#include <lsq.hh>

Public Member Functions | |

| SplitDataRequest (LSQUnit *port, const DynInstPtr &inst, bool isLoad, const Addr &addr, const uint32_t &size, const Request::Flags &flags_, PacketDataPtr data=nullptr, uint64_t *res=nullptr) | |

| virtual | ~SplitDataRequest () |

| virtual void | markAsStaleTranslation () |

| virtual void | finish (const Fault &fault, const RequestPtr &req, gem5::ThreadContext *tc, BaseMMU::Mode mode) |

| virtual bool | recvTimingResp (PacketPtr pkt) |

| virtual void | initiateTranslation () |

| virtual void | sendPacketToCache () |

| virtual void | buildPackets () |

| virtual Cycles | handleLocalAccess (gem5::ThreadContext *thread, PacketPtr pkt) |

| Memory mapped IPR accesses. | |

| virtual bool | isCacheBlockHit (Addr blockAddr, Addr cacheBlockMask) |

| Caches may probe into the load-store queue to enforce memory ordering guarantees. | |

| virtual RequestPtr | mainReq () |

| virtual PacketPtr | mainPacket () |

| virtual std::string | name () const |

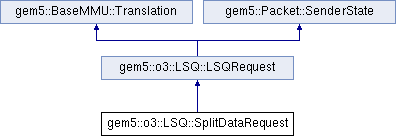

| Public Member Functions inherited from gem5::o3::LSQ::LSQRequest | |

| void | packetSent () |

| Update the status to reflect that a packet was sent. | |

| void | packetNotSent () |

| Update the status to reflect that a packet was not sent. | |

| void | sendFragmentToTranslation (int i) |

| bool | isComplete () |

| bool | isInTranslation () |

| bool | isTranslationComplete () |

| bool | isTranslationBlocked () |

| bool | isSent () |

| bool | isPartialFault () |

| bool | isMemAccessRequired () |

| void | setStateToFault () |

| void | freeLSQEntry () |

| The LSQ entry is cleared. | |

| void | discard () |

| The request is discarded (e.g. | |

| void | packetReplied () |

| void | writebackScheduled () |

| void | writebackDone () |

| void | squashTranslation () |

| void | complete () |

| void | setContext (const ContextID &context_id) |

| Convenience getters/setters. | |

| const DynInstPtr & | instruction () |

| bool | hasStaleTranslation () const |

| void | setVirt (Addr vaddr, unsigned size, Request::Flags flags_, RequestorID requestor_id, Addr pc) |

| Set up virtual request. | |

| ContextID | contextId () const |

| void | taskId (const uint32_t &v) |

| uint32_t | taskId () const |

| RequestPtr | req (int idx=0) |

| const RequestPtr | req (int idx=0) const |

| Addr | getVaddr (int idx=0) const |

| PacketPtr | packet (int idx=0) |

| bool | isAnyOutstandingRequest () |

| Test if there is any in-flight translation or mem access request. | |

| bool | isReleased () |

| Test if the LSQRequest has been released, i.e. | |

| bool | isSplit () const |

| bool | needWBToRegister () const |

| Public Member Functions inherited from gem5::BaseMMU::Translation | |

| virtual | ~Translation () |

| Public Member Functions inherited from gem5::Packet::SenderState | |

| SenderState () | |

| virtual | ~SenderState () |

Protected Attributes | |

| uint32_t | numFragments |

| uint32_t | numReceivedPackets |

| RequestPtr | _mainReq |

| PacketPtr | _mainPacket |

| Protected Attributes inherited from gem5::o3::LSQ::LSQRequest | |

| FlagsType | flags |

| State | _state |

| uint32_t | numTranslatedFragments |

| uint32_t | numInTranslationFragments |

Additional Inherited Members | |

| Public Attributes inherited from gem5::o3::LSQ::LSQRequest | |

| LSQUnit & | _port |

| const DynInstPtr | _inst |

| uint32_t | _taskId |

| PacketDataPtr | _data |

| std::vector< PacketPtr > | _packets |

| std::vector< RequestPtr > | _reqs |

| std::vector< Fault > | _fault |

| uint64_t * | _res |

| const Addr | _addr |

| const uint32_t | _size |

| const Request::Flags | _flags |

| std::vector< bool > | _byteEnable |

| uint32_t | _numOutstandingPackets |

| AtomicOpFunctorPtr | _amo_op |

| bool | _hasStaleTranslation |

| Public Attributes inherited from gem5::Packet::SenderState | |

| SenderState * | predecessor |

| Protected Types inherited from gem5::o3::LSQ::LSQRequest | |

| enum | Flag : FlagsStorage { IsLoad = 0x00000001 , WriteBackToRegister = 0x00000002 , Delayed = 0x00000004 , IsSplit = 0x00000008 , TranslationStarted = 0x00000010 , TranslationFinished = 0x00000020 , Sent = 0x00000040 , Retry = 0x00000080 , Complete = 0x00000100 , TranslationSquashed = 0x00000200 , Discarded = 0x00000400 , LSQEntryFreed = 0x00000800 , WritebackScheduled = 0x00001000 , WritebackDone = 0x00002000 , IsAtomic = 0x00004000 } |

| enum class | State { NotIssued , Translation , Request , Fault , PartialFault } |

| typedef uint32_t | FlagsStorage |

| typedef Flags< FlagsStorage > | FlagsType |

| Protected Member Functions inherited from gem5::o3::LSQ::LSQRequest | |

| void | setState (const State &newState) |

| void | markDelayed () override |

| Signal that the translation has been delayed due to a hw page table walk. | |

| bool | isDelayed () |

| LSQUnit * | lsqUnit () |

| LSQRequest (LSQUnit *port, const DynInstPtr &inst, bool isLoad) | |

| LSQRequest (LSQUnit *port, const DynInstPtr &inst, bool isLoad, const Addr &addr, const uint32_t &size, const Request::Flags &flags_, PacketDataPtr data=nullptr, uint64_t *res=nullptr, AtomicOpFunctorPtr amo_op=nullptr, bool stale_translation=false) | |

| bool | isLoad () const |

| bool | isAtomic () const |

| void | install () |

| Install the request in the LQ/SQ. | |

| bool | squashed () const override |

| This function is used by the page table walker to determine if it should translate the a pending request or if the underlying request has been squashed. | |

| void | release (Flag reason) |

| Release the LSQRequest. | |

| void | addReq (Addr addr, unsigned size, const std::vector< bool > &byte_enable) |

| Helper function used to add a (sub)request, given its address addr, size size and byte-enable mask byteEnable. | |

| virtual | ~LSQRequest () |

| Destructor. | |

Detailed Description

Constructor & Destructor Documentation

◆ SplitDataRequest()

|

inline |

Definition at line 653 of file lsq.hh.

References _mainPacket, _mainReq, gem5::X86ISA::addr, data, gem5::o3::LSQ::LSQRequest::flags, gem5::o3::LSQ::LSQRequest::isLoad(), gem5::o3::LSQ::LSQRequest::IsSplit, gem5::o3::LSQ::LSQRequest::LSQRequest(), numFragments, and numReceivedPackets.

◆ ~SplitDataRequest()

|

inlinevirtual |

Definition at line 666 of file lsq.hh.

References _mainPacket, and _mainReq.

Member Function Documentation

◆ buildPackets()

|

virtual |

Implements gem5::o3::LSQ::LSQRequest.

Definition at line 1231 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_addr, gem5::o3::LSQ::LSQRequest::_fault, gem5::o3::LSQ::LSQRequest::_inst, _mainPacket, _mainReq, gem5::o3::LSQ::LSQRequest::_packets, gem5::o3::LSQ::LSQRequest::_reqs, gem5::Packet::createRead(), gem5::Packet::createWrite(), gem5::Packet::dataDynamic(), gem5::Packet::dataStatic(), DPRINTF, gem5::ArmISA::i, gem5::o3::LSQ::LSQRequest::isLoad(), gem5::NoFault, gem5::ArmISA::offset, gem5::o3::LSQ::LSQRequest::req(), and gem5::Packet::senderState.

◆ finish()

|

virtual |

Implements gem5::BaseMMU::Translation.

Definition at line 876 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_fault, gem5::o3::LSQ::LSQRequest::_inst, _mainReq, gem5::o3::LSQ::LSQRequest::_reqs, gem5::o3::LSQ::LSQRequest::_res, gem5::o3::LSQ::LSQRequest::Fault, gem5::o3::LSQ::LSQRequest::flags, gem5::ArmISA::i, gem5::ArmISA::mode, gem5::NoFault, gem5::o3::LSQ::LSQRequest::numInTranslationFragments, gem5::o3::LSQ::LSQRequest::numTranslatedFragments, gem5::o3::LSQ::LSQRequest::PartialFault, gem5::o3::LSQ::LSQRequest::req(), gem5::o3::LSQ::LSQRequest::Request, gem5::o3::LSQ::LSQRequest::setState(), gem5::o3::LSQ::LSQRequest::squashTranslation(), and gem5::o3::LSQ::LSQRequest::TranslationFinished.

◆ handleLocalAccess()

|

virtual |

Memory mapped IPR accesses.

Implements gem5::o3::LSQ::LSQRequest.

Definition at line 1322 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_reqs, gem5::ArmISA::d, gem5::Packet::dataStatic(), gem5::Packet::getPtr(), gem5::o3::LSQ::LSQRequest::isLoad(), gem5::ArmISA::offset, gem5::MipsISA::r, gem5::MemCmd::ReadReq, gem5::o3::LSQ::thread, and gem5::MemCmd::WriteReq.

◆ initiateTranslation()

|

virtual |

Implements gem5::o3::LSQ::LSQRequest.

Definition at line 957 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_addr, gem5::o3::LSQ::LSQRequest::_byteEnable, gem5::o3::LSQ::LSQRequest::_fault, gem5::o3::LSQ::LSQRequest::_flags, gem5::o3::LSQ::LSQRequest::_inst, _mainReq, gem5::o3::LSQ::LSQRequest::_port, gem5::o3::LSQ::LSQRequest::_reqs, gem5::o3::LSQ::LSQRequest::_size, gem5::o3::LSQ::LSQRequest::_taskId, gem5::addrBlockAlign(), gem5::o3::LSQ::LSQRequest::addReq(), gem5::o3::LSQ::LSQRequest::flags, gem5::ArmISA::i, gem5::o3::LSQ::LSQRequest::numInTranslationFragments, gem5::o3::LSQ::LSQRequest::numTranslatedFragments, gem5::MipsISA::r, gem5::o3::LSQ::LSQRequest::sendFragmentToTranslation(), gem5::o3::LSQ::LSQRequest::setState(), gem5::o3::LSQ::LSQRequest::Translation, and gem5::o3::LSQ::LSQRequest::TranslationStarted.

◆ isCacheBlockHit()

Caches may probe into the load-store queue to enforce memory ordering guarantees.

This method supports probes by providing a mechanism to compare snoop messages with requests tracked by the load-store queue.

Consistency models must enforce ordering constraints. TSO, for instance, must prevent memory reorderings except stores which are reordered after loads. The reordering restrictions negatively impact performance by cutting down on memory level parallelism. However, the core can regain performance by generating speculative loads. Speculative loads may issue without affecting correctness if precautions are taken to handle invalid memory orders. The load queue must squash under memory model violations. Memory model violations may occur when block ownership is granted to another core or the block cannot be accurately monitored by the load queue.

The load-store queue handles partial faults which complicates this method. Physical addresses must be compared between requests and snoops. Some requests will not have a valid physical address, since partial faults may have outstanding translations. Therefore, the existence of a valid request address must be checked before comparing block hits. We assume no pipeline squash is needed if a valid request address does not exist.

Implements gem5::o3::LSQ::LSQRequest.

Definition at line 1363 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_reqs, and gem5::MipsISA::r.

◆ mainPacket()

|

virtual |

Reimplemented from gem5::o3::LSQ::LSQRequest.

Definition at line 945 of file lsq.cc.

References _mainPacket.

◆ mainReq()

|

virtual |

Reimplemented from gem5::o3::LSQ::LSQRequest.

Definition at line 951 of file lsq.cc.

References _mainReq.

◆ markAsStaleTranslation()

|

virtual |

Implements gem5::o3::LSQ::LSQRequest.

Definition at line 1147 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_hasStaleTranslation, gem5::o3::LSQ::LSQRequest::_state, gem5::o3::LSQ::LSQRequest::Complete, gem5::o3::LSQ::LSQRequest::Discarded, DPRINTF, gem5::o3::LSQ::LSQRequest::flags, gem5::o3::LSQ::LSQ(), and gem5::o3::LSQ::LSQRequest::TranslationStarted.

◆ name()

|

inlinevirtual |

Reimplemented from gem5::o3::LSQ::LSQRequest.

◆ recvTimingResp()

|

virtual |

Implements gem5::o3::LSQ::LSQRequest.

Definition at line 1173 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_data, gem5::o3::LSQ::LSQRequest::_hasStaleTranslation, gem5::o3::LSQ::LSQRequest::_inst, _mainReq, gem5::o3::LSQ::LSQRequest::_packets, gem5::o3::LSQ::LSQRequest::_port, gem5::o3::LSQ::LSQRequest::Complete, gem5::Packet::createRead(), gem5::Packet::createWrite(), gem5::Packet::dataStatic(), gem5::o3::LSQ::LSQRequest::flags, gem5::o3::LSQ::LSQRequest::isLoad(), numReceivedPackets, and gem5::Packet::senderState.

◆ sendPacketToCache()

|

virtual |

Implements gem5::o3::LSQ::LSQRequest.

Definition at line 1304 of file lsq.cc.

References gem5::o3::LSQ::LSQRequest::_numOutstandingPackets, gem5::o3::LSQ::LSQRequest::_packets, gem5::o3::LSQ::LSQRequest::isLoad(), gem5::o3::LSQ::LSQRequest::lsqUnit(), and numReceivedPackets.

Member Data Documentation

◆ _mainPacket

|

protected |

Definition at line 650 of file lsq.hh.

Referenced by buildPackets(), mainPacket(), SplitDataRequest(), and ~SplitDataRequest().

◆ _mainReq

|

protected |

Definition at line 649 of file lsq.hh.

Referenced by buildPackets(), finish(), initiateTranslation(), mainReq(), recvTimingResp(), SplitDataRequest(), and ~SplitDataRequest().

◆ numFragments

|

protected |

Definition at line 647 of file lsq.hh.

Referenced by SplitDataRequest().

◆ numReceivedPackets

|

protected |

Definition at line 648 of file lsq.hh.

Referenced by recvTimingResp(), sendPacketToCache(), and SplitDataRequest().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:07:00 for gem5 by doxygen 1.14.0