#include <mmu.hh>

Classes | |

| class | MMUTranslationGen |

| class | Translation |

Public Types | |

| enum | Mode { Read , Write , Execute } |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| void | init () override |

| Called at init time, this method is traversing the TLB hierarchy and pupulating the instruction/data/unified containers accordingly. | |

| virtual void | flushAll () |

| virtual void | reset () |

| void | demapPage (Addr vaddr, uint64_t asn) |

| virtual Fault | translateAtomic (const RequestPtr &req, ThreadContext *tc, Mode mode) |

| virtual void | translateTiming (const RequestPtr &req, ThreadContext *tc, Translation *translation, Mode mode) |

| virtual Fault | translateFunctional (const RequestPtr &req, ThreadContext *tc, Mode mode) |

| virtual Addr | getValidAddr (Addr vaddr, ThreadContext *tc, Mode mode) |

| virtual TranslationGenPtr | translateFunctional (Addr start, Addr size, ThreadContext *tc, BaseMMU::Mode mode, Request::Flags flags)=0 |

| Returns a translation generator for a region of virtual addresses, instead of directly translating a specific address. | |

| virtual Fault | finalizePhysical (const RequestPtr &req, ThreadContext *tc, Mode mode) const |

| virtual void | takeOverFrom (BaseMMU *old_mmu) |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Public Attributes | |

| BaseTLB * | dtb |

| BaseTLB * | itb |

Protected Types | |

| typedef BaseMMUParams | Params |

Protected Member Functions | |

| BaseMMU (const Params &p) | |

| BaseTLB * | getTlb (Mode mode) const |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

Protected Attributes | |

| std::set< BaseTLB * > | instruction |

| It is possible from the MMU to traverse the entire hierarchy of TLBs, starting from the DTB and ITB (generally speaking from the first level) up to the last level via the nextLevel pointer. | |

| std::set< BaseTLB * > | data |

| std::set< BaseTLB * > | unified |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

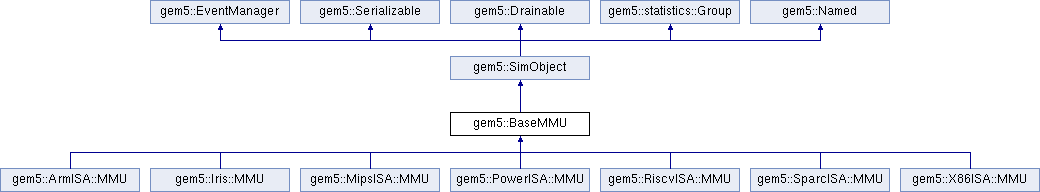

Detailed Description

Member Typedef Documentation

◆ Params

|

protected |

Member Enumeration Documentation

◆ Mode

| enum gem5::BaseMMU::Mode |

Constructor & Destructor Documentation

◆ BaseMMU()

|

inlineprotected |

Definition at line 90 of file mmu.hh.

References dtb, itb, gem5::MipsISA::p, and gem5::SimObject::SimObject().

Referenced by gem5::ArmISA::MMU::MMU(), gem5::Iris::MMU::MMU(), gem5::MipsISA::MMU::MMU(), gem5::PowerISA::MMU::MMU(), gem5::RiscvISA::MMU::MMU(), gem5::SparcISA::MMU::MMU(), gem5::X86ISA::MMU::MMU(), gem5::BaseMMU::MMUTranslationGen::MMUTranslationGen(), gem5::ArmISA::MMU::takeOverFrom(), takeOverFrom(), gem5::RiscvISA::MMU::takeOverFrom(), translateFunctional(), and gem5::ArmISA::MMU::translateTiming().

Member Function Documentation

◆ demapPage()

| void gem5::BaseMMU::demapPage | ( | Addr | vaddr, |

| uint64_t | asn ) |

Definition at line 104 of file mmu.cc.

References dtb, itb, and gem5::MipsISA::vaddr.

Referenced by gem5::X86ISA::PageFault::invoke().

◆ finalizePhysical()

|

virtual |

Reimplemented in gem5::ArmISA::MMU.

Definition at line 138 of file mmu.cc.

References gem5::BaseTLB::finalizePhysical(), getTlb(), and gem5::ArmISA::mode.

◆ flushAll()

|

virtual |

Reimplemented in gem5::ArmISA::MMU.

Definition at line 81 of file mmu.cc.

References data, instruction, gem5::ArmISA::tlb, and unified.

Referenced by gem5::X86ISA::copyMiscRegs(), gem5::ArmISA::MMU::flushAll(), gem5::BaseCPU::flushTLBs(), gem5::GPUComputeDriver::ioctl(), and reset().

◆ getTlb()

Definition at line 95 of file mmu.hh.

References dtb, Execute, itb, and gem5::ArmISA::mode.

Referenced by finalizePhysical(), translateAtomic(), translateFunctional(), and translateTiming().

◆ getValidAddr()

|

virtual |

Reimplemented in gem5::ArmISA::MMU, and gem5::RiscvISA::MMU.

Definition at line 132 of file mmu.cc.

References gem5::ArmISA::mode, and gem5::MipsISA::vaddr.

◆ init()

|

overridevirtual |

Called at init time, this method is traversing the TLB hierarchy and pupulating the instruction/data/unified containers accordingly.

Reimplemented from gem5::SimObject.

Reimplemented in gem5::ArmISA::MMU.

Definition at line 53 of file mmu.cc.

References data, dtb, instruction, itb, panic, gem5::ArmISA::tlb, and unified.

Referenced by gem5::ArmISA::MMU::init().

◆ reset()

|

virtual |

◆ takeOverFrom()

|

virtual |

Reimplemented in gem5::ArmISA::MMU, and gem5::RiscvISA::MMU.

Definition at line 172 of file mmu.cc.

References BaseMMU(), dtb, gem5::BaseTLB::getTableWalkerPort(), itb, and gem5::Port::takeOverFrom().

Referenced by gem5::ArmISA::MMU::takeOverFrom(), gem5::BaseCPU::takeOverFrom(), and gem5::RiscvISA::MMU::takeOverFrom().

◆ translateAtomic()

|

virtual |

Reimplemented in gem5::ArmISA::MMU.

Definition at line 111 of file mmu.cc.

References getTlb(), gem5::ArmISA::mode, and gem5::BaseTLB::translateAtomic().

Referenced by gem5::AtomicSimpleCPU::amoMem(), gem5::BaseCPU::mwaitAtomic(), gem5::AtomicSimpleCPU::readMem(), gem5::AtomicSimpleCPU::tick(), and gem5::AtomicSimpleCPU::writeMem().

◆ translateFunctional() [1/2]

|

pure virtual |

Returns a translation generator for a region of virtual addresses, instead of directly translating a specific address.

Implemented in gem5::ArmISA::MMU, gem5::MipsISA::MMU, gem5::PowerISA::MMU, gem5::RiscvISA::MMU, gem5::SparcISA::MMU, and gem5::X86ISA::MMU.

References BaseMMU(), and gem5::ArmISA::mode.

◆ translateFunctional() [2/2]

|

virtual |

Reimplemented in gem5::ArmISA::MMU.

Definition at line 125 of file mmu.cc.

References getTlb(), gem5::ArmISA::mode, and gem5::BaseTLB::translateFunctional().

Referenced by gem5::tryTranslate().

◆ translateTiming()

|

virtual |

Reimplemented in gem5::ArmISA::MMU.

Definition at line 118 of file mmu.cc.

References getTlb(), gem5::ArmISA::mode, and gem5::BaseTLB::translateTiming().

Referenced by gem5::TimingSimpleCPU::fetch(), gem5::TimingSimpleCPU::initiateMemAMO(), gem5::TimingSimpleCPU::initiateMemRead(), gem5::minor::LSQ::SplitDataRequest::sendNextFragmentToTranslation(), gem5::minor::LSQ::SingleDataRequest::startAddrTranslation(), and gem5::TimingSimpleCPU::writeMem().

Member Data Documentation

◆ data

|

protected |

Definition at line 186 of file mmu.hh.

Referenced by gem5::ArmISA::MMU::checkWalkCache(), gem5::ArmISA::MMU::dflush(), flushAll(), gem5::ArmISA::MMU::flushStage1(), init(), and gem5::ArmISA::MMU::updateMiscReg().

◆ dtb

| BaseTLB* gem5::BaseMMU::dtb |

Definition at line 162 of file mmu.hh.

Referenced by BaseMMU(), demapPage(), gem5::X86ISA::MMU::flushNonGlobal(), gem5::RiscvISA::MMU::getDataWalker(), gem5::X86ISA::MMU::getDataWalker(), gem5::ArmISA::MMU::getDTBPtr(), gem5::RiscvISA::MMU::getMemAccessInfo(), gem5::RiscvISA::MMU::getPMP(), getTlb(), gem5::RiscvISA::MMU::getValidAddr(), init(), gem5::SparcISA::MMU::insertDtlbEntry(), and takeOverFrom().

◆ instruction

|

protected |

It is possible from the MMU to traverse the entire hierarchy of TLBs, starting from the DTB and ITB (generally speaking from the first level) up to the last level via the nextLevel pointer.

So in theory no extra data should be stored in the BaseMMU.

This design makes some operations a bit more complex. For example if we have a unified (I+D) L2, it will be pointed by both ITB and DTB. If we want to invalidate all TLB entries, we should be careful to not invalidate L2 twice, but if we simply follow the next level pointer, we might do so. This is not a problem from a functional perspective but alters the TLB statistics (a single invalidation is recorded twice)

We then provide a different view of the set of TLBs in the system. At the init phase we traverse the TLB hierarchy and we add every TLB to the appropriate set. This makes invalidation (and any operation targeting a specific kind of TLBs) easier.

Definition at line 185 of file mmu.hh.

Referenced by gem5::ArmISA::MMU::checkWalkCache(), flushAll(), gem5::ArmISA::MMU::flushStage1(), gem5::ArmISA::MMU::iflush(), init(), and gem5::ArmISA::MMU::updateMiscReg().

◆ itb

| BaseTLB* gem5::BaseMMU::itb |

Definition at line 163 of file mmu.hh.

Referenced by BaseMMU(), demapPage(), gem5::X86ISA::MMU::flushNonGlobal(), gem5::ArmISA::MMU::getITBPtr(), getTlb(), gem5::RiscvISA::MMU::getValidAddr(), init(), gem5::SparcISA::MMU::insertItlbEntry(), and takeOverFrom().

◆ unified

|

protected |

Definition at line 187 of file mmu.hh.

Referenced by gem5::ArmISA::MMU::checkWalkCache(), gem5::ArmISA::MMU::dflush(), flushAll(), gem5::ArmISA::MMU::flushStage1(), gem5::ArmISA::MMU::iflush(), init(), and gem5::ArmISA::MMU::updateMiscReg().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:49 for gem5 by doxygen 1.14.0