#include <gic_v3_cpu_interface.hh>

Classes | |

| struct | hppi_t |

Public Member Functions | |

| Gicv3CPUInterface (Gicv3 *gic, uint32_t cpu_id) | |

| void | init () |

| RegVal | readMiscReg (int misc_reg) override |

| Read a system register belonging to this device. More... | |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Write to a system register belonging to this device. More... | |

| void | setThreadContext (ThreadContext *tc) override |

Public Member Functions inherited from ArmISA::BaseISADevice Public Member Functions inherited from ArmISA::BaseISADevice | |

| BaseISADevice () | |

| virtual | ~BaseISADevice () |

| virtual void | setISA (ISA *isa) |

Public Member Functions inherited from Serializable Public Member Functions inherited from Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. More... | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. More... | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Protected Types | |

| enum | { GICC_CTLR = 0x0000, GICC_PMR = 0x0004, GICC_BPR = 0x0008, GICC_IAR = 0x000C, GICC_EOIR = 0x0010, GICC_RPR = 0x0014, GICC_HPPI = 0x0018, GICC_ABPR = 0x001C, GICC_AIAR = 0x0020, GICC_AEOIR = 0x0024, GICC_AHPPIR = 0x0028, GICC_STATUSR = 0x002C, GICC_IIDR = 0x00FC } |

| enum | { GICH_HCR = 0x0000, GICH_VTR = 0x0004, GICH_VMCR = 0x0008, GICH_MISR = 0x0010, GICH_EISR = 0x0020, GICH_ELRSR = 0x0030 } |

Protected Member Functions | |

| BitUnion64 (ICC_CTLR_EL1) Bitfield< 63 | |

| EndBitUnion (ICC_CTLR_EL1) BitUnion64(ICC_CTLR_EL3) Bitfield< 63 | |

| EndBitUnion (ICC_CTLR_EL3) BitUnion64(ICC_IGRPEN0_EL1) Bitfield< 63 | |

| EndBitUnion (ICC_IGRPEN0_EL1) BitUnion64(ICC_IGRPEN1_EL1) Bitfield< 63 | |

| EndBitUnion (ICC_IGRPEN1_EL1) BitUnion64(ICC_IGRPEN1_EL3) Bitfield< 63 | |

| EndBitUnion (ICC_IGRPEN1_EL3) BitUnion64(ICC_SRE_EL1) Bitfield< 63 | |

| EndBitUnion (ICC_SRE_EL1) BitUnion64(ICC_SRE_EL2) Bitfield< 63 | |

| EndBitUnion (ICC_SRE_EL2) BitUnion64(ICC_SRE_EL3) Bitfield< 63 | |

| EndBitUnion (ICC_SRE_EL3) static const uint8_t PRIORITY_BITS | |

| BitUnion64 (ICH_HCR_EL2) Bitfield< 63 | |

| EndBitUnion (ICH_HCR_EL2) BitUnion64(ICH_LR_EL2) Bitfield< 63 | |

| EndBitUnion (ICH_LR_EL2) static const uint64_t ICH_LR_EL2_STATE_INVALID=0 | |

| BitUnion32 (ICH_LRC) Bitfield< 31 | |

| EndBitUnion (ICH_LRC) BitUnion64(ICH_MISR_EL2) Bitfield< 63 | |

| EndBitUnion (ICH_MISR_EL2) BitUnion64(ICH_VMCR_EL2) Bitfield< 63 | |

| EndBitUnion (ICH_VMCR_EL2) BitUnion64(ICH_VTR_EL2) Bitfield< 63 | |

| EndBitUnion (ICH_VTR_EL2) BitUnion64(ICV_CTLR_EL1) Bitfield< 63 | |

| EndBitUnion(ICV_CTLR_EL1) protected void | generateSGI (RegVal val, Gicv3::GroupId group) |

| int | currEL () const |

| void | deactivateIRQ (uint32_t intid, Gicv3::GroupId group) |

| void | dropPriority (Gicv3::GroupId group) |

| uint64_t | eoiMaintenanceInterruptStatus () const |

| bool | getHCREL2FMO () const |

| bool | getHCREL2IMO () const |

| uint32_t | getHPPIR0 () const |

| uint32_t | getHPPIR1 () const |

| int | getHPPVILR () const |

| bool | groupEnabled (Gicv3::GroupId group) const |

| uint32_t | groupPriorityMask (Gicv3::GroupId group) |

| bool | haveEL (ArmISA::ExceptionLevel el) const |

| int | highestActiveGroup () const |

| uint8_t | highestActivePriority () const |

| bool | hppiCanPreempt () |

| bool | hppviCanPreempt (int lrIdx) const |

| bool | inSecureState () const |

| ArmISA::InterruptTypes | intSignalType (Gicv3::GroupId group) const |

| bool | isAA64 () const |

| bool | isEL3OrMon () const |

| bool | isEOISplitMode () const |

| bool | isSecureBelowEL3 () const |

| ICH_MISR_EL2 | maintenanceInterruptStatus () const |

| void | resetHppi (uint32_t intid) |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. More... | |

| void | update () |

| void | updateDistributor () |

| void | virtualActivateIRQ (uint32_t lrIdx) |

| void | virtualDeactivateIRQ (int lrIdx) |

| uint8_t | virtualDropPriority () |

| int | virtualFindActive (uint32_t intid) const |

| uint32_t | virtualGroupPriorityMask (Gicv3::GroupId group) const |

| uint8_t | virtualHighestActivePriority () const |

| void | virtualIncrementEOICount () |

| bool | virtualIsEOISplitMode () const |

| void | virtualUpdate () |

| RegVal | bpr1 (Gicv3::GroupId group) |

| bool | havePendingInterrupts (void) const |

| void | clearPendingInterrupts (void) |

| void | assertWakeRequest (void) |

| void | deassertWakeRequest (void) |

| RegVal | readBankedMiscReg (ArmISA::MiscRegIndex misc_reg) const |

| void | setBankedMiscReg (ArmISA::MiscRegIndex misc_reg, RegVal val) const |

Protected Attributes | |

| Gicv3 * | gic |

| Gicv3Redistributor * | redistributor |

| Gicv3Distributor * | distributor |

| uint32_t | cpuId |

| ArmInterruptPin * | maintenanceInterrupt |

| res0_3 | |

| Bitfield< 19 > | ExtRange |

| Bitfield< 18 > | RSS |

| Bitfield< 17, 16 > | res0_2 |

| Bitfield< 15 > | A3V |

| Bitfield< 14 > | SEIS |

| Bitfield< 13, 11 > | IDbits |

| Bitfield< 10, 8 > | PRIbits |

| Bitfield< 7 > | res0_1 |

| Bitfield< 6 > | PMHE |

| Bitfield< 5, 2 > | res0_0 |

| Bitfield< 1 > | EOImode |

| Bitfield< 0 > | CBPR |

| res0_2 | |

| Bitfield< 17 > | nDS |

| Bitfield< 16 > | res0_1 |

| Bitfield< 7 > | res0_0 |

| Bitfield< 5 > | RM |

| Bitfield< 4 > | EOImode_EL1NS |

| Bitfield< 3 > | EOImode_EL1S |

| Bitfield< 2 > | EOImode_EL3 |

| Bitfield< 1 > | CBPR_EL1NS |

| Bitfield< 0 > | CBPR_EL1S |

| res0 | |

| Bitfield< 0 > | Enable |

| Bitfield< 1 > | EnableGrp1S |

| Bitfield< 0 > | EnableGrp1NS |

| Bitfield< 2 > | DIB |

| Bitfield< 1 > | DFB |

| Bitfield< 0 > | SRE |

| Bitfield< 3 > | Enable |

| hppi_t | hppi |

| Bitfield< 31, 27 > | EOIcount |

| Bitfield< 26, 15 > | res0_1 |

| Bitfield< 14 > | TDIR |

| Bitfield< 13 > | TSEI |

| Bitfield< 12 > | TALL1 |

| Bitfield< 11 > | TALL0 |

| Bitfield< 10 > | TC |

| Bitfield< 9, 8 > | res0_0 |

| Bitfield< 7 > | VGrp1DIE |

| Bitfield< 6 > | VGrp1EIE |

| Bitfield< 5 > | VGrp0DIE |

| Bitfield< 4 > | VGrp0EIE |

| Bitfield< 3 > | NPIE |

| Bitfield< 2 > | LRENPIE |

| Bitfield< 1 > | UIE |

| Bitfield< 0 > | En |

| State | |

| Bitfield< 61 > | HW |

| Bitfield< 60 > | Group |

| Bitfield< 59, 56 > | res0_1 |

| Bitfield< 55, 48 > | Priority |

| Bitfield< 47, 45 > | res0_0 |

| Bitfield< 44, 32 > | pINTID |

| Bitfield< 41 > | EOI |

| Bitfield< 31, 0 > | vINTID |

| Bitfield< 29 > | HW |

| Bitfield< 28 > | Group |

| Bitfield< 27, 24 > | res0_1 |

| Bitfield< 23, 16 > | Priority |

| Bitfield< 15, 13 > | res0_0 |

| Bitfield< 12, 0 > | pINTID |

| Bitfield< 9 > | EOI |

| Bitfield< 7 > | VGrp1D |

| Bitfield< 6 > | VGrp1E |

| Bitfield< 5 > | VGrp0D |

| Bitfield< 4 > | VGrp0E |

| Bitfield< 3 > | NP |

| Bitfield< 2 > | LRENP |

| Bitfield< 1 > | U |

| Bitfield< 0 > | EOI |

| Bitfield< 31, 24 > | VPMR |

| Bitfield< 23, 21 > | VBPR0 |

| Bitfield< 20, 18 > | VBPR1 |

| Bitfield< 17, 10 > | res0_1 |

| Bitfield< 9 > | VEOIM |

| Bitfield< 8, 5 > | res0_0 |

| Bitfield< 4 > | VCBPR |

| Bitfield< 3 > | VFIQEn |

| Bitfield< 2 > | VAckCtl |

| Bitfield< 1 > | VENG1 |

| Bitfield< 0 > | VENG0 |

| res0_1 | |

| Bitfield< 31, 29 > | PRIbits |

| Bitfield< 28, 26 > | PREbits |

| Bitfield< 25, 23 > | IDbits |

| Bitfield< 22 > | SEIS |

| Bitfield< 21 > | A3V |

| Bitfield< 20 > | res1 |

| Bitfield< 19 > | TDS |

| Bitfield< 18, 5 > | res0_0 |

| Bitfield< 4, 0 > | ListRegs |

| Bitfield< 17, 16 > | res0_1 |

| Bitfield< 7, 2 > | res0_0 |

Protected Attributes inherited from ArmISA::BaseISADevice Protected Attributes inherited from ArmISA::BaseISADevice | |

| ISA * | isa |

Static Protected Attributes | |

| static const uint8_t | GIC_MIN_BPR = 2 |

| static const uint8_t | GIC_MIN_BPR_NS = GIC_MIN_BPR + 1 |

| static const uint8_t | VIRTUAL_PRIORITY_BITS = 5 |

| static const uint8_t | VIRTUAL_PREEMPTION_BITS = 5 |

| static const uint8_t | VIRTUAL_NUM_LIST_REGS = 16 |

| static const uint8_t | GIC_MIN_VBPR = 7 - VIRTUAL_PREEMPTION_BITS |

| static const AddrRange | GICC_APR |

| static const AddrRange | GICC_NSAPR |

| static const AddrRange | GICH_APR |

| static const AddrRange | GICH_LR |

| static const uint64_t | ICH_LR_EL2_STATE_PENDING = 1 |

| static const uint64_t | ICH_LR_EL2_STATE_ACTIVE = 2 |

| static const uint64_t | ICH_LR_EL2_STATE_ACTIVE_PENDING = 3 |

Friends | |

| class | Gicv3Distributor |

| class | Gicv3Redistributor |

Additional Inherited Members | |

Static Public Member Functions inherited from Serializable Static Public Member Functions inherited from Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. More... | |

| static void | serializeAll (const std::string &cpt_dir) |

| Serializes all the SimObjects. More... | |

| static void | unserializeGlobals (CheckpointIn &cp) |

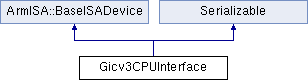

Detailed Description

Definition at line 50 of file gic_v3_cpu_interface.hh.

Member Enumeration Documentation

◆ anonymous enum

|

protected |

| Enumerator | |

|---|---|

| GICC_CTLR | |

| GICC_PMR | |

| GICC_BPR | |

| GICC_IAR | |

| GICC_EOIR | |

| GICC_RPR | |

| GICC_HPPI | |

| GICC_ABPR | |

| GICC_AIAR | |

| GICC_AEOIR | |

| GICC_AHPPIR | |

| GICC_STATUSR | |

| GICC_IIDR | |

Definition at line 163 of file gic_v3_cpu_interface.hh.

◆ anonymous enum

|

protected |

| Enumerator | |

|---|---|

| GICH_HCR | |

| GICH_VTR | |

| GICH_VMCR | |

| GICH_MISR | |

| GICH_EISR | |

| GICH_ELRSR | |

Definition at line 183 of file gic_v3_cpu_interface.hh.

Constructor & Destructor Documentation

◆ Gicv3CPUInterface()

| Gicv3CPUInterface::Gicv3CPUInterface | ( | Gicv3 * | gic, |

| uint32_t | cpu_id | ||

| ) |

Definition at line 55 of file gic_v3_cpu_interface.cc.

References hppi, Gicv3CPUInterface::hppi_t::intid, Gicv3::INTID_SPURIOUS, and Gicv3CPUInterface::hppi_t::prio.

Member Function Documentation

◆ assertWakeRequest()

|

protected |

Definition at line 2595 of file gic_v3_cpu_interface.cc.

References ArmSystem::callSetWakeRequest(), cpuId, BaseGic::getSystem(), gic, Ps2::Reset, and System::threads.

Referenced by Gicv3Redistributor::update().

◆ BitUnion32()

|

protected |

◆ BitUnion64() [1/2]

|

protected |

◆ BitUnion64() [2/2]

|

protected |

◆ bpr1()

|

protected |

Definition at line 2541 of file gic_v3_cpu_interface.cc.

References currEL(), ArmISA::EL1, ArmISA::EL3, Gicv3::G1NS, Gicv3::G1S, getHCREL2IMO(), GIC_MIN_BPR, GIC_MIN_BPR_NS, haveEL(), inSecureState(), ArmISA::BaseISADevice::isa, isEL3OrMon(), ArmISA::MISCREG_ICC_BPR0_EL1, ArmISA::MISCREG_ICC_BPR1_EL1_NS, ArmISA::MISCREG_ICC_BPR1_EL1_S, ArmISA::MISCREG_ICC_CTLR_EL1_NS, ArmISA::MISCREG_ICC_CTLR_EL1_S, ArmISA::MISCREG_ICV_BPR1_EL1, panic, readMiscReg(), and ArmISA::ISA::readMiscRegNoEffect().

Referenced by groupPriorityMask(), and readMiscReg().

◆ clearPendingInterrupts()

|

protected |

Definition at line 2588 of file gic_v3_cpu_interface.cc.

References cpuId, Gicv3::deassertAll(), gic, hppi, Gicv3CPUInterface::hppi_t::intid, and resetHppi().

Referenced by Gicv3Redistributor::update().

◆ currEL()

|

protected |

Definition at line 2343 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, ArmISA::MISCREG_CPSR, ArmISA::MODE_HYP, ArmISA::MODE_MON, ArmISA::MODE_USER, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by bpr1(), getHPPIR1(), intSignalType(), readMiscReg(), and setMiscReg().

◆ deactivateIRQ()

|

protected |

Definition at line 1882 of file gic_v3_cpu_interface.cc.

References Gicv3Distributor::deactivateIRQ(), Gicv3Redistributor::deactivateIRQ(), distributor, Gicv3::INTID_SECURE, Gicv3::PPI_MAX, redistributor, Gicv3::SGI_MAX, and updateDistributor().

Referenced by setMiscReg(), and virtualDeactivateIRQ().

◆ deassertWakeRequest()

|

protected |

Definition at line 2605 of file gic_v3_cpu_interface.cc.

References ArmSystem::callClearWakeRequest(), cpuId, BaseGic::getSystem(), gic, and System::threads.

Referenced by Gicv3Redistributor::write().

◆ dropPriority()

|

protected |

Definition at line 1712 of file gic_v3_cpu_interface.cc.

References Gicv3::G0S, Gicv3::G1NS, Gicv3::G1S, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICC_AP0R0_EL1, ArmISA::MISCREG_ICC_AP1R0_EL1_NS, ArmISA::MISCREG_ICC_AP1R0_EL1_S, panic, ArmISA::ISA::readMiscRegNoEffect(), ArmISA::ISA::setMiscRegNoEffect(), and update().

Referenced by setMiscReg().

◆ EndBitUnion() [1/14]

|

protected |

◆ EndBitUnion() [2/14]

|

protected |

◆ EndBitUnion() [3/14]

|

protected |

◆ EndBitUnion() [4/14]

|

protected |

◆ EndBitUnion() [5/14]

|

protected |

◆ EndBitUnion() [6/14]

|

protected |

◆ EndBitUnion() [7/14]

|

protected |

◆ EndBitUnion() [8/14]

|

protected |

◆ EndBitUnion() [9/14]

|

protected |

◆ EndBitUnion() [10/14]

|

protectedpure virtual |

◆ EndBitUnion() [11/14]

|

protected |

◆ EndBitUnion() [12/14]

|

protected |

◆ EndBitUnion() [13/14]

|

protected |

◆ EndBitUnion() [14/14]

|

protected |

◆ eoiMaintenanceInterruptStatus()

|

protected |

Definition at line 2420 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::ISA::readMiscRegNoEffect(), and VIRTUAL_NUM_LIST_REGS.

Referenced by maintenanceInterruptStatus(), and readMiscReg().

◆ generateSGI()

|

protected |

Definition at line 1771 of file gic_v3_cpu_interface.cc.

References bits(), Gicv3Redistributor::getAffinity(), Gicv3::getRedistributor(), BaseGic::getSystem(), gic, ArmISA::i, inSecureState(), ArmISA::ns, redistributor, ArmISA::rs, Gicv3Redistributor::sendSGI(), and X86ISA::val.

Referenced by setMiscReg().

◆ getHCREL2FMO()

|

protected |

Definition at line 89 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, ArmISA::MISCREG_HCR_EL2, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by readMiscReg(), and setMiscReg().

◆ getHCREL2IMO()

|

protected |

Definition at line 103 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, ArmISA::MISCREG_HCR_EL2, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by bpr1(), readMiscReg(), and setMiscReg().

◆ getHPPIR0()

|

protected |

Definition at line 1651 of file gic_v3_cpu_interface.cc.

References distributor, Gicv3Distributor::DS, Gicv3::G0S, Gicv3::G1NS, Gicv3CPUInterface::hppi_t::group, groupEnabled(), hppi, inSecureState(), Gicv3CPUInterface::hppi_t::intid, Gicv3::INTID_NONSECURE, Gicv3::INTID_SECURE, Gicv3::INTID_SPURIOUS, isEL3OrMon(), and Gicv3CPUInterface::hppi_t::prio.

Referenced by readMiscReg().

◆ getHPPIR1()

|

protected |

Definition at line 1677 of file gic_v3_cpu_interface.cc.

References currEL(), distributor, Gicv3Distributor::DS, ArmISA::EL3, Gicv3::G0S, Gicv3::G1NS, Gicv3CPUInterface::hppi_t::group, groupEnabled(), hppi, inSecureState(), Gicv3CPUInterface::hppi_t::intid, Gicv3::INTID_NONSECURE, Gicv3::INTID_SECURE, Gicv3::INTID_SPURIOUS, ArmISA::BaseISADevice::isa, isEL3OrMon(), ArmISA::MISCREG_ICC_CTLR_EL3, Gicv3CPUInterface::hppi_t::prio, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by readMiscReg().

◆ getHPPVILR()

|

protected |

Definition at line 2113 of file gic_v3_cpu_interface.cc.

References ArmISA::i, Gicv3::INT_PENDING, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::MISCREG_ICH_VMCR_EL2, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by readMiscReg(), and virtualUpdate().

◆ groupEnabled()

|

protected |

Definition at line 2304 of file gic_v3_cpu_interface.cc.

References distributor, Gicv3Distributor::EnableGrp0, Gicv3Distributor::EnableGrp1NS, Gicv3Distributor::EnableGrp1S, Gicv3::G0S, Gicv3::G1NS, Gicv3::G1S, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICC_IGRPEN0_EL1, ArmISA::MISCREG_ICC_IGRPEN1_EL1_NS, ArmISA::MISCREG_ICC_IGRPEN1_EL1_S, panic, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by getHPPIR0(), getHPPIR1(), and hppiCanPreempt().

◆ groupPriorityMask()

|

protected |

Definition at line 1921 of file gic_v3_cpu_interface.cc.

References bpr1(), Gicv3::G0S, Gicv3::G1NS, Gicv3::G1S, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICC_BPR0_EL1, ArmISA::MISCREG_ICC_CTLR_EL1_NS, ArmISA::MISCREG_ICC_CTLR_EL1_S, readMiscReg(), ArmISA::ISA::readMiscRegNoEffect(), and U.

Referenced by hppiCanPreempt().

◆ haveEL()

|

protected |

Definition at line 2368 of file gic_v3_cpu_interface.cc.

References ArmISA::el, ArmISA::EL0, ArmISA::EL1, ArmISA::EL2, ArmISA::EL3, BaseGic::getSystem(), gic, ArmSystem::haveSecurity(), ArmSystem::haveVirtualization(), and warn.

Referenced by bpr1(), isEL3OrMon(), isSecureBelowEL3(), readMiscReg(), setMiscReg(), and update().

◆ havePendingInterrupts()

|

protected |

Definition at line 2582 of file gic_v3_cpu_interface.cc.

References cpuId, gic, Gicv3::haveAsserted(), hppi, and Gicv3CPUInterface::hppi_t::prio.

Referenced by Gicv3Redistributor::update().

◆ highestActiveGroup()

|

protected |

Definition at line 2002 of file gic_v3_cpu_interface.cc.

References ctz32(), Gicv3::G0S, Gicv3::G1NS, Gicv3::G1S, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICC_AP0R0_EL1, ArmISA::MISCREG_ICC_AP1R0_EL1_NS, ArmISA::MISCREG_ICC_AP1R0_EL1_S, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by setMiscReg().

◆ highestActivePriority()

|

protected |

Definition at line 2289 of file gic_v3_cpu_interface.cc.

References ctz32(), GIC_MIN_BPR, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICC_AP0R0_EL1, ArmISA::MISCREG_ICC_AP1R0_EL1_NS, ArmISA::MISCREG_ICC_AP1R0_EL1_S, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by hppiCanPreempt(), and readMiscReg().

◆ hppiCanPreempt()

|

protected |

Definition at line 2256 of file gic_v3_cpu_interface.cc.

References Gicv3CPUInterface::hppi_t::group, groupEnabled(), groupPriorityMask(), highestActivePriority(), hppi, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICC_PMR_EL1, Gicv3CPUInterface::hppi_t::prio, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by readMiscReg(), and update().

◆ hppviCanPreempt()

|

protected |

Definition at line 2157 of file gic_v3_cpu_interface.cc.

References bits(), Gicv3::G0S, Gicv3::G1NS, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_HCR_EL2, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::MISCREG_ICH_VMCR_EL2, ArmISA::ISA::readMiscRegNoEffect(), virtualGroupPriorityMask(), and virtualHighestActivePriority().

Referenced by readMiscReg(), and virtualUpdate().

◆ init()

| void Gicv3CPUInterface::init | ( | ) |

Definition at line 67 of file gic_v3_cpu_interface.cc.

References cpuId, distributor, Gicv3::getDistributor(), Gicv3::getRedistributor(), gic, and redistributor.

◆ inSecureState()

|

protected |

Definition at line 2331 of file gic_v3_cpu_interface.cc.

References BaseGic::getSystem(), gic, ArmSystem::haveSecurity(), ArmISA::inSecureState(), ArmISA::BaseISADevice::isa, ArmISA::MISCREG_CPSR, ArmISA::MISCREG_SCR, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by bpr1(), generateSGI(), getHPPIR0(), getHPPIR1(), intSignalType(), isEOISplitMode(), readMiscReg(), and setMiscReg().

◆ intSignalType()

|

protected |

Definition at line 2226 of file gic_v3_cpu_interface.cc.

References currEL(), distributor, Gicv3Distributor::DS, ArmISA::EL3, Gicv3::G0S, Gicv3::G1NS, Gicv3::G1S, inSecureState(), ArmISA::INT_FIQ, ArmISA::INT_IRQ, isAA64(), and panic.

Referenced by update().

◆ isAA64()

|

protected |

Definition at line 2395 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, ArmISA::MISCREG_CPSR, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by intSignalType().

◆ isEL3OrMon()

|

protected |

Definition at line 2402 of file gic_v3_cpu_interface.cc.

References ArmISA::EL3, haveEL(), ArmISA::BaseISADevice::isa, ArmISA::MISCREG_CPSR, ArmISA::MODE_MON, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by bpr1(), getHPPIR0(), getHPPIR1(), isEOISplitMode(), and setMiscReg().

◆ isEOISplitMode()

|

protected |

Definition at line 1978 of file gic_v3_cpu_interface.cc.

References inSecureState(), ArmISA::BaseISADevice::isa, isEL3OrMon(), ArmISA::MISCREG_ICC_CTLR_EL1_NS, ArmISA::MISCREG_ICC_CTLR_EL1_S, ArmISA::MISCREG_ICC_CTLR_EL3, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by setMiscReg().

◆ isSecureBelowEL3()

|

protected |

Definition at line 2388 of file gic_v3_cpu_interface.cc.

References ArmISA::EL3, haveEL(), ArmISA::BaseISADevice::isa, ArmISA::MISCREG_SCR_EL3, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by readBankedMiscReg(), readMiscReg(), setBankedMiscReg(), and setMiscReg().

◆ maintenanceInterruptStatus()

|

protected |

Definition at line 2453 of file gic_v3_cpu_interface.cc.

References eoiMaintenanceInterruptStatus(), ICH_LR_EL2_STATE_PENDING, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_HCR_EL2, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::MISCREG_ICH_VMCR_EL2, ArmISA::ISA::readMiscRegNoEffect(), and VIRTUAL_NUM_LIST_REGS.

Referenced by readMiscReg(), and virtualUpdate().

◆ readBankedMiscReg()

|

protected |

Definition at line 1620 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, isSecureBelowEL3(), ArmISA::ISA::readMiscRegNoEffect(), and ArmISA::ISA::snsBankedIndex64().

Referenced by readMiscReg(), and setMiscReg().

◆ readMiscReg()

|

overridevirtual |

Read a system register belonging to this device.

- Parameters

-

misc_reg Register number (see miscregs.hh)

- Returns

- Register value.

Implements ArmISA::BaseISADevice.

Definition at line 117 of file gic_v3_cpu_interface.cc.

References Gicv3Redistributor::activateIRQ(), bpr1(), currEL(), DPRINTF, ArmISA::EL1, ArmISA::EL3, Enable, eoiMaintenanceInterruptStatus(), Gicv3::G0S, Gicv3::G1NS, Gicv3::G1S, getHCREL2FMO(), getHCREL2IMO(), getHPPIR0(), getHPPIR1(), getHPPVILR(), Gicv3CPUInterface::hppi_t::group, haveEL(), highestActivePriority(), hppi, hppiCanPreempt(), hppviCanPreempt(), inSecureState(), Gicv3::INTID_SECURE, Gicv3::INTID_SPURIOUS, ArmISA::BaseISADevice::isa, isSecureBelowEL3(), maintenanceInterruptStatus(), ArmISA::MISCREG_ICC_AP0R0, ArmISA::MISCREG_ICC_AP0R0_EL1, ArmISA::MISCREG_ICC_AP0R1, ArmISA::MISCREG_ICC_AP0R1_EL1, ArmISA::MISCREG_ICC_AP0R2, ArmISA::MISCREG_ICC_AP0R2_EL1, ArmISA::MISCREG_ICC_AP0R3, ArmISA::MISCREG_ICC_AP0R3_EL1, ArmISA::MISCREG_ICC_AP1R0, ArmISA::MISCREG_ICC_AP1R0_EL1, ArmISA::MISCREG_ICC_AP1R1, ArmISA::MISCREG_ICC_AP1R1_EL1, ArmISA::MISCREG_ICC_AP1R2, ArmISA::MISCREG_ICC_AP1R2_EL1, ArmISA::MISCREG_ICC_AP1R3, ArmISA::MISCREG_ICC_AP1R3_EL1, ArmISA::MISCREG_ICC_BPR0, ArmISA::MISCREG_ICC_BPR0_EL1, ArmISA::MISCREG_ICC_BPR1, ArmISA::MISCREG_ICC_BPR1_EL1, ArmISA::MISCREG_ICC_CTLR, ArmISA::MISCREG_ICC_CTLR_EL1, ArmISA::MISCREG_ICC_CTLR_EL3, ArmISA::MISCREG_ICC_HPPIR0, ArmISA::MISCREG_ICC_HPPIR0_EL1, ArmISA::MISCREG_ICC_HPPIR1, ArmISA::MISCREG_ICC_HPPIR1_EL1, ArmISA::MISCREG_ICC_HSRE, ArmISA::MISCREG_ICC_IAR0, ArmISA::MISCREG_ICC_IAR0_EL1, ArmISA::MISCREG_ICC_IAR1, ArmISA::MISCREG_ICC_IAR1_EL1, ArmISA::MISCREG_ICC_IGRPEN0, ArmISA::MISCREG_ICC_IGRPEN0_EL1, ArmISA::MISCREG_ICC_IGRPEN1, ArmISA::MISCREG_ICC_IGRPEN1_EL1, ArmISA::MISCREG_ICC_IGRPEN1_EL1_NS, ArmISA::MISCREG_ICC_IGRPEN1_EL1_S, ArmISA::MISCREG_ICC_IGRPEN1_EL3, ArmISA::MISCREG_ICC_MCTLR, ArmISA::MISCREG_ICC_MGRPEN1, ArmISA::MISCREG_ICC_MSRE, ArmISA::MISCREG_ICC_PMR, ArmISA::MISCREG_ICC_PMR_EL1, ArmISA::MISCREG_ICC_RPR, ArmISA::MISCREG_ICC_RPR_EL1, ArmISA::MISCREG_ICC_SRE, ArmISA::MISCREG_ICC_SRE_EL1, ArmISA::MISCREG_ICC_SRE_EL2, ArmISA::MISCREG_ICC_SRE_EL3, ArmISA::MISCREG_ICH_AP0R0, ArmISA::MISCREG_ICH_AP0R0_EL2, ArmISA::MISCREG_ICH_AP0R1, ArmISA::MISCREG_ICH_AP0R1_EL2, ArmISA::MISCREG_ICH_AP0R2, ArmISA::MISCREG_ICH_AP0R2_EL2, ArmISA::MISCREG_ICH_AP0R3, ArmISA::MISCREG_ICH_AP0R3_EL2, ArmISA::MISCREG_ICH_AP1R0, ArmISA::MISCREG_ICH_AP1R0_EL2, ArmISA::MISCREG_ICH_AP1R1, ArmISA::MISCREG_ICH_AP1R1_EL2, ArmISA::MISCREG_ICH_AP1R2, ArmISA::MISCREG_ICH_AP1R2_EL2, ArmISA::MISCREG_ICH_AP1R3, ArmISA::MISCREG_ICH_AP1R3_EL2, ArmISA::MISCREG_ICH_EISR, ArmISA::MISCREG_ICH_EISR_EL2, ArmISA::MISCREG_ICH_ELRSR, ArmISA::MISCREG_ICH_ELRSR_EL2, ArmISA::MISCREG_ICH_HCR, ArmISA::MISCREG_ICH_HCR_EL2, ArmISA::MISCREG_ICH_LR0, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::MISCREG_ICH_LR15, ArmISA::MISCREG_ICH_LR15_EL2, ArmISA::MISCREG_ICH_LRC0, ArmISA::MISCREG_ICH_LRC15, ArmISA::MISCREG_ICH_MISR, ArmISA::MISCREG_ICH_MISR_EL2, ArmISA::MISCREG_ICH_VMCR, ArmISA::MISCREG_ICH_VMCR_EL2, ArmISA::MISCREG_ICH_VTR, ArmISA::MISCREG_ICH_VTR_EL2, ArmISA::MISCREG_ICV_AP0R0_EL1, ArmISA::MISCREG_ICV_AP1R0_EL1, ArmISA::MISCREG_ICV_BPR0_EL1, ArmISA::MISCREG_ICV_BPR1_EL1, ArmISA::MISCREG_ICV_CTLR_EL1, ArmISA::MISCREG_ICV_HPPIR0_EL1, ArmISA::MISCREG_ICV_HPPIR1_EL1, ArmISA::MISCREG_ICV_IAR0_EL1, ArmISA::MISCREG_ICV_IAR1_EL1, ArmISA::MISCREG_ICV_IGRPEN0_EL1, ArmISA::MISCREG_ICV_IGRPEN1_EL1, ArmISA::MISCREG_ICV_PMR_EL1, ArmISA::MISCREG_ICV_RPR_EL1, ArmISA::MISCREG_SCR_EL3, ArmISA::miscRegName, panic, readBankedMiscReg(), ArmISA::ISA::readMiscRegNoEffect(), ArmISA::ISA::setMiscRegNoEffect(), Gicv3Redistributor::SMALLEST_LPI_ID, U, VIRTUAL_NUM_LIST_REGS, VIRTUAL_PREEMPTION_BITS, VIRTUAL_PRIORITY_BITS, virtualActivateIRQ(), virtualHighestActivePriority(), and virtualUpdate().

Referenced by bpr1(), and groupPriorityMask().

◆ resetHppi()

|

protected |

Definition at line 74 of file gic_v3_cpu_interface.cc.

References hppi, Gicv3CPUInterface::hppi_t::intid, and Gicv3CPUInterface::hppi_t::prio.

Referenced by clearPendingInterrupts(), and Gicv3Redistributor::setClrLPI().

◆ serialize()

|

overrideprotectedvirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements Serializable.

Definition at line 2612 of file gic_v3_cpu_interface.cc.

References Gicv3CPUInterface::hppi_t::group, hppi, Gicv3CPUInterface::hppi_t::intid, Gicv3CPUInterface::hppi_t::prio, SERIALIZE_ENUM, and SERIALIZE_SCALAR.

◆ setBankedMiscReg()

|

protected |

Definition at line 1627 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, isSecureBelowEL3(), ArmISA::ISA::setMiscRegNoEffect(), ArmISA::ISA::snsBankedIndex64(), and X86ISA::val.

Referenced by setMiscReg().

◆ setMiscReg()

|

overridevirtual |

Write to a system register belonging to this device.

- Parameters

-

misc_reg Register number (see miscregs.hh) val Value to store

Implements ArmISA::BaseISADevice.

Definition at line 737 of file gic_v3_cpu_interface.cc.

References currEL(), deactivateIRQ(), distributor, DPRINTF, dropPriority(), Gicv3Distributor::DS, ArmISA::EL1, ArmISA::EL2, ArmISA::EL3, X86ISA::enable, Gicv3::G0S, Gicv3::G1NS, Gicv3::G1S, generateSGI(), getHCREL2FMO(), getHCREL2IMO(), Gicv3Distributor::getIntGroup(), Gicv3Redistributor::getIntGroup(), GIC_MIN_BPR, GIC_MIN_BPR_NS, haveEL(), highestActiveGroup(), inSecureState(), Gicv3::INTID_SECURE, Gicv3::INTID_SPURIOUS, ArmISA::BaseISADevice::isa, isEL3OrMon(), isEOISplitMode(), isSecureBelowEL3(), ArmISA::MISCREG_ICC_AP0R0, ArmISA::MISCREG_ICC_AP0R0_EL1, ArmISA::MISCREG_ICC_AP0R1, ArmISA::MISCREG_ICC_AP0R1_EL1, ArmISA::MISCREG_ICC_AP0R2, ArmISA::MISCREG_ICC_AP0R2_EL1, ArmISA::MISCREG_ICC_AP0R3, ArmISA::MISCREG_ICC_AP0R3_EL1, ArmISA::MISCREG_ICC_AP1R0, ArmISA::MISCREG_ICC_AP1R0_EL1, ArmISA::MISCREG_ICC_AP1R1, ArmISA::MISCREG_ICC_AP1R1_EL1, ArmISA::MISCREG_ICC_AP1R2, ArmISA::MISCREG_ICC_AP1R2_EL1, ArmISA::MISCREG_ICC_AP1R3, ArmISA::MISCREG_ICC_AP1R3_EL1, ArmISA::MISCREG_ICC_ASGI1R, ArmISA::MISCREG_ICC_ASGI1R_EL1, ArmISA::MISCREG_ICC_BPR0, ArmISA::MISCREG_ICC_BPR0_EL1, ArmISA::MISCREG_ICC_BPR1, ArmISA::MISCREG_ICC_BPR1_EL1, ArmISA::MISCREG_ICC_BPR1_EL1_NS, ArmISA::MISCREG_ICC_BPR1_EL1_S, ArmISA::MISCREG_ICC_CTLR, ArmISA::MISCREG_ICC_CTLR_EL1, ArmISA::MISCREG_ICC_CTLR_EL1_NS, ArmISA::MISCREG_ICC_CTLR_EL1_S, ArmISA::MISCREG_ICC_CTLR_EL3, ArmISA::MISCREG_ICC_DIR, ArmISA::MISCREG_ICC_DIR_EL1, ArmISA::MISCREG_ICC_EOIR0, ArmISA::MISCREG_ICC_EOIR0_EL1, ArmISA::MISCREG_ICC_EOIR1, ArmISA::MISCREG_ICC_EOIR1_EL1, ArmISA::MISCREG_ICC_HSRE, ArmISA::MISCREG_ICC_IGRPEN0, ArmISA::MISCREG_ICC_IGRPEN0_EL1, ArmISA::MISCREG_ICC_IGRPEN1, ArmISA::MISCREG_ICC_IGRPEN1_EL1, ArmISA::MISCREG_ICC_IGRPEN1_EL1_NS, ArmISA::MISCREG_ICC_IGRPEN1_EL1_S, ArmISA::MISCREG_ICC_IGRPEN1_EL3, ArmISA::MISCREG_ICC_MCTLR, ArmISA::MISCREG_ICC_MGRPEN1, ArmISA::MISCREG_ICC_MSRE, ArmISA::MISCREG_ICC_PMR, ArmISA::MISCREG_ICC_PMR_EL1, ArmISA::MISCREG_ICC_SGI0R, ArmISA::MISCREG_ICC_SGI0R_EL1, ArmISA::MISCREG_ICC_SGI1R, ArmISA::MISCREG_ICC_SGI1R_EL1, ArmISA::MISCREG_ICC_SRE, ArmISA::MISCREG_ICC_SRE_EL1, ArmISA::MISCREG_ICC_SRE_EL2, ArmISA::MISCREG_ICC_SRE_EL3, ArmISA::MISCREG_ICH_AP0R0, ArmISA::MISCREG_ICH_AP0R0_EL2, ArmISA::MISCREG_ICH_AP0R1, ArmISA::MISCREG_ICH_AP0R1_EL2, ArmISA::MISCREG_ICH_AP0R2, ArmISA::MISCREG_ICH_AP0R2_EL2, ArmISA::MISCREG_ICH_AP0R3, ArmISA::MISCREG_ICH_AP0R3_EL2, ArmISA::MISCREG_ICH_AP1R0, ArmISA::MISCREG_ICH_AP1R0_EL2, ArmISA::MISCREG_ICH_AP1R1, ArmISA::MISCREG_ICH_AP1R1_EL2, ArmISA::MISCREG_ICH_AP1R2, ArmISA::MISCREG_ICH_AP1R2_EL2, ArmISA::MISCREG_ICH_AP1R3, ArmISA::MISCREG_ICH_AP1R3_EL2, ArmISA::MISCREG_ICH_HCR, ArmISA::MISCREG_ICH_HCR_EL2, ArmISA::MISCREG_ICH_LR0, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::MISCREG_ICH_LR15, ArmISA::MISCREG_ICH_LR15_EL2, ArmISA::MISCREG_ICH_LRC0, ArmISA::MISCREG_ICH_LRC15, ArmISA::MISCREG_ICH_VMCR, ArmISA::MISCREG_ICH_VMCR_EL2, ArmISA::MISCREG_ICV_AP0R0_EL1, ArmISA::MISCREG_ICV_AP1R0_EL1, ArmISA::MISCREG_ICV_BPR0_EL1, ArmISA::MISCREG_ICV_BPR1_EL1, ArmISA::MISCREG_ICV_CTLR_EL1, ArmISA::MISCREG_ICV_DIR_EL1, ArmISA::MISCREG_ICV_EOIR0_EL1, ArmISA::MISCREG_ICV_EOIR1_EL1, ArmISA::MISCREG_ICV_IGRPEN0_EL1, ArmISA::MISCREG_ICV_IGRPEN1_EL1, ArmISA::MISCREG_ICV_PMR_EL1, ArmISA::MISCREG_SCR_EL3, ArmISA::miscRegName, panic, readBankedMiscReg(), ArmISA::ISA::readMiscRegNoEffect(), redistributor, setBankedMiscReg(), ArmISA::ISA::setMiscRegNoEffect(), U, updateDistributor(), X86ISA::val, VIRTUAL_PREEMPTION_BITS, virtualDeactivateIRQ(), virtualDropPriority(), virtualFindActive(), virtualIncrementEOICount(), virtualIsEOISplitMode(), and virtualUpdate().

◆ setThreadContext()

|

overridevirtual |

Reimplemented from ArmISA::BaseISADevice.

Definition at line 81 of file gic_v3_cpu_interface.cc.

References fatal_if, gic, Gicv3Redistributor::irqPending, maintenanceInterrupt, ArmInterruptPin::num(), Gicv3::params(), and redistributor.

◆ unserialize()

|

overrideprotectedvirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements Serializable.

Definition at line 2620 of file gic_v3_cpu_interface.cc.

References Gicv3CPUInterface::hppi_t::group, hppi, Gicv3CPUInterface::hppi_t::intid, Gicv3CPUInterface::hppi_t::prio, UNSERIALIZE_ENUM, and UNSERIALIZE_SCALAR.

◆ update()

|

protected |

Definition at line 2030 of file gic_v3_cpu_interface.cc.

References cpuId, Gicv3::deassertInt(), DPRINTF, ArmISA::EL3, Gicv3::G0S, Gicv3::G1S, gic, Gicv3CPUInterface::hppi_t::group, haveEL(), hppi, hppiCanPreempt(), ArmISA::INT_FIQ, ArmISA::INT_IRQ, intSignalType(), and Gicv3::postInt().

Referenced by dropPriority(), and Gicv3Redistributor::update().

◆ updateDistributor()

|

protected |

Definition at line 2024 of file gic_v3_cpu_interface.cc.

References distributor, and Gicv3Distributor::update().

Referenced by deactivateIRQ(), and setMiscReg().

◆ virtualActivateIRQ()

|

protected |

Definition at line 1861 of file gic_v3_cpu_interface.cc.

References Gicv3::G0S, Gicv3::G1NS, ICH_LR_EL2_STATE_ACTIVE, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_AP0R0_EL2, ArmISA::MISCREG_ICH_AP1R0_EL2, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::ISA::readMiscRegNoEffect(), ArmISA::ISA::setMiscRegNoEffect(), and VIRTUAL_PREEMPTION_BITS.

Referenced by readMiscReg().

◆ virtualDeactivateIRQ()

|

protected |

Definition at line 1896 of file gic_v3_cpu_interface.cc.

References deactivateIRQ(), distributor, Gicv3Distributor::getIntGroup(), Gicv3Redistributor::getIntGroup(), ICH_LR_EL2_STATE_ACTIVE, Gicv3::INTID_SECURE, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::ISA::readMiscRegNoEffect(), redistributor, and ArmISA::ISA::setMiscRegNoEffect().

Referenced by setMiscReg().

◆ virtualDropPriority()

|

protected |

Definition at line 1741 of file gic_v3_cpu_interface.cc.

References ctz32(), GIC_MIN_VBPR, ArmISA::i, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_AP0R0_EL2, ArmISA::MISCREG_ICH_AP1R0_EL2, ArmISA::ISA::readMiscRegNoEffect(), ArmISA::ISA::setMiscRegNoEffect(), and VIRTUAL_PREEMPTION_BITS.

Referenced by setMiscReg().

◆ virtualFindActive()

|

protected |

Definition at line 1634 of file gic_v3_cpu_interface.cc.

References ICH_LR_EL2_STATE_ACTIVE, ICH_LR_EL2_STATE_ACTIVE_PENDING, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_LR0_EL2, ArmISA::ISA::readMiscRegNoEffect(), and VIRTUAL_NUM_LIST_REGS.

Referenced by setMiscReg().

◆ virtualGroupPriorityMask()

|

protected |

Definition at line 1952 of file gic_v3_cpu_interface.cc.

References Gicv3::G0S, Gicv3::G1NS, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_VMCR_EL2, ArmISA::ISA::readMiscRegNoEffect(), and U.

Referenced by hppviCanPreempt().

◆ virtualHighestActivePriority()

|

protected |

Definition at line 2193 of file gic_v3_cpu_interface.cc.

References ctz32(), GIC_MIN_VBPR, ArmISA::i, ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_AP0R0_EL2, ArmISA::MISCREG_ICH_AP1R0_EL2, ArmISA::ISA::readMiscRegNoEffect(), and VIRTUAL_PRIORITY_BITS.

Referenced by hppviCanPreempt(), and readMiscReg().

◆ virtualIncrementEOICount()

|

protected |

Definition at line 2214 of file gic_v3_cpu_interface.cc.

References bits(), insertBits(), ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_HCR_EL2, ArmISA::ISA::readMiscRegNoEffect(), and ArmISA::ISA::setMiscRegNoEffect().

Referenced by setMiscReg().

◆ virtualIsEOISplitMode()

|

protected |

Definition at line 1995 of file gic_v3_cpu_interface.cc.

References ArmISA::BaseISADevice::isa, ArmISA::MISCREG_ICH_VMCR_EL2, and ArmISA::ISA::readMiscRegNoEffect().

Referenced by setMiscReg().

◆ virtualUpdate()

|

protected |

Definition at line 2064 of file gic_v3_cpu_interface.cc.

References ArmInterruptPin::clear(), cpuId, Gicv3::deassertInt(), DPRINTF, getHPPVILR(), gic, hppviCanPreempt(), ArmISA::INT_VIRT_FIQ, ArmISA::INT_VIRT_IRQ, Gicv3Redistributor::irqPending, ArmISA::BaseISADevice::isa, maintenanceInterrupt, maintenanceInterruptStatus(), ArmISA::MISCREG_ICH_HCR_EL2, ArmISA::MISCREG_ICH_LR0_EL2, ArmInterruptPin::num(), Gicv3::postInt(), ArmInterruptPin::raise(), ArmISA::ISA::readMiscRegNoEffect(), and redistributor.

Referenced by readMiscReg(), and setMiscReg().

Friends And Related Function Documentation

◆ Gicv3Distributor

|

friend |

Definition at line 54 of file gic_v3_cpu_interface.hh.

◆ Gicv3Redistributor

|

friend |

Definition at line 55 of file gic_v3_cpu_interface.hh.

Member Data Documentation

◆ A3V [1/2]

|

protected |

Definition at line 71 of file gic_v3_cpu_interface.hh.

◆ A3V [2/2]

|

protected |

Definition at line 276 of file gic_v3_cpu_interface.hh.

◆ CBPR

|

protected |

Definition at line 79 of file gic_v3_cpu_interface.hh.

◆ CBPR_EL1NS

|

protected |

Definition at line 98 of file gic_v3_cpu_interface.hh.

◆ CBPR_EL1S

|

protected |

Definition at line 99 of file gic_v3_cpu_interface.hh.

◆ cpuId

|

protected |

Definition at line 62 of file gic_v3_cpu_interface.hh.

Referenced by assertWakeRequest(), clearPendingInterrupts(), deassertWakeRequest(), havePendingInterrupts(), init(), update(), and virtualUpdate().

◆ DFB

|

protected |

Definition at line 121 of file gic_v3_cpu_interface.hh.

◆ DIB

|

protected |

Definition at line 120 of file gic_v3_cpu_interface.hh.

◆ distributor

|

protected |

Definition at line 61 of file gic_v3_cpu_interface.hh.

Referenced by deactivateIRQ(), getHPPIR0(), getHPPIR1(), groupEnabled(), init(), intSignalType(), setMiscReg(), updateDistributor(), and virtualDeactivateIRQ().

◆ En

|

protected |

Definition at line 212 of file gic_v3_cpu_interface.hh.

◆ Enable [1/2]

|

protected |

Definition at line 104 of file gic_v3_cpu_interface.hh.

Referenced by readMiscReg().

◆ Enable [2/2]

|

protected |

Definition at line 127 of file gic_v3_cpu_interface.hh.

◆ EnableGrp1NS

|

protected |

Definition at line 115 of file gic_v3_cpu_interface.hh.

◆ EnableGrp1S

|

protected |

Definition at line 114 of file gic_v3_cpu_interface.hh.

◆ EOI [1/3]

|

protected |

Definition at line 223 of file gic_v3_cpu_interface.hh.

◆ EOI [2/3]

|

protected |

Definition at line 240 of file gic_v3_cpu_interface.hh.

◆ EOI [3/3]

|

protected |

Definition at line 252 of file gic_v3_cpu_interface.hh.

◆ EOIcount

|

protected |

Definition at line 197 of file gic_v3_cpu_interface.hh.

◆ EOImode

|

protected |

Definition at line 78 of file gic_v3_cpu_interface.hh.

◆ EOImode_EL1NS

|

protected |

Definition at line 95 of file gic_v3_cpu_interface.hh.

◆ EOImode_EL1S

|

protected |

Definition at line 96 of file gic_v3_cpu_interface.hh.

◆ EOImode_EL3

|

protected |

Definition at line 97 of file gic_v3_cpu_interface.hh.

◆ ExtRange

|

protected |

Definition at line 68 of file gic_v3_cpu_interface.hh.

◆ gic

|

protected |

Definition at line 59 of file gic_v3_cpu_interface.hh.

Referenced by assertWakeRequest(), clearPendingInterrupts(), deassertWakeRequest(), generateSGI(), haveEL(), havePendingInterrupts(), init(), inSecureState(), setThreadContext(), update(), and virtualUpdate().

◆ GIC_MIN_BPR

|

staticprotected |

Definition at line 144 of file gic_v3_cpu_interface.hh.

Referenced by bpr1(), highestActivePriority(), and setMiscReg().

◆ GIC_MIN_BPR_NS

|

staticprotected |

Definition at line 146 of file gic_v3_cpu_interface.hh.

Referenced by bpr1(), and setMiscReg().

◆ GIC_MIN_VBPR

|

staticprotected |

Definition at line 152 of file gic_v3_cpu_interface.hh.

Referenced by virtualDropPriority(), and virtualHighestActivePriority().

◆ GICC_APR

|

staticprotected |

Definition at line 179 of file gic_v3_cpu_interface.hh.

◆ GICC_NSAPR

|

staticprotected |

Definition at line 180 of file gic_v3_cpu_interface.hh.

◆ GICH_APR

|

staticprotected |

Definition at line 192 of file gic_v3_cpu_interface.hh.

◆ GICH_LR

|

staticprotected |

Definition at line 193 of file gic_v3_cpu_interface.hh.

◆ Group [1/2]

|

protected |

Definition at line 218 of file gic_v3_cpu_interface.hh.

◆ Group [2/2]

|

protected |

Definition at line 235 of file gic_v3_cpu_interface.hh.

◆ hppi

|

protected |

Definition at line 160 of file gic_v3_cpu_interface.hh.

Referenced by clearPendingInterrupts(), getHPPIR0(), getHPPIR1(), Gicv3CPUInterface(), havePendingInterrupts(), hppiCanPreempt(), readMiscReg(), resetHppi(), serialize(), unserialize(), Gicv3Redistributor::update(), Gicv3Distributor::update(), and update().

◆ HW [1/2]

|

protected |

Definition at line 217 of file gic_v3_cpu_interface.hh.

◆ HW [2/2]

|

protected |

Definition at line 234 of file gic_v3_cpu_interface.hh.

◆ ICH_LR_EL2_STATE_ACTIVE

|

staticprotected |

Definition at line 229 of file gic_v3_cpu_interface.hh.

Referenced by virtualActivateIRQ(), virtualDeactivateIRQ(), and virtualFindActive().

◆ ICH_LR_EL2_STATE_ACTIVE_PENDING

|

staticprotected |

Definition at line 230 of file gic_v3_cpu_interface.hh.

Referenced by virtualFindActive().

◆ ICH_LR_EL2_STATE_PENDING

|

staticprotected |

Definition at line 228 of file gic_v3_cpu_interface.hh.

Referenced by maintenanceInterruptStatus().

◆ IDbits [1/2]

|

protected |

Definition at line 73 of file gic_v3_cpu_interface.hh.

◆ IDbits [2/2]

|

protected |

Definition at line 274 of file gic_v3_cpu_interface.hh.

◆ ListRegs

|

protected |

Definition at line 280 of file gic_v3_cpu_interface.hh.

◆ LRENP

|

protected |

Definition at line 250 of file gic_v3_cpu_interface.hh.

◆ LRENPIE

|

protected |

Definition at line 210 of file gic_v3_cpu_interface.hh.

◆ maintenanceInterrupt

|

protected |

Definition at line 64 of file gic_v3_cpu_interface.hh.

Referenced by setThreadContext(), and virtualUpdate().

◆ nDS

|

protected |

Definition at line 86 of file gic_v3_cpu_interface.hh.

◆ NP

|

protected |

Definition at line 249 of file gic_v3_cpu_interface.hh.

◆ NPIE

|

protected |

Definition at line 209 of file gic_v3_cpu_interface.hh.

◆ pINTID [1/2]

|

protected |

Definition at line 222 of file gic_v3_cpu_interface.hh.

◆ pINTID [2/2]

|

protected |

Definition at line 239 of file gic_v3_cpu_interface.hh.

◆ PMHE

|

protected |

Definition at line 76 of file gic_v3_cpu_interface.hh.

◆ PREbits

|

protected |

Definition at line 273 of file gic_v3_cpu_interface.hh.

◆ PRIbits [1/2]

|

protected |

Definition at line 74 of file gic_v3_cpu_interface.hh.

◆ PRIbits [2/2]

|

protected |

Definition at line 272 of file gic_v3_cpu_interface.hh.

◆ Priority [1/2]

|

protected |

Definition at line 220 of file gic_v3_cpu_interface.hh.

◆ Priority [2/2]

|

protected |

Definition at line 237 of file gic_v3_cpu_interface.hh.

◆ redistributor

|

protected |

Definition at line 60 of file gic_v3_cpu_interface.hh.

Referenced by deactivateIRQ(), generateSGI(), init(), setMiscReg(), setThreadContext(), virtualDeactivateIRQ(), and virtualUpdate().

◆ res0

|

protected |

Definition at line 103 of file gic_v3_cpu_interface.hh.

◆ res0_0 [1/8]

|

protected |

Definition at line 77 of file gic_v3_cpu_interface.hh.

◆ res0_0 [2/8]

|

protected |

Definition at line 92 of file gic_v3_cpu_interface.hh.

◆ res0_0 [3/8]

|

protected |

Definition at line 204 of file gic_v3_cpu_interface.hh.

◆ res0_0 [4/8]

|

protected |

Definition at line 221 of file gic_v3_cpu_interface.hh.

◆ res0_0 [5/8]

|

protected |

Definition at line 238 of file gic_v3_cpu_interface.hh.

◆ res0_0 [6/8]

|

protected |

Definition at line 262 of file gic_v3_cpu_interface.hh.

◆ res0_0 [7/8]

|

protected |

Definition at line 279 of file gic_v3_cpu_interface.hh.

◆ res0_0 [8/8]

|

protected |

Definition at line 291 of file gic_v3_cpu_interface.hh.

◆ res0_1 [1/8]

|

protected |

Definition at line 75 of file gic_v3_cpu_interface.hh.

◆ res0_1 [2/8]

|

protected |

Definition at line 87 of file gic_v3_cpu_interface.hh.

◆ res0_1 [3/8]

|

protected |

Definition at line 198 of file gic_v3_cpu_interface.hh.

◆ res0_1 [4/8]

|

protected |

Definition at line 219 of file gic_v3_cpu_interface.hh.

◆ res0_1 [5/8]

|

protected |

Definition at line 236 of file gic_v3_cpu_interface.hh.

◆ res0_1 [6/8]

|

protected |

Definition at line 260 of file gic_v3_cpu_interface.hh.

◆ res0_1 [7/8]

|

protected |

Definition at line 271 of file gic_v3_cpu_interface.hh.

◆ res0_1 [8/8]

|

protected |

Definition at line 286 of file gic_v3_cpu_interface.hh.

◆ res0_2 [1/2]

|

protected |

Definition at line 70 of file gic_v3_cpu_interface.hh.

◆ res0_2 [2/2]

|

protected |

Definition at line 83 of file gic_v3_cpu_interface.hh.

◆ res0_3

|

protected |

Definition at line 67 of file gic_v3_cpu_interface.hh.

◆ res1

|

protected |

Definition at line 277 of file gic_v3_cpu_interface.hh.

◆ RM

|

protected |

Definition at line 94 of file gic_v3_cpu_interface.hh.

◆ RSS

|

protected |

Definition at line 69 of file gic_v3_cpu_interface.hh.

◆ SEIS [1/2]

|

protected |

Definition at line 72 of file gic_v3_cpu_interface.hh.

◆ SEIS [2/2]

|

protected |

Definition at line 275 of file gic_v3_cpu_interface.hh.

◆ SRE

|

protected |

Definition at line 122 of file gic_v3_cpu_interface.hh.

◆ State

|

protected |

Definition at line 216 of file gic_v3_cpu_interface.hh.

◆ TALL0

|

protected |

Definition at line 202 of file gic_v3_cpu_interface.hh.

◆ TALL1

|

protected |

Definition at line 201 of file gic_v3_cpu_interface.hh.

◆ TC

|

protected |

Definition at line 203 of file gic_v3_cpu_interface.hh.

◆ TDIR

|

protected |

Definition at line 199 of file gic_v3_cpu_interface.hh.

◆ TDS

|

protected |

Definition at line 278 of file gic_v3_cpu_interface.hh.

◆ TSEI

|

protected |

Definition at line 200 of file gic_v3_cpu_interface.hh.

◆ U

|

protected |

Definition at line 251 of file gic_v3_cpu_interface.hh.

Referenced by groupPriorityMask(), readMiscReg(), setMiscReg(), and virtualGroupPriorityMask().

◆ UIE

|

protected |

Definition at line 211 of file gic_v3_cpu_interface.hh.

◆ VAckCtl

|

protected |

Definition at line 265 of file gic_v3_cpu_interface.hh.

◆ VBPR0

|

protected |

Definition at line 258 of file gic_v3_cpu_interface.hh.

◆ VBPR1

|

protected |

Definition at line 259 of file gic_v3_cpu_interface.hh.

◆ VCBPR

|

protected |

Definition at line 263 of file gic_v3_cpu_interface.hh.

◆ VENG0

|

protected |

Definition at line 267 of file gic_v3_cpu_interface.hh.

◆ VENG1

|

protected |

Definition at line 266 of file gic_v3_cpu_interface.hh.

◆ VEOIM

|

protected |

Definition at line 261 of file gic_v3_cpu_interface.hh.

◆ VFIQEn

|

protected |

Definition at line 264 of file gic_v3_cpu_interface.hh.

◆ VGrp0D

|

protected |

Definition at line 247 of file gic_v3_cpu_interface.hh.

◆ VGrp0DIE

|

protected |

Definition at line 207 of file gic_v3_cpu_interface.hh.

◆ VGrp0E

|

protected |

Definition at line 248 of file gic_v3_cpu_interface.hh.

◆ VGrp0EIE

|

protected |

Definition at line 208 of file gic_v3_cpu_interface.hh.

◆ VGrp1D

|

protected |

Definition at line 245 of file gic_v3_cpu_interface.hh.

◆ VGrp1DIE

|

protected |

Definition at line 205 of file gic_v3_cpu_interface.hh.

◆ VGrp1E

|

protected |

Definition at line 246 of file gic_v3_cpu_interface.hh.

◆ VGrp1EIE

|

protected |

Definition at line 206 of file gic_v3_cpu_interface.hh.

◆ vINTID

|

protected |

Definition at line 224 of file gic_v3_cpu_interface.hh.

◆ VIRTUAL_NUM_LIST_REGS

|

staticprotected |

Definition at line 150 of file gic_v3_cpu_interface.hh.

Referenced by eoiMaintenanceInterruptStatus(), maintenanceInterruptStatus(), readMiscReg(), and virtualFindActive().

◆ VIRTUAL_PREEMPTION_BITS

|

staticprotected |

Definition at line 149 of file gic_v3_cpu_interface.hh.

Referenced by readMiscReg(), setMiscReg(), virtualActivateIRQ(), and virtualDropPriority().

◆ VIRTUAL_PRIORITY_BITS

|

staticprotected |

Definition at line 148 of file gic_v3_cpu_interface.hh.

Referenced by readMiscReg(), and virtualHighestActivePriority().

◆ VPMR

|

protected |

Definition at line 257 of file gic_v3_cpu_interface.hh.

The documentation for this class was generated from the following files:

- dev/arm/gic_v3_cpu_interface.hh

- dev/arm/gic_v3_cpu_interface.cc