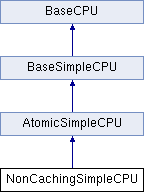

The NonCachingSimpleCPU is an AtomicSimpleCPU using the 'atomic_noncaching' memory mode instead of just 'atomic'. More...

#include <noncaching.hh>

Public Member Functions | |

| NonCachingSimpleCPU (NonCachingSimpleCPUParams *p) | |

| void | verifyMemoryMode () const override |

| Verify that the system is in a memory mode supported by the CPU. More... | |

Public Member Functions inherited from AtomicSimpleCPU Public Member Functions inherited from AtomicSimpleCPU | |

| AtomicSimpleCPU (AtomicSimpleCPUParams *params) | |

| virtual | ~AtomicSimpleCPU () |

| void | init () override |

| DrainState | drain () override |

| void | drainResume () override |

| void | switchOut () override |

| Prepare for another CPU to take over execution. More... | |

| void | takeOverFrom (BaseCPU *oldCPU) override |

| Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in. More... | |

| void | activateContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now active. More... | |

| void | suspendContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now suspended. More... | |

| bool | genMemFragmentRequest (const RequestPtr &req, Addr frag_addr, int size, Request::Flags flags, const std::vector< bool > &byte_enable, int &frag_size, int &size_left) const |

| Helper function used to set up the request for a single fragment of a memory access. More... | |

| Fault | readMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | initiateHtmCmd (Request::Flags flags) override |

| Hardware transactional memory commands (HtmCmds), e.g. More... | |

| void | htmSendAbortSignal (HtmFailureFaultCause cause) override |

| This function is used to instruct the memory subsystem that a transaction should be aborted and the speculative state should be thrown away. More... | |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | amoMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| void | regProbePoints () override |

| void | printAddr (Addr a) |

| Print state of address in memory system via PrintReq (for debugging). More... | |

Public Member Functions inherited from BaseSimpleCPU Public Member Functions inherited from BaseSimpleCPU | |

| BaseSimpleCPU (BaseSimpleCPUParams *params) | |

| virtual | ~BaseSimpleCPU () |

| void | wakeup (ThreadID tid) override |

| void | init () override |

| void | checkForInterrupts () |

| void | setupFetchRequest (const RequestPtr &req) |

| void | preExecute () |

| void | postExecute () |

| void | advancePC (const Fault &fault) |

| void | haltContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now halted. More... | |

| void | regStats () override |

| void | resetStats () override |

| virtual Fault | initiateMemRead (Addr addr, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| virtual Fault | initiateMemAMO (Addr addr, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| void | countInst () |

| Counter | totalInsts () const override |

| Counter | totalOps () const override |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| Serialize a single thread. More... | |

| void | unserializeThread (CheckpointIn &cp, ThreadID tid) override |

| Unserialize one thread. More... | |

Public Member Functions inherited from BaseCPU Public Member Functions inherited from BaseCPU | |

| virtual PortProxy::SendFunctionalFunc | getSendFunctional () |

| Returns a sendFunctional delegate for use with port proxies. More... | |

| int | cpuId () const |

| Reads this CPU's ID. More... | |

| uint32_t | socketId () const |

| Reads this CPU's Socket ID. More... | |

| RequestorID | dataRequestorId () const |

| Reads this CPU's unique data requestor ID. More... | |

| RequestorID | instRequestorId () const |

| Reads this CPU's unique instruction requestor ID. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. More... | |

| uint32_t | taskId () const |

| Get cpu task id. More... | |

| void | taskId (uint32_t id) |

| Set cpu task id. More... | |

| uint32_t | getPid () const |

| void | setPid (uint32_t pid) |

| void | workItemBegin () |

| void | workItemEnd () |

| Tick | instCount () |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupts (ThreadID tid) |

| bool | checkInterrupts (ThreadID tid) const |

| Trace::InstTracer * | getTracer () |

| Provide access to the tracer pointer. More... | |

| int | findContext (ThreadContext *tc) |

| Given a Thread Context pointer return the thread num. More... | |

| virtual ThreadContext * | getContext (int tn) |

| Given a thread num get tho thread context for it. More... | |

| unsigned | numContexts () |

| Get the number of thread contexts available. More... | |

| ThreadID | contextToThread (ContextID cid) |

| Convert ContextID to threadID. More... | |

| const Params * | params () const |

| BaseCPU (Params *params, bool is_checker=false) | |

| virtual | ~BaseCPU () |

| void | init () override |

| void | startup () override |

| void | regStats () override |

| void | regProbePoints () override |

| void | registerThreadContexts () |

| void | deschedulePowerGatingEvent () |

| void | schedulePowerGatingEvent () |

| void | flushTLBs () |

| Flush all TLBs in the CPU. More... | |

| bool | switchedOut () const |

| Determine if the CPU is switched out. More... | |

| unsigned int | cacheLineSize () const |

| Get the cache line size of the system. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. More... | |

| void | scheduleInstStop (ThreadID tid, Counter insts, const char *cause) |

| Schedule an event that exits the simulation loops after a predefined number of instructions. More... | |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| Get the number of instructions executed by the specified thread on this CPU. More... | |

| void | traceFunctions (Addr pc) |

| void | armMonitor (ThreadID tid, Addr address) |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseTLB *dtb) |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| bool | waitForRemoteGDB () const |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| Helper method to trigger PMU probes for a committed instruction. More... | |

Protected Member Functions | |

| Tick | sendPacket (RequestPort &port, const PacketPtr &pkt) override |

Protected Member Functions inherited from AtomicSimpleCPU Protected Member Functions inherited from AtomicSimpleCPU | |

| void | tick () |

| bool | isCpuDrained () const |

| Check if a system is in a drained state. More... | |

| bool | tryCompleteDrain () |

| Try to complete a drain request. More... | |

| Port & | getDataPort () override |

| Return a reference to the data port. More... | |

| Port & | getInstPort () override |

| Return a reference to the instruction port. More... | |

| void | threadSnoop (PacketPtr pkt, ThreadID sender) |

| Perform snoop for other cpu-local thread contexts. More... | |

Protected Member Functions inherited from BaseSimpleCPU Protected Member Functions inherited from BaseSimpleCPU | |

| void | checkPcEventQueue () |

| void | swapActiveThread () |

| void | traceFault () |

| Handler used when encountering a fault; its purpose is to tear down the InstRecord. More... | |

Protected Member Functions inherited from BaseCPU Protected Member Functions inherited from BaseCPU | |

| void | updateCycleCounters (CPUState state) |

| base method keeping track of cycle progression More... | |

| void | enterPwrGating () |

| ProbePoints::PMUUPtr | pmuProbePoint (const char *name) |

| Helper method to instantiate probe points belonging to this object. More... | |

Additional Inherited Members | |

Public Types inherited from BaseCPU Public Types inherited from BaseCPU | |

| typedef BaseCPUParams | Params |

Static Public Member Functions inherited from BaseCPU Static Public Member Functions inherited from BaseCPU | |

| static int | numSimulatedInsts () |

| static int | numSimulatedOps () |

| static void | wakeup (ThreadID tid) |

| static int | numSimulatedCPUs () |

| static Counter | numSimulatedInsts () |

| static Counter | numSimulatedOps () |

Public Attributes inherited from BaseSimpleCPU Public Attributes inherited from BaseSimpleCPU | |

| Trace::InstRecord * | traceData |

| CheckerCPU * | checker |

| std::vector< SimpleExecContext * > | threadInfo |

| std::list< ThreadID > | activeThreads |

| TheISA::MachInst | inst |

| Current instruction. More... | |

| StaticInstPtr | curStaticInst |

| StaticInstPtr | curMacroStaticInst |

Public Attributes inherited from BaseCPU Public Attributes inherited from BaseCPU | |

| ThreadID | numThreads |

| Number of threads we're actually simulating (<= SMT_MAX_THREADS). More... | |

| System * | system |

| Stats::Scalar | numCycles |

| Stats::Scalar | numWorkItemsStarted |

| Stats::Scalar | numWorkItemsCompleted |

| Cycles | syscallRetryLatency |

Static Public Attributes inherited from BaseCPU Static Public Attributes inherited from BaseCPU | |

| static const uint32_t | invldPid = std::numeric_limits<uint32_t>::max() |

| Invalid or unknown Pid. More... | |

| static const Addr | PCMask = ~((Addr)sizeof(TheISA::MachInst) - 1) |

Protected Types inherited from BaseSimpleCPU Protected Types inherited from BaseSimpleCPU | |

| enum | Status { Idle, Running, Faulting, ITBWaitResponse, IcacheRetry, IcacheWaitResponse, IcacheWaitSwitch, DTBWaitResponse, DcacheRetry, DcacheWaitResponse, DcacheWaitSwitch } |

Protected Types inherited from BaseCPU Protected Types inherited from BaseCPU | |

| enum | CPUState { CPU_STATE_ON, CPU_STATE_SLEEP, CPU_STATE_WAKEUP } |

Protected Attributes inherited from AtomicSimpleCPU Protected Attributes inherited from AtomicSimpleCPU | |

| EventFunctionWrapper | tickEvent |

| const int | width |

| bool | locked |

| const bool | simulate_data_stalls |

| const bool | simulate_inst_stalls |

| AtomicCPUPort | icachePort |

| AtomicCPUDPort | dcachePort |

| RequestPtr | ifetch_req |

| RequestPtr | data_read_req |

| RequestPtr | data_write_req |

| RequestPtr | data_amo_req |

| bool | dcache_access |

| Tick | dcache_latency |

| ProbePointArg< std::pair< SimpleThread *, const StaticInstPtr > > * | ppCommit |

| Probe Points. More... | |

Protected Attributes inherited from BaseSimpleCPU Protected Attributes inherited from BaseSimpleCPU | |

| ThreadID | curThread |

| BPredUnit * | branchPred |

| Status | _status |

Protected Attributes inherited from BaseCPU Protected Attributes inherited from BaseCPU | |

| Tick | instCnt |

| Instruction count used for SPARC misc register. More... | |

| int | _cpuId |

| const uint32_t | _socketId |

| Each cpu will have a socket ID that corresponds to its physical location in the system. More... | |

| RequestorID | _instRequestorId |

| instruction side request id that must be placed in all requests More... | |

| RequestorID | _dataRequestorId |

| data side request id that must be placed in all requests More... | |

| uint32_t | _taskId |

| An intrenal representation of a task identifier within gem5. More... | |

| uint32_t | _pid |

| The current OS process ID that is executing on this processor. More... | |

| bool | _switchedOut |

| Is the CPU switched out or active? More... | |

| const unsigned int | _cacheLineSize |

| Cache the cache line size that we get from the system. More... | |

| std::vector< BaseInterrupts * > | interrupts |

| std::vector< ThreadContext * > | threadContexts |

| Trace::InstTracer * | tracer |

| Cycles | previousCycle |

| CPUState | previousState |

| const Cycles | pwrGatingLatency |

| const bool | powerGatingOnIdle |

| EventFunctionWrapper | enterPwrGatingEvent |

| ProbePoints::PMUUPtr | ppRetiredInsts |

| Instruction commit probe point. More... | |

| ProbePoints::PMUUPtr | ppRetiredInstsPC |

| ProbePoints::PMUUPtr | ppRetiredLoads |

| Retired load instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredStores |

| Retired store instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredBranches |

| Retired branches (any type) More... | |

| ProbePoints::PMUUPtr | ppAllCycles |

| CPU cycle counter even if any thread Context is suspended. More... | |

| ProbePoints::PMUUPtr | ppActiveCycles |

| CPU cycle counter, only counts if any thread contexts is active. More... | |

| ProbePointArg< bool > * | ppSleeping |

| ProbePoint that signals transitions of threadContexts sets. More... | |

Detailed Description

The NonCachingSimpleCPU is an AtomicSimpleCPU using the 'atomic_noncaching' memory mode instead of just 'atomic'.

Definition at line 48 of file noncaching.hh.

Constructor & Destructor Documentation

◆ NonCachingSimpleCPU()

| NonCachingSimpleCPU::NonCachingSimpleCPU | ( | NonCachingSimpleCPUParams * | p | ) |

Definition at line 40 of file noncaching.cc.

Member Function Documentation

◆ sendPacket()

|

overrideprotectedvirtual |

Reimplemented from AtomicSimpleCPU.

Definition at line 55 of file noncaching.cc.

References PhysicalMemory::access(), Packet::getAddr(), System::getPhysMem(), System::isMemAddr(), RequestPort::sendAtomic(), and BaseCPU::system.

◆ verifyMemoryMode()

|

overridevirtual |

Verify that the system is in a memory mode supported by the CPU.

Implementations are expected to query the system for the current memory mode and ensure that it is what the CPU model expects. If the check fails, the implementation should terminate the simulation using fatal().

Reimplemented from AtomicSimpleCPU.

Definition at line 46 of file noncaching.cc.

References System::bypassCaches(), fatal, System::isAtomicMode(), and BaseCPU::system.

The documentation for this class was generated from the following files:

- cpu/simple/noncaching.hh

- cpu/simple/noncaching.cc