#include <op_encodings.hh>

Public Member Functions | |

| Inst_VOP3P (InFmt_VOP3P *, const std::string &opcode) | |

| ~Inst_VOP3P () | |

| int | instSize () const override |

| void | generateDisassembly () override |

| void | initOperandInfo () override |

Public Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst Public Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| VEGAGPUStaticInst (const std::string &opcode) | |

| ~VEGAGPUStaticInst () | |

| void | generateDisassembly () override |

| bool | isFlatScratchRegister (int opIdx) override |

| bool | isExecMaskRegister (int opIdx) override |

| void | initOperandInfo () override |

| int | getOperandSize (int opIdx) override |

| int | coalescerTokenCount () const override |

| Return the number of tokens needed by the coalescer. | |

| ScalarRegU32 | srcLiteral () const override |

Public Member Functions inherited from gem5::GPUStaticInst Public Member Functions inherited from gem5::GPUStaticInst | |

| GPUStaticInst (const std::string &opcode) | |

| virtual | ~GPUStaticInst () |

| void | instAddr (int inst_addr) |

| int | instAddr () const |

| int | nextInstAddr () const |

| void | instNum (int num) |

| int | instNum () |

| void | ipdInstNum (int num) |

| int | ipdInstNum () const |

| void | initDynOperandInfo (Wavefront *wf, ComputeUnit *cu) |

| virtual void | execute (GPUDynInstPtr gpuDynInst)=0 |

| const std::string & | disassemble () |

| virtual int | getNumOperands ()=0 |

| virtual int | numDstRegOperands ()=0 |

| virtual int | numSrcRegOperands ()=0 |

| int | numSrcVecOperands () |

| int | numDstVecOperands () |

| int | numSrcVecDWords () |

| int | numDstVecDWords () |

| int | numSrcScalarOperands () |

| int | numDstScalarOperands () |

| int | numSrcScalarDWords () |

| int | numDstScalarDWords () |

| int | maxOperandSize () |

| bool | isALU () const |

| bool | isBranch () const |

| bool | isCondBranch () const |

| bool | isNop () const |

| bool | isReturn () const |

| bool | isEndOfKernel () const |

| bool | isKernelLaunch () const |

| bool | isSDWAInst () const |

| bool | isDPPInst () const |

| bool | isUnconditionalJump () const |

| bool | isSpecialOp () const |

| bool | isWaitcnt () const |

| bool | isSleep () const |

| bool | isBarrier () const |

| bool | isMemSync () const |

| bool | isMemRef () const |

| bool | isFlat () const |

| bool | isFlatGlobal () const |

| bool | isFlatScratch () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isAtomicNoRet () const |

| bool | isAtomicRet () const |

| bool | isScalar () const |

| bool | readsSCC () const |

| bool | writesSCC () const |

| bool | readsVCC () const |

| bool | writesVCC () const |

| bool | readsEXEC () const |

| bool | writesEXEC () const |

| bool | readsMode () const |

| bool | writesMode () const |

| bool | ignoreExec () const |

| bool | isAtomicAnd () const |

| bool | isAtomicOr () const |

| bool | isAtomicXor () const |

| bool | isAtomicCAS () const |

| bool | isAtomicExch () const |

| bool | isAtomicAdd () const |

| bool | isAtomicSub () const |

| bool | isAtomicInc () const |

| bool | isAtomicDec () const |

| bool | isAtomicMax () const |

| bool | isAtomicMin () const |

| bool | isArgLoad () const |

| bool | isGlobalMem () const |

| bool | isLocalMem () const |

| bool | isArgSeg () const |

| bool | isGlobalSeg () const |

| bool | isGroupSeg () const |

| bool | isKernArgSeg () const |

| bool | isPrivateSeg () const |

| bool | isReadOnlySeg () const |

| bool | isSpillSeg () const |

| bool | isGloballyCoherent () const |

| Coherence domain of a memory instruction. | |

| bool | isSystemCoherent () const |

| bool | isI8 () const |

| bool | isF16 () const |

| bool | isF32 () const |

| bool | isF64 () const |

| bool | isFMA () const |

| bool | isMAC () const |

| bool | isMAD () const |

| bool | isMFMA () const |

| bool | hasNoAddr () const |

| virtual void | initiateAcc (GPUDynInstPtr gpuDynInst) |

| virtual void | completeAcc (GPUDynInstPtr gpuDynInst) |

| virtual uint32_t | getTargetPc () |

| void | setFlag (Flags flag) |

| const std::string & | opcode () const |

| const std::vector< OperandInfo > & | srcOperands () const |

| const std::vector< OperandInfo > & | dstOperands () const |

| const std::vector< OperandInfo > & | srcVecRegOperands () const |

| const std::vector< OperandInfo > & | dstVecRegOperands () const |

| const std::vector< OperandInfo > & | srcScalarRegOperands () const |

| const std::vector< OperandInfo > & | dstScalarRegOperands () const |

Protected Member Functions | |

| template<typename T > | |

| void | vop3pHelper (GPUDynInstPtr gpuDynInst, T(*fOpImpl)(T, T, bool)) |

| template<typename T > | |

| void | vop3pHelper (GPUDynInstPtr gpuDynInst, T(*fOpImpl)(T, T, T, bool)) |

| void | dotHelper (GPUDynInstPtr gpuDynInst, uint32_t(*fOpImpl)(uint32_t, uint32_t, uint32_t, bool)) |

Protected Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst Protected Member Functions inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| void | panicUnimplemented () const |

Protected Attributes | |

| InFmt_VOP3P | instData |

| InFmt_VOP3P_1 | extData |

Protected Attributes inherited from gem5::VegaISA::VEGAGPUStaticInst Protected Attributes inherited from gem5::VegaISA::VEGAGPUStaticInst | |

| ScalarRegU32 | _srcLiteral |

| if the instruction has a src literal - an immediate value that is part of the instruction stream - we store that here | |

Protected Attributes inherited from gem5::GPUStaticInst Protected Attributes inherited from gem5::GPUStaticInst | |

| const std::string | _opcode |

| std::string | disassembly |

| int | _instNum |

| int | _instAddr |

| std::vector< OperandInfo > | srcOps |

| std::vector< OperandInfo > | dstOps |

Private Member Functions | |

| bool | hasSecondDword (InFmt_VOP3P *) |

| template<typename T > | |

| T | word (uint32_t data, int opSel, int neg, int opSelBit) |

Additional Inherited Members | |

Public Types inherited from gem5::GPUStaticInst Public Types inherited from gem5::GPUStaticInst | |

| enum | OpType { SRC_VEC , SRC_SCALAR , DST_VEC , DST_SCALAR } |

| typedef int(RegisterManager::* | MapRegFn) (Wavefront *, int) |

Public Attributes inherited from gem5::GPUStaticInst Public Attributes inherited from gem5::GPUStaticInst | |

| enums::StorageClassType | executed_as |

Static Public Attributes inherited from gem5::GPUStaticInst Static Public Attributes inherited from gem5::GPUStaticInst | |

| static uint64_t | dynamic_id_count |

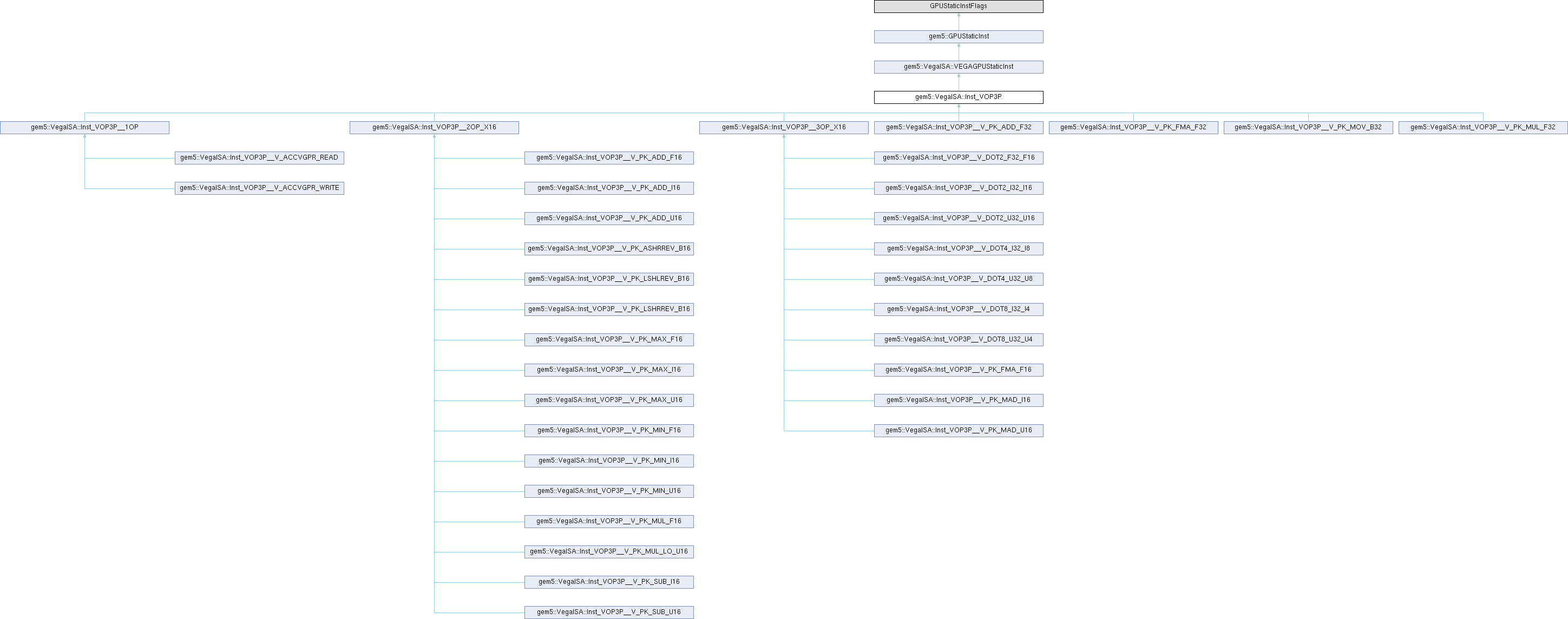

Detailed Description

Definition at line 671 of file op_encodings.hh.

Constructor & Destructor Documentation

◆ Inst_VOP3P()

| gem5::VegaISA::Inst_VOP3P::Inst_VOP3P | ( | InFmt_VOP3P * | iFmt, |

| const std::string & | opcode | ||

| ) |

Definition at line 1183 of file op_encodings.cc.

◆ ~Inst_VOP3P()

| gem5::VegaISA::Inst_VOP3P::~Inst_VOP3P | ( | ) |

Definition at line 1192 of file op_encodings.cc.

Member Function Documentation

◆ dotHelper()

|

inlineprotected |

Definition at line 769 of file op_encodings.hh.

References gem5::VegaISA::InFmt_VOP3P::CLMP, gem5::Wavefront::execMask(), extData, instData, gem5::VegaISA::InFmt_VOP3P_1::NEG, gem5::VegaISA::InFmt_VOP3P::NEG_HI, gem5::ArmISA::NumVecElemPerVecReg, gem5::VegaISA::InFmt_VOP3P::OPSEL, gem5::VegaISA::InFmt_VOP3P_1::OPSEL_HI, gem5::VegaISA::InFmt_VOP3P_1::SRC0, gem5::VegaISA::InFmt_VOP3P_1::SRC1, gem5::VegaISA::InFmt_VOP3P_1::SRC2, gem5::VegaISA::InFmt_VOP3P::VDST, and gem5::VegaISA::VecOperand< DataType, Const, NumDwords >::write().

Referenced by gem5::VegaISA::Inst_VOP3P__V_DOT2_F32_F16::execute(), gem5::VegaISA::Inst_VOP3P__V_DOT2_I32_I16::execute(), gem5::VegaISA::Inst_VOP3P__V_DOT2_U32_U16::execute(), gem5::VegaISA::Inst_VOP3P__V_DOT4_I32_I8::execute(), gem5::VegaISA::Inst_VOP3P__V_DOT4_U32_U8::execute(), gem5::VegaISA::Inst_VOP3P__V_DOT8_I32_I4::execute(), and gem5::VegaISA::Inst_VOP3P__V_DOT8_U32_U4::execute().

◆ generateDisassembly()

|

overridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 1230 of file op_encodings.cc.

References gem5::GPUStaticInst::_opcode, gem5::bits(), gem5::GPUStaticInst::disassembly, extData, gem5::VegaISA::VEGAGPUStaticInst::getOperandSize(), instData, gem5::GPUStaticInst::numSrcRegOperands(), gem5::VegaISA::InFmt_VOP3P::OPSEL, gem5::VegaISA::opSelectorToRegSym(), gem5::VegaISA::InFmt_VOP3P_1::SRC0, gem5::VegaISA::InFmt_VOP3P_1::SRC1, gem5::VegaISA::InFmt_VOP3P_1::SRC2, and gem5::VegaISA::InFmt_VOP3P::VDST.

◆ hasSecondDword()

|

private |

◆ initOperandInfo()

|

overridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 1197 of file op_encodings.cc.

References gem5::GPUStaticInst::dstOps, extData, gem5::VegaISA::VEGAGPUStaticInst::getOperandSize(), instData, gem5::VegaISA::isScalarReg(), gem5::VegaISA::isVectorReg(), gem5::GPUStaticInst::numDstRegOperands(), gem5::GPUStaticInst::numSrcRegOperands(), gem5::X86ISA::reg, gem5::VegaISA::InFmt_VOP3P_1::SRC0, gem5::VegaISA::InFmt_VOP3P_1::SRC1, gem5::VegaISA::InFmt_VOP3P_1::SRC2, gem5::GPUStaticInst::srcOps, and gem5::VegaISA::InFmt_VOP3P::VDST.

◆ instSize()

|

overridevirtual |

Implements gem5::GPUStaticInst.

Definition at line 1224 of file op_encodings.cc.

◆ vop3pHelper() [1/2]

|

inlineprotected |

Definition at line 689 of file op_encodings.hh.

References gem5::VegaISA::InFmt_VOP3P::CLMP, gem5::Wavefront::execMask(), extData, instData, gem5::VegaISA::InFmt_VOP3P_1::NEG, gem5::VegaISA::InFmt_VOP3P::NEG_HI, gem5::ArmISA::NumVecElemPerVecReg, gem5::VegaISA::InFmt_VOP3P::OPSEL, gem5::VegaISA::InFmt_VOP3P_1::OPSEL_HI, gem5::VegaISA::InFmt_VOP3P::OPSEL_HI2, gem5::VegaISA::InFmt_VOP3P_1::SRC0, gem5::VegaISA::InFmt_VOP3P_1::SRC1, gem5::VegaISA::InFmt_VOP3P::VDST, and gem5::VegaISA::VecOperand< DataType, Const, NumDwords >::write().

◆ vop3pHelper() [2/2]

|

inlineprotected |

Definition at line 727 of file op_encodings.hh.

References gem5::VegaISA::InFmt_VOP3P::CLMP, gem5::Wavefront::execMask(), extData, instData, gem5::VegaISA::InFmt_VOP3P_1::NEG, gem5::VegaISA::InFmt_VOP3P::NEG_HI, gem5::ArmISA::NumVecElemPerVecReg, gem5::VegaISA::InFmt_VOP3P::OPSEL, gem5::VegaISA::InFmt_VOP3P_1::OPSEL_HI, gem5::VegaISA::InFmt_VOP3P::OPSEL_HI2, gem5::VegaISA::InFmt_VOP3P_1::SRC0, gem5::VegaISA::InFmt_VOP3P_1::SRC1, gem5::VegaISA::InFmt_VOP3P_1::SRC2, gem5::VegaISA::InFmt_VOP3P::VDST, and gem5::VegaISA::VecOperand< DataType, Const, NumDwords >::write().

◆ word()

|

inlineprivate |

Definition at line 823 of file op_encodings.hh.

References gem5::bits(), and data.

Member Data Documentation

◆ extData

|

protected |

Definition at line 686 of file op_encodings.hh.

Referenced by dotHelper(), gem5::VegaISA::Inst_VOP3P__V_ACCVGPR_READ::execute(), gem5::VegaISA::Inst_VOP3P__V_ACCVGPR_WRITE::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_FMA_F32::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_MUL_F32::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_ADD_F32::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_MOV_B32::execute(), generateDisassembly(), initOperandInfo(), Inst_VOP3P(), vop3pHelper(), and vop3pHelper().

◆ instData

|

protected |

Definition at line 684 of file op_encodings.hh.

Referenced by dotHelper(), gem5::VegaISA::Inst_VOP3P__V_ACCVGPR_READ::execute(), gem5::VegaISA::Inst_VOP3P__V_ACCVGPR_WRITE::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_FMA_F32::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_MUL_F32::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_ADD_F32::execute(), gem5::VegaISA::Inst_VOP3P__V_PK_MOV_B32::execute(), generateDisassembly(), initOperandInfo(), Inst_VOP3P(), vop3pHelper(), and vop3pHelper().

The documentation for this class was generated from the following files:

- arch/amdgpu/vega/insts/op_encodings.hh

- arch/amdgpu/vega/insts/op_encodings.cc