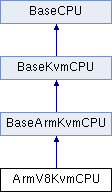

This is an implementation of a KVM-based ARMv8-compatible CPU. More...

#include <armv8_cpu.hh>

Classes | |

| struct | IntRegInfo |

| Mapping between integer registers in gem5 and KVM. More... | |

| struct | MiscRegInfo |

| Mapping between misc registers in gem5 and registers in KVM. More... | |

Public Member Functions | |

| ArmV8KvmCPU (ArmV8KvmCPUParams *params) | |

| virtual | ~ArmV8KvmCPU () |

| void | startup () override |

| void | dump () const override |

| Dump the internal state to the terminal. More... | |

Public Member Functions inherited from BaseArmKvmCPU Public Member Functions inherited from BaseArmKvmCPU | |

| BaseArmKvmCPU (BaseArmKvmCPUParams *params) | |

| virtual | ~BaseArmKvmCPU () |

| void | startup () override |

Public Member Functions inherited from BaseKvmCPU Public Member Functions inherited from BaseKvmCPU | |

| BaseKvmCPU (BaseKvmCPUParams *params) | |

| virtual | ~BaseKvmCPU () |

| void | init () override |

| void | startup () override |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| Serialize a single thread. More... | |

| void | unserializeThread (CheckpointIn &cp, ThreadID tid) override |

| Unserialize one thread. More... | |

| DrainState | drain () override |

| void | drainResume () override |

| void | notifyFork () override |

| void | switchOut () override |

| Prepare for another CPU to take over execution. More... | |

| void | takeOverFrom (BaseCPU *cpu) override |

| Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in. More... | |

| void | verifyMemoryMode () const override |

| Verify that the system is in a memory mode supported by the CPU. More... | |

| Port & | getDataPort () override |

| Purely virtual method that returns a reference to the data port. More... | |

| Port & | getInstPort () override |

| Purely virtual method that returns a reference to the instruction port. More... | |

| void | wakeup (ThreadID tid=0) override |

| void | activateContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now active. More... | |

| void | suspendContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now suspended. More... | |

| void | deallocateContext (ThreadID thread_num) |

| void | haltContext (ThreadID thread_num) override |

| Notify the CPU that the indicated context is now halted. More... | |

| long | getVCpuID () const |

| ThreadContext * | getContext (int tn) override |

| Given a thread num get tho thread context for it. More... | |

| Counter | totalInsts () const override |

| Counter | totalOps () const override |

| void | finishMMIOPending () |

| Callback from KvmCPUPort to transition the CPU out of RunningMMIOPending when all timing requests have completed. More... | |

| void | kick () const |

| Force an exit from KVM. More... | |

Public Member Functions inherited from BaseCPU Public Member Functions inherited from BaseCPU | |

| virtual PortProxy::SendFunctionalFunc | getSendFunctional () |

| Returns a sendFunctional delegate for use with port proxies. More... | |

| int | cpuId () const |

| Reads this CPU's ID. More... | |

| uint32_t | socketId () const |

| Reads this CPU's Socket ID. More... | |

| RequestorID | dataRequestorId () const |

| Reads this CPU's unique data requestor ID. More... | |

| RequestorID | instRequestorId () const |

| Reads this CPU's unique instruction requestor ID. More... | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. More... | |

| uint32_t | taskId () const |

| Get cpu task id. More... | |

| void | taskId (uint32_t id) |

| Set cpu task id. More... | |

| uint32_t | getPid () const |

| void | setPid (uint32_t pid) |

| void | workItemBegin () |

| void | workItemEnd () |

| Tick | instCount () |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupts (ThreadID tid) |

| bool | checkInterrupts (ThreadID tid) const |

| Trace::InstTracer * | getTracer () |

| Provide access to the tracer pointer. More... | |

| int | findContext (ThreadContext *tc) |

| Given a Thread Context pointer return the thread num. More... | |

| unsigned | numContexts () |

| Get the number of thread contexts available. More... | |

| ThreadID | contextToThread (ContextID cid) |

| Convert ContextID to threadID. More... | |

| const Params * | params () const |

| BaseCPU (Params *params, bool is_checker=false) | |

| virtual | ~BaseCPU () |

| void | init () override |

| void | startup () override |

| void | regStats () override |

| void | regProbePoints () override |

| void | registerThreadContexts () |

| void | deschedulePowerGatingEvent () |

| void | schedulePowerGatingEvent () |

| void | flushTLBs () |

| Flush all TLBs in the CPU. More... | |

| bool | switchedOut () const |

| Determine if the CPU is switched out. More... | |

| unsigned int | cacheLineSize () const |

| Get the cache line size of the system. More... | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. More... | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. More... | |

| void | scheduleInstStop (ThreadID tid, Counter insts, const char *cause) |

| Schedule an event that exits the simulation loops after a predefined number of instructions. More... | |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| Get the number of instructions executed by the specified thread on this CPU. More... | |

| void | traceFunctions (Addr pc) |

| void | armMonitor (ThreadID tid, Addr address) |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseTLB *dtb) |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| bool | waitForRemoteGDB () const |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| Helper method to trigger PMU probes for a committed instruction. More... | |

Protected Member Functions | |

| void | updateKvmState () override |

| Update the KVM state from the current thread context. More... | |

| void | updateThreadContext () override |

| Update the current thread context with the KVM state. More... | |

| const std::vector< ArmV8KvmCPU::MiscRegInfo > & | getSysRegMap () const |

| Get a map between system registers in kvm and gem5 registers. More... | |

Protected Member Functions inherited from BaseArmKvmCPU Protected Member Functions inherited from BaseArmKvmCPU | |

| Tick | kvmRun (Tick ticks) override |

| Request KVM to run the guest for a given number of ticks. More... | |

| const RegIndexVector & | getRegList () const |

| Get a list of registers supported by getOneReg() and setOneReg(). More... | |

| void | kvmArmVCpuInit (const struct kvm_vcpu_init &init) |

| Tell the kernel to initialize this CPU. More... | |

Protected Member Functions inherited from BaseKvmCPU Protected Member Functions inherited from BaseKvmCPU | |

| void | tick () |

| Execute the CPU until the next event in the main event queue or until the guest needs service from gem5. More... | |

| virtual uint64_t | getHostCycles () const |

| Get the value of the hardware cycle counter in the guest. More... | |

| virtual Tick | kvmRunDrain () |

| Request the CPU to run until draining completes. More... | |

| struct kvm_run * | getKvmRunState () |

| Get a pointer to the kvm_run structure containing all the input and output parameters from kvmRun(). More... | |

| uint8_t * | getGuestData (uint64_t offset) const |

| Retrieve a pointer to guest data stored at the end of the kvm_run structure. More... | |

| void | kvmNonMaskableInterrupt () |

| Send a non-maskable interrupt to the guest. More... | |

| void | kvmInterrupt (const struct kvm_interrupt &interrupt) |

| Send a normal interrupt to the guest. More... | |

| std::string | getAndFormatOneReg (uint64_t id) const |

| Get and format one register for printout. More... | |

| virtual bool | archIsDrained () const |

| Is the architecture specific code in a state that prevents draining? More... | |

| Tick | doMMIOAccess (Addr paddr, void *data, int size, bool write) |

| Inject a memory mapped IO request into gem5. More... | |

| int | ioctl (int request, long p1) const |

| vCPU ioctl interface. More... | |

| int | ioctl (int request, void *p1) const |

| int | ioctl (int request) const |

| void | getRegisters (struct kvm_regs ®s) const |

| Get/Set the register state of the guest vCPU. More... | |

| void | setRegisters (const struct kvm_regs ®s) |

| void | getSpecialRegisters (struct kvm_sregs ®s) const |

| void | setSpecialRegisters (const struct kvm_sregs ®s) |

| void | getFPUState (struct kvm_fpu &state) const |

| Get/Set the guest FPU/vector state. More... | |

| void | setFPUState (const struct kvm_fpu &state) |

| void | setOneReg (uint64_t id, const void *addr) |

| Get/Set single register using the KVM_(SET|GET)_ONE_REG API. More... | |

| void | setOneReg (uint64_t id, uint64_t value) |

| void | setOneReg (uint64_t id, uint32_t value) |

| void | getOneReg (uint64_t id, void *addr) const |

| uint64_t | getOneRegU64 (uint64_t id) const |

| uint32_t | getOneRegU32 (uint64_t id) const |

| void | syncThreadContext () |

| Update a thread context if the KVM state is dirty with respect to the cached thread context. More... | |

| EventQueue * | deviceEventQueue () |

| Get a pointer to the event queue owning devices. More... | |

| void | syncKvmState () |

| Update the KVM if the thread context is dirty. More... | |

| virtual Tick | handleKvmExit () |

| Main kvmRun exit handler, calls the relevant handleKvmExit* depending on exit type. More... | |

| virtual Tick | handleKvmExitIO () |

| The guest performed a legacy IO request (out/inp on x86) More... | |

| virtual Tick | handleKvmExitHypercall () |

| The guest requested a monitor service using a hypercall. More... | |

| virtual Tick | handleKvmExitIRQWindowOpen () |

| The guest exited because an interrupt window was requested. More... | |

| virtual Tick | handleKvmExitUnknown () |

| An unknown architecture dependent error occurred when starting the vCPU. More... | |

| virtual Tick | handleKvmExitException () |

| An unhandled virtualization exception occured. More... | |

| virtual Tick | handleKvmExitFailEntry () |

| KVM failed to start the virtualized CPU. More... | |

| void | setSignalMask (const sigset_t *mask) |

| Set the signal mask used in kvmRun() More... | |

Protected Member Functions inherited from BaseCPU Protected Member Functions inherited from BaseCPU | |

| void | updateCycleCounters (CPUState state) |

| base method keeping track of cycle progression More... | |

| void | enterPwrGating () |

| ProbePoints::PMUUPtr | pmuProbePoint (const char *name) |

| Helper method to instantiate probe points belonging to this object. More... | |

Protected Attributes | |

| std::vector< ArmV8KvmCPU::MiscRegInfo > | sysRegMap |

| Cached mapping between system registers in kvm and misc regs in gem5. More... | |

Protected Attributes inherited from BaseArmKvmCPU Protected Attributes inherited from BaseArmKvmCPU | |

| bool | irqAsserted |

| Cached state of the IRQ line. More... | |

| bool | fiqAsserted |

| Cached state of the FIQ line. More... | |

| ArmInterruptPin * | virtTimerPin |

| If the user-space GIC and the kernel-space timer are used simultaneously, set up this interrupt pin to forward interrupt from the timer to the GIC when timer IRQ level change is intercepted. More... | |

| uint64_t | prevDeviceIRQLevel |

| KVM records whether each in-kernel device IRQ is asserted or disasserted in the kvmRunState->s.regs.device_irq_level bit map, and guarantees at least one KVM exit when the level changes. More... | |

Protected Attributes inherited from BaseKvmCPU Protected Attributes inherited from BaseKvmCPU | |

| Status | _status |

| CPU run state. More... | |

| KVMCpuPort | dataPort |

| Port for data requests. More... | |

| KVMCpuPort | instPort |

| Unused dummy port for the instruction interface. More... | |

| const bool | alwaysSyncTC |

| Be conservative and always synchronize the thread context on KVM entry/exit. More... | |

| bool | threadContextDirty |

| Is the gem5 context dirty? Set to true to force an update of the KVM vCPU state upon the next call to kvmRun(). More... | |

| bool | kvmStateDirty |

| Is the KVM state dirty? Set to true to force an update of the KVM vCPU state upon the next call to kvmRun(). More... | |

| const long | vcpuID |

| KVM internal ID of the vCPU. More... | |

| pthread_t | vcpuThread |

| ID of the vCPU thread. More... | |

Protected Attributes inherited from BaseCPU Protected Attributes inherited from BaseCPU | |

| Tick | instCnt |

| Instruction count used for SPARC misc register. More... | |

| int | _cpuId |

| const uint32_t | _socketId |

| Each cpu will have a socket ID that corresponds to its physical location in the system. More... | |

| RequestorID | _instRequestorId |

| instruction side request id that must be placed in all requests More... | |

| RequestorID | _dataRequestorId |

| data side request id that must be placed in all requests More... | |

| uint32_t | _taskId |

| An intrenal representation of a task identifier within gem5. More... | |

| uint32_t | _pid |

| The current OS process ID that is executing on this processor. More... | |

| bool | _switchedOut |

| Is the CPU switched out or active? More... | |

| const unsigned int | _cacheLineSize |

| Cache the cache line size that we get from the system. More... | |

| std::vector< BaseInterrupts * > | interrupts |

| std::vector< ThreadContext * > | threadContexts |

| Trace::InstTracer * | tracer |

| Cycles | previousCycle |

| CPUState | previousState |

| const Cycles | pwrGatingLatency |

| const bool | powerGatingOnIdle |

| EventFunctionWrapper | enterPwrGatingEvent |

| ProbePoints::PMUUPtr | ppRetiredInsts |

| Instruction commit probe point. More... | |

| ProbePoints::PMUUPtr | ppRetiredInstsPC |

| ProbePoints::PMUUPtr | ppRetiredLoads |

| Retired load instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredStores |

| Retired store instructions. More... | |

| ProbePoints::PMUUPtr | ppRetiredBranches |

| Retired branches (any type) More... | |

| ProbePoints::PMUUPtr | ppAllCycles |

| CPU cycle counter even if any thread Context is suspended. More... | |

| ProbePoints::PMUUPtr | ppActiveCycles |

| CPU cycle counter, only counts if any thread contexts is active. More... | |

| ProbePointArg< bool > * | ppSleeping |

| ProbePoint that signals transitions of threadContexts sets. More... | |

Static Protected Attributes | |

| static const std::vector< ArmV8KvmCPU::IntRegInfo > | intRegMap |

| Mapping between gem5 integer registers and integer registers in kvm. More... | |

| static const std::vector< ArmV8KvmCPU::MiscRegInfo > | miscRegMap |

| Mapping between gem5 misc registers and registers in kvm. More... | |

| static const std::set< ArmISA::MiscRegIndex > | deviceRegSet |

| Device registers (needing "effectful" MiscReg writes) More... | |

| static const std::vector< ArmV8KvmCPU::MiscRegInfo > | miscRegIdMap |

| Mapping between gem5 ID misc registers and registers in kvm. More... | |

Additional Inherited Members | |

Public Types inherited from BaseCPU Public Types inherited from BaseCPU | |

| typedef BaseCPUParams | Params |

Static Public Member Functions inherited from BaseCPU Static Public Member Functions inherited from BaseCPU | |

| static int | numSimulatedInsts () |

| static int | numSimulatedOps () |

| static void | wakeup (ThreadID tid) |

| static int | numSimulatedCPUs () |

| static Counter | numSimulatedInsts () |

| static Counter | numSimulatedOps () |

Public Attributes inherited from BaseKvmCPU Public Attributes inherited from BaseKvmCPU | |

| SimpleThread * | thread |

| A cached copy of a thread's state in the form of a SimpleThread object. More... | |

| ThreadContext * | tc |

| ThreadContext object, provides an interface for external objects to modify this thread's state. More... | |

| KvmVM & | vm |

| BaseKvmCPU::StatGroup | stats |

| Counter | ctrInsts |

| Number of instructions executed by the CPU. More... | |

Public Attributes inherited from BaseCPU Public Attributes inherited from BaseCPU | |

| ThreadID | numThreads |

| Number of threads we're actually simulating (<= SMT_MAX_THREADS). More... | |

| System * | system |

| Stats::Scalar | numCycles |

| Stats::Scalar | numWorkItemsStarted |

| Stats::Scalar | numWorkItemsCompleted |

| Cycles | syscallRetryLatency |

Static Public Attributes inherited from BaseCPU Static Public Attributes inherited from BaseCPU | |

| static const uint32_t | invldPid = std::numeric_limits<uint32_t>::max() |

| Invalid or unknown Pid. More... | |

| static const Addr | PCMask = ~((Addr)sizeof(TheISA::MachInst) - 1) |

Protected Types inherited from BaseArmKvmCPU Protected Types inherited from BaseArmKvmCPU | |

| typedef std::vector< uint64_t > | RegIndexVector |

Protected Types inherited from BaseKvmCPU Protected Types inherited from BaseKvmCPU | |

| enum | Status { Idle, Running, RunningService, RunningMMIOPending, RunningServiceCompletion } |

Protected Types inherited from BaseCPU Protected Types inherited from BaseCPU | |

| enum | CPUState { CPU_STATE_ON, CPU_STATE_SLEEP, CPU_STATE_WAKEUP } |

Detailed Description

This is an implementation of a KVM-based ARMv8-compatible CPU.

Known limitations:

-

The system-register-based generic timer can only be simulated by the host kernel. Workaround: Use a memory mapped timer instead to simulate the timer in gem5.

-

Simulating devices (e.g., the generic timer) in the host kernel requires that the host kernel also simulates the GIC.

-

ID registers in the host and in gem5 must match for switching between simulated CPUs and KVM. This is particularly important for ID registers describing memory system capabilities (e.g., ASID size, physical address size).

-

Switching between a virtualized CPU and a simulated CPU is currently not supported if in-kernel device emulation is used. This could be worked around by adding support for switching to the gem5 (e.g., the KvmGic) side of the device models. A simpler workaround is to avoid in-kernel device models altogether.

Definition at line 79 of file armv8_cpu.hh.

Constructor & Destructor Documentation

◆ ArmV8KvmCPU()

| ArmV8KvmCPU::ArmV8KvmCPU | ( | ArmV8KvmCPUParams * | params | ) |

Definition at line 126 of file armv8_cpu.cc.

◆ ~ArmV8KvmCPU()

|

virtual |

Definition at line 131 of file armv8_cpu.cc.

Member Function Documentation

◆ dump()

|

overridevirtual |

Dump the internal state to the terminal.

Reimplemented from BaseKvmCPU.

Definition at line 149 of file armv8_cpu.cc.

References ArmISA::decodeAArch64SysReg(), EXTRACT_FIELD, BaseKvmCPU::getAndFormatOneReg(), BaseArmKvmCPU::getRegList(), ArmISA::i, ArmISA::id, inform, INT_REG, intRegMap, kvmFPReg(), kvmXReg(), miscRegIdMap, miscRegMap, ArmISA::miscRegName, NUM_QREGS, NUM_XREGS, X86ISA::reg, type, and X86ISA::val.

◆ getSysRegMap()

|

protected |

Get a map between system registers in kvm and gem5 registers.

This method returns a mapping between system registers in kvm and misc regs in gem5. The actual mapping is only created the first time the method is called and stored in a cache (ArmV8KvmCPU::sysRegMap).

- Returns

- Vector of kvm<->misc reg mappings.

Definition at line 359 of file armv8_cpu.cc.

References ArmISA::decodeAArch64SysReg(), deviceRegSet, EXTRACT_FIELD, BaseArmKvmCPU::getRegList(), ArmISA::MISCREG_HYP_WR, ArmISA::MISCREG_IMPLEMENTED, ArmISA::MISCREG_MON_NS0_WR, ArmISA::MISCREG_MON_NS1_WR, ArmISA::MISCREG_PRI_NS_WR, ArmISA::MISCREG_PRI_S_WR, ArmISA::MISCREG_USR_NS_WR, ArmISA::MISCREG_USR_S_WR, ArmISA::MISCREG_WARN_NOT_FAIL, ArmISA::miscRegInfo, ArmISA::miscRegName, X86ISA::reg, sysRegMap, and type.

Referenced by updateKvmState(), and updateThreadContext().

◆ startup()

|

override |

Definition at line 136 of file armv8_cpu.cc.

References DPRINTF, miscRegIdMap, ThreadContext::readMiscReg(), BaseKvmCPU::setOneReg(), BaseArmKvmCPU::startup(), and BaseKvmCPU::tc.

◆ updateKvmState()

|

overrideprotectedvirtual |

Update the KVM state from the current thread context.

The base CPU calls this method before starting the guest CPU when the contextDirty flag is set. The architecture dependent CPU implementation is expected to update all guest state (registers, special registers, and FPU state).

Implements BaseKvmCPU.

Definition at line 216 of file armv8_cpu.cc.

References VecRegContainer< SIZE >::as(), ArmISA::CCREG_C, ArmISA::CCREG_GE, ArmISA::CCREG_NZ, ArmISA::CCREG_V, BaseKvmCPU::deviceEventQueue(), DPRINTF, FP_REGS_PER_VFP_REG, BaseKvmCPU::getAndFormatOneReg(), getSysRegMap(), ArmISA::i, ThreadContext::instAddr(), INT_REG, ArmISA::INTREG_X0, intRegMap, ArmISA::j, kvmFPReg(), kvmXReg(), ArmISA::MISCREG_CPSR, miscRegMap, NUM_QREGS, NUM_XREGS, ThreadContext::readCCReg(), ThreadContext::readIntReg(), ThreadContext::readMiscReg(), ThreadContext::readVecReg(), X86ISA::reg, BaseKvmCPU::setOneReg(), BaseKvmCPU::tc, ArmISA::v, and VecRegClass.

◆ updateThreadContext()

|

overrideprotectedvirtual |

Update the current thread context with the KVM state.

The base CPU after the guest updates any of the KVM state. In practice, this happens after kvmRun is called. The architecture dependent code is expected to read the state of the guest CPU and update gem5's thread state.

Implements BaseKvmCPU.

Definition at line 282 of file armv8_cpu.cc.

References VecRegContainer< SIZE >::as(), ArmISA::CCREG_C, ArmISA::CCREG_GE, ArmISA::CCREG_NZ, ArmISA::CCREG_V, BaseKvmCPU::deviceEventQueue(), DPRINTF, FP_REGS_PER_VFP_REG, BaseKvmCPU::getAndFormatOneReg(), BaseKvmCPU::getOneReg(), BaseKvmCPU::getOneRegU64(), getSysRegMap(), ThreadContext::getWritableVecReg(), ArmISA::i, ArmISA::inAArch64(), INT_REG, ArmISA::IntReg64Map, ArmISA::INTREG_X0, intRegMap, ArmISA::j, kvmFPReg(), kvmXReg(), ArmISA::MISCREG_CPSR, miscRegMap, NUM_QREGS, NUM_XREGS, MipsISA::pc, ThreadContext::pcState(), X86ISA::reg, ThreadContext::setCCReg(), ThreadContext::setIntReg(), ThreadContext::setIntRegFlat(), ThreadContext::setMiscReg(), ThreadContext::setMiscRegNoEffect(), BaseKvmCPU::tc, ArmISA::v, and VecRegClass.

Member Data Documentation

◆ deviceRegSet

|

staticprotected |

Device registers (needing "effectful" MiscReg writes)

Definition at line 140 of file armv8_cpu.hh.

Referenced by getSysRegMap().

◆ intRegMap

|

staticprotected |

Mapping between gem5 integer registers and integer registers in kvm.

Definition at line 136 of file armv8_cpu.hh.

Referenced by dump(), updateKvmState(), and updateThreadContext().

◆ miscRegIdMap

|

staticprotected |

Mapping between gem5 ID misc registers and registers in kvm.

Definition at line 142 of file armv8_cpu.hh.

◆ miscRegMap

|

staticprotected |

Mapping between gem5 misc registers and registers in kvm.

Definition at line 138 of file armv8_cpu.hh.

Referenced by dump(), updateKvmState(), and updateThreadContext().

◆ sysRegMap

|

mutableprotected |

Cached mapping between system registers in kvm and misc regs in gem5.

Definition at line 145 of file armv8_cpu.hh.

Referenced by getSysRegMap().

The documentation for this class was generated from the following files:

- arch/arm/kvm/armv8_cpu.hh

- arch/arm/kvm/armv8_cpu.cc