#include <dyn_inst.hh>

Public Types | |

| enum | { MaxInstSrcRegs = TheISA::MaxInstSrcRegs, MaxInstDestRegs = TheISA::MaxInstDestRegs } |

| typedef Impl::O3CPU | O3CPU |

| Typedef for the CPU. More... | |

| typedef TheISA::MachInst | MachInst |

| Binary machine instruction type. More... | |

| using | VecRegContainer = TheISA::VecRegContainer |

| Register types. More... | |

| using | VecElem = TheISA::VecElem |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

Public Types inherited from BaseDynInst< Impl > Public Types inherited from BaseDynInst< Impl > | |

| enum | { MaxInstSrcRegs = TheISA::MaxInstSrcRegs, MaxInstDestRegs = TheISA::MaxInstDestRegs } |

| typedef Impl::CPUType | ImplCPU |

| typedef ImplCPU::ImplState | ImplState |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | LSQRequestPtr = typename Impl::CPUPol::LSQ::LSQRequest * |

| using | LQIterator = typename Impl::CPUPol::LSQUnit::LQIterator |

| using | SQIterator = typename Impl::CPUPol::LSQUnit::SQIterator |

| typedef Impl::DynInstPtr | DynInstPtr |

| typedef RefCountingPtr< BaseDynInst< Impl > > | BaseDynInstPtr |

| typedef std::list< DynInstPtr >::iterator | ListIt |

Public Types inherited from ExecContext Public Types inherited from ExecContext | |

| typedef TheISA::PCState | PCState |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | VecElem = TheISA::VecElem |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

Public Member Functions | |

| BaseO3DynInst (const StaticInstPtr &staticInst, const StaticInstPtr ¯oop, TheISA::PCState pc, TheISA::PCState predPC, InstSeqNum seq_num, O3CPU *cpu) | |

| BaseDynInst constructor given a binary instruction. More... | |

| BaseO3DynInst (const StaticInstPtr &_staticInst, const StaticInstPtr &_macroop) | |

| BaseDynInst constructor given a static inst pointer. More... | |

| ~BaseO3DynInst () | |

| Fault | execute () |

| Executes the instruction. More... | |

| Fault | initiateAcc () |

| Initiates the access. More... | |

| Fault | completeAcc (PacketPtr pkt) |

| Completes the access. More... | |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a misc. More... | |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a misc. More... | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| Reads a misc. More... | |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| Sets a misc. More... | |

| void | updateMiscRegs () |

| Called at the commit stage to update the misc. More... | |

| void | forwardOldRegs () |

| void | trap (const Fault &fault) |

| Traps to handle specified fault. More... | |

| void | syscall () override |

| Emulates a syscall. More... | |

| RegVal | readIntRegOperand (const StaticInst *si, int idx) override |

| Reads an integer register. More... | |

| RegVal | readFloatRegOperandBits (const StaticInst *si, int idx) override |

| Reads a floating point register in its binary format, instead of by value. More... | |

| const VecRegContainer & | readVecRegOperand (const StaticInst *si, int idx) const override |

| Vector Register Interfaces. More... | |

| VecRegContainer & | getWritableVecRegOperand (const StaticInst *si, int idx) override |

| Read destination vector register operand for modification. More... | |

| VecElem | readVecElemOperand (const StaticInst *si, int idx) const override |

| Vector Elem Interfaces. More... | |

| const VecPredRegContainer & | readVecPredRegOperand (const StaticInst *si, int idx) const override |

| Predicate registers interface. More... | |

| VecPredRegContainer & | getWritableVecPredRegOperand (const StaticInst *si, int idx) override |

| Gets destination predicate register operand for modification. More... | |

| RegVal | readCCRegOperand (const StaticInst *si, int idx) override |

| void | setIntRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setFloatRegOperandBits (const StaticInst *si, int idx, RegVal val) override |

| Records an fp register being set to an integer value. More... | |

| void | setVecRegOperand (const StaticInst *si, int idx, const VecRegContainer &val) override |

| Record a vector register being set to a value. More... | |

| void | setVecElemOperand (const StaticInst *si, int idx, const VecElem val) override |

| Record a vector register being set to a value. More... | |

| void | setVecPredRegOperand (const StaticInst *si, int idx, const VecPredRegContainer &val) override |

| Record a vector register being set to a value. More... | |

| void | setCCRegOperand (const StaticInst *si, int idx, RegVal val) override |

| Records a CC register being set to a value. More... | |

| ConstVecLane8 | readVec8BitLaneOperand (const StaticInst *si, int idx) const override |

| Vector Register Lane Interfaces. More... | |

| ConstVecLane16 | readVec16BitLaneOperand (const StaticInst *si, int idx) const override |

| Reads source vector 16bit operand. More... | |

| ConstVecLane32 | readVec32BitLaneOperand (const StaticInst *si, int idx) const override |

| Reads source vector 32bit operand. More... | |

| ConstVecLane64 | readVec64BitLaneOperand (const StaticInst *si, int idx) const override |

| Reads source vector 64bit operand. More... | |

| template<typename LD > | |

| void | setVecLaneOperandT (const StaticInst *si, int idx, const LD &val) |

| Write a lane of the destination vector operand. More... | |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::Byte > &val) override |

| Write a lane of the destination vector operand. More... | |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::TwoByte > &val) override |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::FourByte > &val) override |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::EightByte > &val) override |

Public Member Functions inherited from BaseDynInst< Impl > Public Member Functions inherited from BaseDynInst< Impl > | |

| BaseCPU * | getCpuPtr () |

| void | recordResult (bool f) |

| Records changes to result? More... | |

| bool | effAddrValid () const |

| Is the effective virtual address valid. More... | |

| void | effAddrValid (bool b) |

| bool | memOpDone () const |

| Whether or not the memory operation is done. More... | |

| void | memOpDone (bool f) |

| bool | notAnInst () const |

| void | setNotAnInst () |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. More... | |

| void | demapInstPage (Addr vaddr, uint64_t asn) |

| void | demapDataPage (Addr vaddr, uint64_t asn) |

| Fault | initiateMemRead (Addr addr, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | initiateHtmCmd (Request::Flags flags) override |

| Initiate an HTM command, e.g. More... | |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | initiateMemAMO (Addr addr, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| bool | translationStarted () const |

| True if the DTB address translation has started. More... | |

| void | translationStarted (bool f) |

| bool | translationCompleted () const |

| True if the DTB address translation has completed. More... | |

| void | translationCompleted (bool f) |

| bool | possibleLoadViolation () const |

| True if this address was found to match a previous load and they issued out of order. More... | |

| void | possibleLoadViolation (bool f) |

| bool | hitExternalSnoop () const |

| True if the address hit a external snoop while sitting in the LSQ. More... | |

| void | hitExternalSnoop (bool f) |

| bool | isTranslationDelayed () const |

| Returns true if the DTB address translation is being delayed due to a hw page table walk. More... | |

| PhysRegIdPtr | renamedDestRegIdx (int idx) const |

| Returns the physical register index of the i'th destination register. More... | |

| PhysRegIdPtr | renamedSrcRegIdx (int idx) const |

| Returns the physical register index of the i'th source register. More... | |

| const RegId & | flattenedDestRegIdx (int idx) const |

| Returns the flattened register index of the i'th destination register. More... | |

| PhysRegIdPtr | prevDestRegIdx (int idx) const |

| Returns the physical register index of the previous physical register that remapped to the same logical register index. More... | |

| void | renameDestReg (int idx, PhysRegIdPtr renamed_dest, PhysRegIdPtr previous_rename) |

| Renames a destination register to a physical register. More... | |

| void | renameSrcReg (int idx, PhysRegIdPtr renamed_src) |

| Renames a source logical register to the physical register which has/will produce that logical register's result. More... | |

| void | flattenDestReg (int idx, const RegId &flattened_dest) |

| Flattens a destination architectural register index into a logical index. More... | |

| BaseDynInst (const StaticInstPtr &staticInst, const StaticInstPtr ¯oop, TheISA::PCState pc, TheISA::PCState predPC, InstSeqNum seq_num, ImplCPU *cpu) | |

| BaseDynInst constructor given a binary instruction. More... | |

| BaseDynInst (const StaticInstPtr &staticInst, const StaticInstPtr ¯oop) | |

| BaseDynInst constructor given a StaticInst pointer. More... | |

| ~BaseDynInst () | |

| BaseDynInst destructor. More... | |

| void | dump () |

| Dumps out contents of this BaseDynInst. More... | |

| void | dump (std::string &outstring) |

| Dumps out contents of this BaseDynInst into given string. More... | |

| int | cpuId () const |

| Read this CPU's ID. More... | |

| uint32_t | socketId () const |

| Read this CPU's Socket ID. More... | |

| RequestorID | requestorId () const |

| Read this CPU's data requestor ID. More... | |

| ContextID | contextId () const |

| Read this context's system-wide ID. More... | |

| Fault | getFault () const |

| Returns the fault type. More... | |

| Fault & | getFault () |

| TODO: This I added for the LSQRequest side to be able to modify the fault. More... | |

| bool | doneTargCalc () |

| Checks whether or not this instruction has had its branch target calculated yet. More... | |

| void | setPredTarg (const TheISA::PCState &_predPC) |

| Set the predicted target of this current instruction. More... | |

| const TheISA::PCState & | readPredTarg () |

| Addr | predInstAddr () |

| Returns the predicted PC immediately after the branch. More... | |

| Addr | predNextInstAddr () |

| Returns the predicted PC two instructions after the branch. More... | |

| Addr | predMicroPC () |

| Returns the predicted micro PC after the branch. More... | |

| bool | readPredTaken () |

| Returns whether the instruction was predicted taken or not. More... | |

| void | setPredTaken (bool predicted_taken) |

| bool | mispredicted () |

| Returns whether the instruction mispredicted. More... | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isCondDelaySlot () const |

| bool | isThreadSync () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isMemBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isIprAccess () const |

| bool | isUnverifiable () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isMicroBranch () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isHtmCmd () const |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| void | setHtmTransactionalState (uint64_t htm_uid, uint64_t htm_depth) |

| void | clearHtmTransactionalState () |

| void | setSerializeBefore () |

| Temporarily sets this instruction as a serialize before instruction. More... | |

| void | clearSerializeBefore () |

| Clears the serializeBefore part of this instruction. More... | |

| bool | isTempSerializeBefore () |

| Checks if this serializeBefore is only temporarily set. More... | |

| void | setSerializeAfter () |

| Temporarily sets this instruction as a serialize after instruction. More... | |

| void | clearSerializeAfter () |

| Clears the serializeAfter part of this instruction. More... | |

| bool | isTempSerializeAfter () |

| Checks if this serializeAfter is only temporarily set. More... | |

| void | setSerializeHandled () |

| Sets the serialization part of this instruction as handled. More... | |

| bool | isSerializeHandled () |

| Checks if the serialization part of this instruction has been handled. More... | |

| OpClass | opClass () const |

| Returns the opclass of this instruction. More... | |

| TheISA::PCState | branchTarget () const |

| Returns the branch target address. More... | |

| int8_t | numSrcRegs () const |

| Returns the number of source registers. More... | |

| int8_t | numDestRegs () const |

| Returns the number of destination registers. More... | |

| int8_t | numFPDestRegs () const |

| int8_t | numIntDestRegs () const |

| int8_t | numCCDestRegs () const |

| int8_t | numVecDestRegs () const |

| int8_t | numVecElemDestRegs () const |

| int8_t | numVecPredDestRegs () const |

| const RegId & | destRegIdx (int i) const |

| Returns the logical register index of the i'th destination register. More... | |

| const RegId & | srcRegIdx (int i) const |

| Returns the logical register index of the i'th source register. More... | |

| uint8_t | resultSize () |

| Return the size of the instResult queue. More... | |

| InstResult | popResult (InstResult dflt=InstResult()) |

| Pops a result off the instResult queue. More... | |

| void | markSrcRegReady () |

| Records that one of the source registers is ready. More... | |

| void | markSrcRegReady (RegIndex src_idx) |

| Marks a specific register as ready. More... | |

| bool | isReadySrcRegIdx (int idx) const |

| Returns if a source register is ready. More... | |

| void | setCompleted () |

| Sets this instruction as completed. More... | |

| bool | isCompleted () const |

| Returns whether or not this instruction is completed. More... | |

| void | setResultReady () |

| Marks the result as ready. More... | |

| bool | isResultReady () const |

| Returns whether or not the result is ready. More... | |

| void | setCanIssue () |

| Sets this instruction as ready to issue. More... | |

| bool | readyToIssue () const |

| Returns whether or not this instruction is ready to issue. More... | |

| void | clearCanIssue () |

| Clears this instruction being able to issue. More... | |

| void | setIssued () |

| Sets this instruction as issued from the IQ. More... | |

| bool | isIssued () const |

| Returns whether or not this instruction has issued. More... | |

| void | clearIssued () |

| Clears this instruction as being issued. More... | |

| void | setExecuted () |

| Sets this instruction as executed. More... | |

| bool | isExecuted () const |

| Returns whether or not this instruction has executed. More... | |

| void | setCanCommit () |

| Sets this instruction as ready to commit. More... | |

| void | clearCanCommit () |

| Clears this instruction as being ready to commit. More... | |

| bool | readyToCommit () const |

| Returns whether or not this instruction is ready to commit. More... | |

| void | setAtCommit () |

| bool | isAtCommit () |

| void | setCommitted () |

| Sets this instruction as committed. More... | |

| bool | isCommitted () const |

| Returns whether or not this instruction is committed. More... | |

| void | setSquashed () |

| Sets this instruction as squashed. More... | |

| bool | isSquashed () const |

| Returns whether or not this instruction is squashed. More... | |

| void | setInIQ () |

| Sets this instruction as a entry the IQ. More... | |

| void | clearInIQ () |

| Sets this instruction as a entry the IQ. More... | |

| bool | isInIQ () const |

| Returns whether or not this instruction has issued. More... | |

| void | setSquashedInIQ () |

| Sets this instruction as squashed in the IQ. More... | |

| bool | isSquashedInIQ () const |

| Returns whether or not this instruction is squashed in the IQ. More... | |

| void | setInLSQ () |

| Sets this instruction as a entry the LSQ. More... | |

| void | removeInLSQ () |

| Sets this instruction as a entry the LSQ. More... | |

| bool | isInLSQ () const |

| Returns whether or not this instruction is in the LSQ. More... | |

| void | setSquashedInLSQ () |

| Sets this instruction as squashed in the LSQ. More... | |

| bool | isSquashedInLSQ () const |

| Returns whether or not this instruction is squashed in the LSQ. More... | |

| void | setInROB () |

| Sets this instruction as a entry the ROB. More... | |

| void | clearInROB () |

| Sets this instruction as a entry the ROB. More... | |

| bool | isInROB () const |

| Returns whether or not this instruction is in the ROB. More... | |

| void | setSquashedInROB () |

| Sets this instruction as squashed in the ROB. More... | |

| bool | isSquashedInROB () const |

| Returns whether or not this instruction is squashed in the ROB. More... | |

| bool | isPinnedRegsRenamed () const |

| Returns whether pinned registers are renamed. More... | |

| void | setPinnedRegsRenamed () |

| Sets the destination registers as renamed. More... | |

| bool | isPinnedRegsWritten () const |

| Returns whether destination registers are written. More... | |

| void | setPinnedRegsWritten () |

| Sets destination registers as written. More... | |

| bool | isPinnedRegsSquashDone () const |

| Return whether dest registers' pinning status updated after squash. More... | |

| void | setPinnedRegsSquashDone () |

| Sets dest registers' status updated after squash. More... | |

| TheISA::PCState | pcState () const override |

| Read the PC state of this instruction. More... | |

| void | pcState (const TheISA::PCState &val) override |

| Set the PC state of this instruction. More... | |

| Addr | instAddr () const |

| Read the PC of this instruction. More... | |

| Addr | nextInstAddr () const |

| Read the PC of the next instruction. More... | |

| Addr | microPC () const |

| Read the micro PC of this instruction. More... | |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| void | setTid (ThreadID tid) |

| Sets the thread id. More... | |

| void | setThreadState (ImplState *state) |

| Sets the pointer to the thread state. More... | |

| ThreadContext * | tcBase () const override |

| Returns the thread context. More... | |

| bool | eaSrcsReady () const |

| Returns whether or not the eff. More... | |

| bool | strictlyOrdered () const |

| Is this instruction's memory access strictly ordered? More... | |

| void | strictlyOrdered (bool so) |

| bool | hasRequest () const |

| Has this instruction generated a memory request. More... | |

| void | setRequest () |

| Assert this instruction has generated a memory request. More... | |

| ListIt & | getInstListIt () |

| Returns iterator to this instruction in the list of all insts. More... | |

| void | setInstListIt (ListIt _instListIt) |

| Sets iterator for this instruction in the list of all insts. More... | |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. More... | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. More... | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| template<typename T > | |

| void | setScalarResult (T &&t) |

| Pushes a result onto the instResult queue. More... | |

| template<typename T > | |

| void | setVecResult (T &&t) |

| Full vector result. More... | |

| template<typename T > | |

| void | setVecElemResult (T &&t) |

| Vector element result. More... | |

| template<typename T > | |

| void | setVecPredResult (T &&t) |

| Predicate result. More... | |

Public Member Functions inherited from ExecContext Public Member Functions inherited from ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| Perform an atomic memory read operation. More... | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| Initiate a timing memory read operation. More... | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >())=0 |

| For atomic-mode contexts, perform an atomic memory write operation. More... | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More... | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More... | |

Public Member Functions inherited from RefCounted Public Member Functions inherited from RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. More... | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. More... | |

| void | incref () const |

| Increment the reference count. More... | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. More... | |

Static Public Attributes | |

| static constexpr auto | NumVecElemPerVecReg = TheISA::NumVecElemPerVecReg |

Protected Attributes | |

| std::array< RegVal, TheISA::MaxMiscDestRegs > | _destMiscRegVal |

| Values to be written to the destination misc. More... | |

| std::array< short, TheISA::MaxMiscDestRegs > | _destMiscRegIdx |

| Indexes of the destination misc. More... | |

| uint8_t | _numDestMiscRegs |

| Number of destination misc. More... | |

Protected Attributes inherited from BaseDynInst< Impl > Protected Attributes inherited from BaseDynInst< Impl > | |

| std::queue< InstResult > | instResult |

| The result of the instruction; assumes an instruction can have many destination registers. More... | |

| TheISA::PCState | pc |

| PC state for this instruction. More... | |

| std::bitset< MaxInstSrcRegs > | _readySrcRegIdx |

| Whether or not the source register is ready. More... | |

| std::array< RegId, TheISA::MaxInstDestRegs > | _flatDestRegIdx |

| Flattened register index of the destination registers of this instruction. More... | |

| std::array< PhysRegIdPtr, TheISA::MaxInstDestRegs > | _destRegIdx |

| Physical register index of the destination registers of this instruction. More... | |

| std::array< PhysRegIdPtr, TheISA::MaxInstSrcRegs > | _srcRegIdx |

| Physical register index of the source registers of this instruction. More... | |

| std::array< PhysRegIdPtr, TheISA::MaxInstDestRegs > | _prevDestRegIdx |

| Physical register index of the previous producers of the architected destinations. More... | |

Private Member Functions | |

| void | initVars () |

| Initializes variables. More... | |

Additional Inherited Members | |

Public Attributes inherited from BaseDynInst< Impl > Public Attributes inherited from BaseDynInst< Impl > | |

| InstSeqNum | seqNum |

| The sequence number of the instruction. More... | |

| const StaticInstPtr | staticInst |

| The StaticInst used by this BaseDynInst. More... | |

| ImplCPU * | cpu |

| Pointer to the Impl's CPU object. More... | |

| ImplState * | thread |

| Pointer to the thread state. More... | |

| Fault | fault |

| The kind of fault this instruction has generated. More... | |

| Trace::InstRecord * | traceData |

| InstRecord that tracks this instructions. More... | |

| ThreadID | threadNumber |

| The thread this instruction is from. More... | |

| ListIt | instListIt |

| Iterator pointing to this BaseDynInst in the list of all insts. More... | |

| TheISA::PCState | predPC |

| Predicted PC state after this instruction. More... | |

| const StaticInstPtr | macroop |

| The Macroop if one exists. More... | |

| uint8_t | readyRegs |

| How many source registers are ready. More... | |

| Addr | effAddr |

| The effective virtual address (lds & stores only). More... | |

| Addr | physEffAddr |

| The effective physical address. More... | |

| unsigned | memReqFlags |

| The memory request flags (from translation). More... | |

| unsigned | effSize |

| The size of the request. More... | |

| uint8_t * | memData |

| Pointer to the data for the memory access. More... | |

| int16_t | lqIdx |

| Load queue index. More... | |

| LQIterator | lqIt |

| int16_t | sqIdx |

| Store queue index. More... | |

| SQIterator | sqIt |

| LSQRequestPtr | savedReq |

| Saved memory request (needed when the DTB address translation is delayed due to a hw page table walk). More... | |

| RequestPtr | reqToVerify |

Protected Types inherited from BaseDynInst< Impl > Protected Types inherited from BaseDynInst< Impl > | |

| enum | Status { IqEntry, RobEntry, LsqEntry, Completed, ResultReady, CanIssue, Issued, Executed, CanCommit, AtCommit, Committed, Squashed, SquashedInIQ, SquashedInLSQ, SquashedInROB, PinnedRegsRenamed, PinnedRegsWritten, PinnedRegsSquashDone, RecoverInst, BlockingInst, ThreadsyncWait, SerializeBefore, SerializeAfter, SerializeHandled, NumStatus } |

| enum | Flags { NotAnInst, TranslationStarted, TranslationCompleted, PossibleLoadViolation, HitExternalSnoop, EffAddrValid, RecordResult, Predicate, MemAccPredicate, PredTaken, IsStrictlyOrdered, ReqMade, MemOpDone, HtmFromTransaction, MaxFlags } |

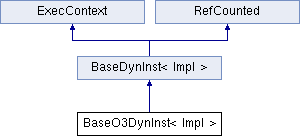

Detailed Description

template<class Impl>

class BaseO3DynInst< Impl >

Definition at line 57 of file dyn_inst.hh.

Member Typedef Documentation

◆ MachInst

| typedef TheISA::MachInst BaseO3DynInst< Impl >::MachInst |

Binary machine instruction type.

Definition at line 64 of file dyn_inst.hh.

◆ O3CPU

| typedef Impl::O3CPU BaseO3DynInst< Impl >::O3CPU |

Typedef for the CPU.

Definition at line 61 of file dyn_inst.hh.

◆ VecElem

| using BaseO3DynInst< Impl >::VecElem = TheISA::VecElem |

Definition at line 67 of file dyn_inst.hh.

◆ VecPredRegContainer

| using BaseO3DynInst< Impl >::VecPredRegContainer = TheISA::VecPredRegContainer |

Definition at line 69 of file dyn_inst.hh.

◆ VecRegContainer

| using BaseO3DynInst< Impl >::VecRegContainer = TheISA::VecRegContainer |

Register types.

Definition at line 66 of file dyn_inst.hh.

Member Enumeration Documentation

◆ anonymous enum

| anonymous enum |

| Enumerator | |

|---|---|

| MaxInstSrcRegs | |

| MaxInstDestRegs | |

Definition at line 71 of file dyn_inst.hh.

Constructor & Destructor Documentation

◆ BaseO3DynInst() [1/2]

| BaseO3DynInst< Impl >::BaseO3DynInst | ( | const StaticInstPtr & | staticInst, |

| const StaticInstPtr & | macroop, | ||

| TheISA::PCState | pc, | ||

| TheISA::PCState | predPC, | ||

| InstSeqNum | seq_num, | ||

| O3CPU * | cpu | ||

| ) |

BaseDynInst constructor given a binary instruction.

Definition at line 48 of file dyn_inst_impl.hh.

References BaseO3DynInst< Impl >::initVars().

◆ BaseO3DynInst() [2/2]

| BaseO3DynInst< Impl >::BaseO3DynInst | ( | const StaticInstPtr & | _staticInst, |

| const StaticInstPtr & | _macroop | ||

| ) |

BaseDynInst constructor given a static inst pointer.

Definition at line 58 of file dyn_inst_impl.hh.

References BaseO3DynInst< Impl >::initVars().

◆ ~BaseO3DynInst()

| BaseO3DynInst< Impl >::~BaseO3DynInst |

Definition at line 65 of file dyn_inst_impl.hh.

References DPRINTFR, DTRACE, and X86ISA::val.

Member Function Documentation

◆ completeAcc()

| Fault BaseO3DynInst< Impl >::completeAcc | ( | PacketPtr | pkt | ) |

Completes the access.

Only valid for memory operations.

Definition at line 161 of file dyn_inst_impl.hh.

References Packet::req.

◆ execute()

| Fault BaseO3DynInst< Impl >::execute |

Executes the instruction.

Definition at line 125 of file dyn_inst_impl.hh.

◆ forwardOldRegs()

|

inline |

Definition at line 207 of file dyn_inst.hh.

References CCRegClass, RegId::classValue(), StaticInst::destRegIdx(), FloatRegClass, RefCountingPtr< T >::get(), IntRegClass, MiscRegClass, BaseDynInst< Impl >::numDestRegs(), panic, BaseDynInst< Impl >::prevDestRegIdx(), BaseO3DynInst< Impl >::setCCRegOperand(), BaseO3DynInst< Impl >::setFloatRegOperandBits(), BaseO3DynInst< Impl >::setIntRegOperand(), BaseO3DynInst< Impl >::setVecElemOperand(), BaseO3DynInst< Impl >::setVecPredRegOperand(), BaseO3DynInst< Impl >::setVecRegOperand(), BaseDynInst< Impl >::staticInst, VecElemClass, VecPredRegClass, and VecRegClass.

◆ getWritableVecPredRegOperand()

|

inlineoverridevirtual |

Gets destination predicate register operand for modification.

Implements ExecContext.

Definition at line 369 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, and BaseDynInst< Impl >::cpu.

◆ getWritableVecRegOperand()

|

inlineoverridevirtual |

Read destination vector register operand for modification.

Implements ExecContext.

Definition at line 289 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, and BaseDynInst< Impl >::cpu.

◆ initiateAcc()

| Fault BaseO3DynInst< Impl >::initiateAcc |

Initiates the access.

Only valid for memory operations.

Definition at line 143 of file dyn_inst_impl.hh.

◆ initVars()

|

private |

Initializes variables.

Definition at line 103 of file dyn_inst_impl.hh.

Referenced by BaseO3DynInst< Impl >::BaseO3DynInst().

◆ readCCRegOperand()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 375 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readFloatRegOperandBits()

|

inlineoverridevirtual |

Reads a floating point register in its binary format, instead of by value.

Implements ExecContext.

Definition at line 274 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readIntRegOperand()

|

inlineoverridevirtual |

Reads an integer register.

Implements ExecContext.

Definition at line 268 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readMiscReg()

|

inlineoverridevirtual |

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements ExecContext.

Definition at line 137 of file dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and BaseDynInst< Impl >::threadNumber.

◆ readMiscRegOperand()

|

inlineoverridevirtual |

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements ExecContext.

Definition at line 171 of file dyn_inst.hh.

References BaseDynInst< Impl >::cpu, RegId::index(), X86ISA::reg, and ArmISA::si.

◆ readVec16BitLaneOperand()

|

inlineoverridevirtual |

Reads source vector 16bit operand.

Implements ExecContext.

Definition at line 305 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readVec32BitLaneOperand()

|

inlineoverridevirtual |

Reads source vector 32bit operand.

Implements ExecContext.

Definition at line 312 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readVec64BitLaneOperand()

|

inlineoverridevirtual |

Reads source vector 64bit operand.

Implements ExecContext.

Definition at line 319 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readVec8BitLaneOperand()

|

inlineoverridevirtual |

Vector Register Lane Interfaces.

Reads source vector 8bit operand.

Implements ExecContext.

Definition at line 298 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readVecElemOperand()

|

inlineoverridevirtual |

Vector Elem Interfaces.

Reads an element of a vector register.

Implements ExecContext.

Definition at line 357 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readVecPredRegOperand()

|

inlineoverridevirtual |

Predicate registers interface.

Reads source predicate register operand.

Implements ExecContext.

Definition at line 363 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ readVecRegOperand()

|

inlineoverridevirtual |

Vector Register Interfaces.

Reads source vector register operand.

Implements ExecContext.

Definition at line 280 of file dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and BaseDynInst< Impl >::cpu.

◆ setCCRegOperand()

|

inlineoverridevirtual |

Records a CC register being set to a value.

Reimplemented from BaseDynInst< Impl >.

Definition at line 421 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::cpu, BaseDynInst< Impl >::setCCRegOperand(), ArmISA::si, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ setFloatRegOperandBits()

|

inlineoverridevirtual |

Records an fp register being set to an integer value.

Reimplemented from BaseDynInst< Impl >.

Definition at line 391 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::cpu, BaseDynInst< Impl >::setFloatRegOperandBits(), ArmISA::si, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ setIntRegOperand()

|

inlineoverridevirtual |

- Todo:

- : Make results into arrays so they can handle multiple dest registers.

Reimplemented from BaseDynInst< Impl >.

Definition at line 384 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::cpu, BaseDynInst< Impl >::setIntRegOperand(), ArmISA::si, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ setMiscReg()

|

inlineoverridevirtual |

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Writes to misc. registers are recorded and deferred until the commit stage, when updateMiscRegs() is called. First, check if the misc reg has been written before and update its value to be committed instead of making a new entry. If not, make a new entry and record the write.

Implements ExecContext.

Definition at line 146 of file dyn_inst.hh.

References BaseO3DynInst< Impl >::_destMiscRegIdx, BaseO3DynInst< Impl >::_destMiscRegVal, BaseO3DynInst< Impl >::_numDestMiscRegs, PowerISA::MaxMiscDestRegs, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setMiscRegOperand().

◆ setMiscRegOperand()

|

inlineoverridevirtual |

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Implements ExecContext.

Definition at line 182 of file dyn_inst.hh.

References X86ISA::reg, BaseO3DynInst< Impl >::setMiscReg(), ArmISA::si, and X86ISA::val.

◆ setVecElemOperand()

|

inlineoverridevirtual |

Record a vector register being set to a value.

Reimplemented from BaseDynInst< Impl >.

Definition at line 405 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::cpu, BaseDynInst< Impl >::setVecElemOperand(), ArmISA::si, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ setVecLaneOperand() [1/4]

|

inlineoverridevirtual |

Write a lane of the destination vector operand.

Implements ExecContext.

Definition at line 332 of file dyn_inst.hh.

References BaseO3DynInst< Impl >::setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperand() [2/4]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 350 of file dyn_inst.hh.

References BaseO3DynInst< Impl >::setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperand() [3/4]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 344 of file dyn_inst.hh.

References BaseO3DynInst< Impl >::setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperand() [4/4]

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 338 of file dyn_inst.hh.

References BaseO3DynInst< Impl >::setVecLaneOperandT(), ArmISA::si, and X86ISA::val.

◆ setVecLaneOperandT()

|

inline |

Write a lane of the destination vector operand.

Definition at line 327 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::cpu, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setVecLaneOperand().

◆ setVecPredRegOperand()

|

inlineoverridevirtual |

Record a vector register being set to a value.

Reimplemented from BaseDynInst< Impl >.

Definition at line 414 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::cpu, BaseDynInst< Impl >::setVecPredRegOperand(), ArmISA::si, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ setVecRegOperand()

|

inlineoverridevirtual |

Record a vector register being set to a value.

Reimplemented from BaseDynInst< Impl >.

Definition at line 398 of file dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::cpu, BaseDynInst< Impl >::setVecRegOperand(), ArmISA::si, and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ syscall()

|

overridevirtual |

◆ trap()

| void BaseO3DynInst< Impl >::trap | ( | const Fault & | fault | ) |

Traps to handle specified fault.

Definition at line 185 of file dyn_inst_impl.hh.

◆ updateMiscRegs()

|

inline |

Called at the commit stage to update the misc.

registers.

Definition at line 191 of file dyn_inst.hh.

References BaseO3DynInst< Impl >::_destMiscRegVal, BaseO3DynInst< Impl >::_numDestMiscRegs, BaseDynInst< Impl >::cpu, ArmISA::i, and BaseDynInst< Impl >::thread.

Member Data Documentation

◆ _destMiscRegIdx

|

protected |

Indexes of the destination misc.

registers. They are needed to defer the write accesses to the misc. registers until the commit stage, when the instruction is out of its speculative state.

Definition at line 114 of file dyn_inst.hh.

Referenced by BaseO3DynInst< Impl >::setMiscReg().

◆ _destMiscRegVal

|

protected |

Values to be written to the destination misc.

registers.

Definition at line 108 of file dyn_inst.hh.

Referenced by BaseO3DynInst< Impl >::setMiscReg(), and BaseO3DynInst< Impl >::updateMiscRegs().

◆ _numDestMiscRegs

|

protected |

Number of destination misc.

registers.

Definition at line 117 of file dyn_inst.hh.

Referenced by BaseO3DynInst< Impl >::setMiscReg(), and BaseO3DynInst< Impl >::updateMiscRegs().

◆ NumVecElemPerVecReg

|

staticconstexpr |

Definition at line 68 of file dyn_inst.hh.

The documentation for this class was generated from the following files:

- cpu/o3/dyn_inst.hh

- cpu/o3/dyn_inst_impl.hh