#include <base_dyn_inst.hh>

Public Types | |

| enum | { MaxInstSrcRegs = TheISA::MaxInstSrcRegs, MaxInstDestRegs = TheISA::MaxInstDestRegs } |

| typedef Impl::CPUType | ImplCPU |

| typedef ImplCPU::ImplState | ImplState |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | LSQRequestPtr = typename Impl::CPUPol::LSQ::LSQRequest * |

| using | LQIterator = typename Impl::CPUPol::LSQUnit::LQIterator |

| using | SQIterator = typename Impl::CPUPol::LSQUnit::SQIterator |

| typedef Impl::DynInstPtr | DynInstPtr |

| typedef RefCountingPtr< BaseDynInst< Impl > > | BaseDynInstPtr |

| typedef std::list< DynInstPtr >::iterator | ListIt |

Public Types inherited from ExecContext Public Types inherited from ExecContext | |

| typedef TheISA::PCState | PCState |

| using | VecRegContainer = TheISA::VecRegContainer |

| using | VecElem = TheISA::VecElem |

| using | VecPredRegContainer = TheISA::VecPredRegContainer |

Public Member Functions | |

| BaseCPU * | getCpuPtr () |

| void | recordResult (bool f) |

| Records changes to result? More... | |

| bool | effAddrValid () const |

| Is the effective virtual address valid. More... | |

| void | effAddrValid (bool b) |

| bool | memOpDone () const |

| Whether or not the memory operation is done. More... | |

| void | memOpDone (bool f) |

| bool | notAnInst () const |

| void | setNotAnInst () |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. More... | |

| void | demapInstPage (Addr vaddr, uint64_t asn) |

| void | demapDataPage (Addr vaddr, uint64_t asn) |

| Fault | initiateMemRead (Addr addr, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | initiateHtmCmd (Request::Flags flags) override |

| Initiate an HTM command, e.g. More... | |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >()) override |

| Fault | initiateMemAMO (Addr addr, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| bool | translationStarted () const |

| True if the DTB address translation has started. More... | |

| void | translationStarted (bool f) |

| bool | translationCompleted () const |

| True if the DTB address translation has completed. More... | |

| void | translationCompleted (bool f) |

| bool | possibleLoadViolation () const |

| True if this address was found to match a previous load and they issued out of order. More... | |

| void | possibleLoadViolation (bool f) |

| bool | hitExternalSnoop () const |

| True if the address hit a external snoop while sitting in the LSQ. More... | |

| void | hitExternalSnoop (bool f) |

| bool | isTranslationDelayed () const |

| Returns true if the DTB address translation is being delayed due to a hw page table walk. More... | |

| PhysRegIdPtr | renamedDestRegIdx (int idx) const |

| Returns the physical register index of the i'th destination register. More... | |

| PhysRegIdPtr | renamedSrcRegIdx (int idx) const |

| Returns the physical register index of the i'th source register. More... | |

| const RegId & | flattenedDestRegIdx (int idx) const |

| Returns the flattened register index of the i'th destination register. More... | |

| PhysRegIdPtr | prevDestRegIdx (int idx) const |

| Returns the physical register index of the previous physical register that remapped to the same logical register index. More... | |

| void | renameDestReg (int idx, PhysRegIdPtr renamed_dest, PhysRegIdPtr previous_rename) |

| Renames a destination register to a physical register. More... | |

| void | renameSrcReg (int idx, PhysRegIdPtr renamed_src) |

| Renames a source logical register to the physical register which has/will produce that logical register's result. More... | |

| void | flattenDestReg (int idx, const RegId &flattened_dest) |

| Flattens a destination architectural register index into a logical index. More... | |

| BaseDynInst (const StaticInstPtr &staticInst, const StaticInstPtr ¯oop, TheISA::PCState pc, TheISA::PCState predPC, InstSeqNum seq_num, ImplCPU *cpu) | |

| BaseDynInst constructor given a binary instruction. More... | |

| BaseDynInst (const StaticInstPtr &staticInst, const StaticInstPtr ¯oop) | |

| BaseDynInst constructor given a StaticInst pointer. More... | |

| ~BaseDynInst () | |

| BaseDynInst destructor. More... | |

| void | dump () |

| Dumps out contents of this BaseDynInst. More... | |

| void | dump (std::string &outstring) |

| Dumps out contents of this BaseDynInst into given string. More... | |

| int | cpuId () const |

| Read this CPU's ID. More... | |

| uint32_t | socketId () const |

| Read this CPU's Socket ID. More... | |

| RequestorID | requestorId () const |

| Read this CPU's data requestor ID. More... | |

| ContextID | contextId () const |

| Read this context's system-wide ID. More... | |

| Fault | getFault () const |

| Returns the fault type. More... | |

| Fault & | getFault () |

| TODO: This I added for the LSQRequest side to be able to modify the fault. More... | |

| bool | doneTargCalc () |

| Checks whether or not this instruction has had its branch target calculated yet. More... | |

| void | setPredTarg (const TheISA::PCState &_predPC) |

| Set the predicted target of this current instruction. More... | |

| const TheISA::PCState & | readPredTarg () |

| Addr | predInstAddr () |

| Returns the predicted PC immediately after the branch. More... | |

| Addr | predNextInstAddr () |

| Returns the predicted PC two instructions after the branch. More... | |

| Addr | predMicroPC () |

| Returns the predicted micro PC after the branch. More... | |

| bool | readPredTaken () |

| Returns whether the instruction was predicted taken or not. More... | |

| void | setPredTaken (bool predicted_taken) |

| bool | mispredicted () |

| Returns whether the instruction mispredicted. More... | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isCondDelaySlot () const |

| bool | isThreadSync () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isMemBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isIprAccess () const |

| bool | isUnverifiable () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isMicroBranch () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isHtmCmd () const |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| void | setHtmTransactionalState (uint64_t htm_uid, uint64_t htm_depth) |

| void | clearHtmTransactionalState () |

| void | setSerializeBefore () |

| Temporarily sets this instruction as a serialize before instruction. More... | |

| void | clearSerializeBefore () |

| Clears the serializeBefore part of this instruction. More... | |

| bool | isTempSerializeBefore () |

| Checks if this serializeBefore is only temporarily set. More... | |

| void | setSerializeAfter () |

| Temporarily sets this instruction as a serialize after instruction. More... | |

| void | clearSerializeAfter () |

| Clears the serializeAfter part of this instruction. More... | |

| bool | isTempSerializeAfter () |

| Checks if this serializeAfter is only temporarily set. More... | |

| void | setSerializeHandled () |

| Sets the serialization part of this instruction as handled. More... | |

| bool | isSerializeHandled () |

| Checks if the serialization part of this instruction has been handled. More... | |

| OpClass | opClass () const |

| Returns the opclass of this instruction. More... | |

| TheISA::PCState | branchTarget () const |

| Returns the branch target address. More... | |

| int8_t | numSrcRegs () const |

| Returns the number of source registers. More... | |

| int8_t | numDestRegs () const |

| Returns the number of destination registers. More... | |

| int8_t | numFPDestRegs () const |

| int8_t | numIntDestRegs () const |

| int8_t | numCCDestRegs () const |

| int8_t | numVecDestRegs () const |

| int8_t | numVecElemDestRegs () const |

| int8_t | numVecPredDestRegs () const |

| const RegId & | destRegIdx (int i) const |

| Returns the logical register index of the i'th destination register. More... | |

| const RegId & | srcRegIdx (int i) const |

| Returns the logical register index of the i'th source register. More... | |

| uint8_t | resultSize () |

| Return the size of the instResult queue. More... | |

| InstResult | popResult (InstResult dflt=InstResult()) |

| Pops a result off the instResult queue. More... | |

| void | setIntRegOperand (const StaticInst *si, int idx, RegVal val) override |

| Records an integer register being set to a value. More... | |

| void | setCCRegOperand (const StaticInst *si, int idx, RegVal val) override |

| Records a CC register being set to a value. More... | |

| void | setVecRegOperand (const StaticInst *si, int idx, const VecRegContainer &val) override |

| Record a vector register being set to a value. More... | |

| void | setFloatRegOperandBits (const StaticInst *si, int idx, RegVal val) override |

| Records an fp register being set to an integer value. More... | |

| void | setVecElemOperand (const StaticInst *si, int idx, const VecElem val) override |

| Record a vector register being set to a value. More... | |

| void | setVecPredRegOperand (const StaticInst *si, int idx, const VecPredRegContainer &val) override |

| Record a vector register being set to a value. More... | |

| void | markSrcRegReady () |

| Records that one of the source registers is ready. More... | |

| void | markSrcRegReady (RegIndex src_idx) |

| Marks a specific register as ready. More... | |

| bool | isReadySrcRegIdx (int idx) const |

| Returns if a source register is ready. More... | |

| void | setCompleted () |

| Sets this instruction as completed. More... | |

| bool | isCompleted () const |

| Returns whether or not this instruction is completed. More... | |

| void | setResultReady () |

| Marks the result as ready. More... | |

| bool | isResultReady () const |

| Returns whether or not the result is ready. More... | |

| void | setCanIssue () |

| Sets this instruction as ready to issue. More... | |

| bool | readyToIssue () const |

| Returns whether or not this instruction is ready to issue. More... | |

| void | clearCanIssue () |

| Clears this instruction being able to issue. More... | |

| void | setIssued () |

| Sets this instruction as issued from the IQ. More... | |

| bool | isIssued () const |

| Returns whether or not this instruction has issued. More... | |

| void | clearIssued () |

| Clears this instruction as being issued. More... | |

| void | setExecuted () |

| Sets this instruction as executed. More... | |

| bool | isExecuted () const |

| Returns whether or not this instruction has executed. More... | |

| void | setCanCommit () |

| Sets this instruction as ready to commit. More... | |

| void | clearCanCommit () |

| Clears this instruction as being ready to commit. More... | |

| bool | readyToCommit () const |

| Returns whether or not this instruction is ready to commit. More... | |

| void | setAtCommit () |

| bool | isAtCommit () |

| void | setCommitted () |

| Sets this instruction as committed. More... | |

| bool | isCommitted () const |

| Returns whether or not this instruction is committed. More... | |

| void | setSquashed () |

| Sets this instruction as squashed. More... | |

| bool | isSquashed () const |

| Returns whether or not this instruction is squashed. More... | |

| void | setInIQ () |

| Sets this instruction as a entry the IQ. More... | |

| void | clearInIQ () |

| Sets this instruction as a entry the IQ. More... | |

| bool | isInIQ () const |

| Returns whether or not this instruction has issued. More... | |

| void | setSquashedInIQ () |

| Sets this instruction as squashed in the IQ. More... | |

| bool | isSquashedInIQ () const |

| Returns whether or not this instruction is squashed in the IQ. More... | |

| void | setInLSQ () |

| Sets this instruction as a entry the LSQ. More... | |

| void | removeInLSQ () |

| Sets this instruction as a entry the LSQ. More... | |

| bool | isInLSQ () const |

| Returns whether or not this instruction is in the LSQ. More... | |

| void | setSquashedInLSQ () |

| Sets this instruction as squashed in the LSQ. More... | |

| bool | isSquashedInLSQ () const |

| Returns whether or not this instruction is squashed in the LSQ. More... | |

| void | setInROB () |

| Sets this instruction as a entry the ROB. More... | |

| void | clearInROB () |

| Sets this instruction as a entry the ROB. More... | |

| bool | isInROB () const |

| Returns whether or not this instruction is in the ROB. More... | |

| void | setSquashedInROB () |

| Sets this instruction as squashed in the ROB. More... | |

| bool | isSquashedInROB () const |

| Returns whether or not this instruction is squashed in the ROB. More... | |

| bool | isPinnedRegsRenamed () const |

| Returns whether pinned registers are renamed. More... | |

| void | setPinnedRegsRenamed () |

| Sets the destination registers as renamed. More... | |

| bool | isPinnedRegsWritten () const |

| Returns whether destination registers are written. More... | |

| void | setPinnedRegsWritten () |

| Sets destination registers as written. More... | |

| bool | isPinnedRegsSquashDone () const |

| Return whether dest registers' pinning status updated after squash. More... | |

| void | setPinnedRegsSquashDone () |

| Sets dest registers' status updated after squash. More... | |

| TheISA::PCState | pcState () const override |

| Read the PC state of this instruction. More... | |

| void | pcState (const TheISA::PCState &val) override |

| Set the PC state of this instruction. More... | |

| Addr | instAddr () const |

| Read the PC of this instruction. More... | |

| Addr | nextInstAddr () const |

| Read the PC of the next instruction. More... | |

| Addr | microPC () const |

| Read the micro PC of this instruction. More... | |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| void | setTid (ThreadID tid) |

| Sets the thread id. More... | |

| void | setThreadState (ImplState *state) |

| Sets the pointer to the thread state. More... | |

| ThreadContext * | tcBase () const override |

| Returns the thread context. More... | |

| bool | eaSrcsReady () const |

| Returns whether or not the eff. More... | |

| bool | strictlyOrdered () const |

| Is this instruction's memory access strictly ordered? More... | |

| void | strictlyOrdered (bool so) |

| bool | hasRequest () const |

| Has this instruction generated a memory request. More... | |

| void | setRequest () |

| Assert this instruction has generated a memory request. More... | |

| ListIt & | getInstListIt () |

| Returns iterator to this instruction in the list of all insts. More... | |

| void | setInstListIt (ListIt _instListIt) |

| Sets iterator for this instruction in the list of all insts. More... | |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. More... | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. More... | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| template<typename T > | |

| void | setScalarResult (T &&t) |

| Pushes a result onto the instResult queue. More... | |

| template<typename T > | |

| void | setVecResult (T &&t) |

| Full vector result. More... | |

| template<typename T > | |

| void | setVecElemResult (T &&t) |

| Vector element result. More... | |

| template<typename T > | |

| void | setVecPredResult (T &&t) |

| Predicate result. More... | |

Public Member Functions inherited from ExecContext Public Member Functions inherited from ExecContext | |

| virtual RegVal | readIntRegOperand (const StaticInst *si, int idx)=0 |

| Reads an integer register. More... | |

| virtual RegVal | readFloatRegOperandBits (const StaticInst *si, int idx)=0 |

| Reads a floating point register in its binary format, instead of by value. More... | |

| virtual const VecRegContainer & | readVecRegOperand (const StaticInst *si, int idx) const =0 |

| Vector Register Interfaces. More... | |

| virtual VecRegContainer & | getWritableVecRegOperand (const StaticInst *si, int idx)=0 |

| Gets destination vector register operand for modification. More... | |

| virtual ConstVecLane8 | readVec8BitLaneOperand (const StaticInst *si, int idx) const =0 |

| Vector Register Lane Interfaces. More... | |

| virtual ConstVecLane16 | readVec16BitLaneOperand (const StaticInst *si, int idx) const =0 |

| Reads source vector 16bit operand. More... | |

| virtual ConstVecLane32 | readVec32BitLaneOperand (const StaticInst *si, int idx) const =0 |

| Reads source vector 32bit operand. More... | |

| virtual ConstVecLane64 | readVec64BitLaneOperand (const StaticInst *si, int idx) const =0 |

| Reads source vector 64bit operand. More... | |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::Byte > &val)=0 |

| Write a lane of the destination vector operand. More... | |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::TwoByte > &val)=0 |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::FourByte > &val)=0 |

| virtual void | setVecLaneOperand (const StaticInst *si, int idx, const LaneData< LaneSize::EightByte > &val)=0 |

| virtual VecElem | readVecElemOperand (const StaticInst *si, int idx) const =0 |

| Vector Elem Interfaces. More... | |

| virtual const VecPredRegContainer & | readVecPredRegOperand (const StaticInst *si, int idx) const =0 |

| Predicate registers interface. More... | |

| virtual VecPredRegContainer & | getWritableVecPredRegOperand (const StaticInst *si, int idx)=0 |

| Gets destination predicate register operand for modification. More... | |

| virtual RegVal | readCCRegOperand (const StaticInst *si, int idx)=0 |

| virtual RegVal | readMiscRegOperand (const StaticInst *si, int idx)=0 |

| virtual void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val)=0 |

| virtual RegVal | readMiscReg (int misc_reg)=0 |

| Reads a miscellaneous register, handling any architectural side effects due to reading that register. More... | |

| virtual void | setMiscReg (int misc_reg, RegVal val)=0 |

| Sets a miscellaneous register, handling any architectural side effects due to writing that register. More... | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| Perform an atomic memory read operation. More... | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable=std::vector< bool >()) |

| Initiate a timing memory read operation. More... | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable=std::vector< bool >())=0 |

| For atomic-mode contexts, perform an atomic memory write operation. More... | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) More... | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) More... | |

| virtual void | syscall ()=0 |

| Executes a syscall. More... | |

Public Member Functions inherited from RefCounted Public Member Functions inherited from RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. More... | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. More... | |

| void | incref () const |

| Increment the reference count. More... | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. More... | |

Public Attributes | |

| InstSeqNum | seqNum |

| The sequence number of the instruction. More... | |

| const StaticInstPtr | staticInst |

| The StaticInst used by this BaseDynInst. More... | |

| ImplCPU * | cpu |

| Pointer to the Impl's CPU object. More... | |

| ImplState * | thread |

| Pointer to the thread state. More... | |

| Fault | fault |

| The kind of fault this instruction has generated. More... | |

| Trace::InstRecord * | traceData |

| InstRecord that tracks this instructions. More... | |

| ThreadID | threadNumber |

| The thread this instruction is from. More... | |

| ListIt | instListIt |

| Iterator pointing to this BaseDynInst in the list of all insts. More... | |

| TheISA::PCState | predPC |

| Predicted PC state after this instruction. More... | |

| const StaticInstPtr | macroop |

| The Macroop if one exists. More... | |

| uint8_t | readyRegs |

| How many source registers are ready. More... | |

| Addr | effAddr |

| The effective virtual address (lds & stores only). More... | |

| Addr | physEffAddr |

| The effective physical address. More... | |

| unsigned | memReqFlags |

| The memory request flags (from translation). More... | |

| unsigned | effSize |

| The size of the request. More... | |

| uint8_t * | memData |

| Pointer to the data for the memory access. More... | |

| int16_t | lqIdx |

| Load queue index. More... | |

| LQIterator | lqIt |

| int16_t | sqIdx |

| Store queue index. More... | |

| SQIterator | sqIt |

| LSQRequestPtr | savedReq |

| Saved memory request (needed when the DTB address translation is delayed due to a hw page table walk). More... | |

| RequestPtr | reqToVerify |

Protected Attributes | |

| std::queue< InstResult > | instResult |

| The result of the instruction; assumes an instruction can have many destination registers. More... | |

| TheISA::PCState | pc |

| PC state for this instruction. More... | |

| std::bitset< MaxInstSrcRegs > | _readySrcRegIdx |

| Whether or not the source register is ready. More... | |

| std::array< RegId, TheISA::MaxInstDestRegs > | _flatDestRegIdx |

| Flattened register index of the destination registers of this instruction. More... | |

| std::array< PhysRegIdPtr, TheISA::MaxInstDestRegs > | _destRegIdx |

| Physical register index of the destination registers of this instruction. More... | |

| std::array< PhysRegIdPtr, TheISA::MaxInstSrcRegs > | _srcRegIdx |

| Physical register index of the source registers of this instruction. More... | |

| std::array< PhysRegIdPtr, TheISA::MaxInstDestRegs > | _prevDestRegIdx |

| Physical register index of the previous producers of the architected destinations. More... | |

Private Member Functions | |

| void | initVars () |

| Function to initialize variables in the constructors. More... | |

Private Attributes | |

| std::bitset< MaxFlags > | instFlags |

| std::bitset< NumStatus > | status |

| The status of this BaseDynInst. More... | |

| uint64_t | htmUid |

| uint64_t | htmDepth |

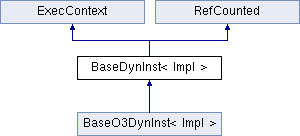

Detailed Description

template<class Impl>

class BaseDynInst< Impl >

Definition at line 76 of file base_dyn_inst.hh.

Member Typedef Documentation

◆ BaseDynInstPtr

| typedef RefCountingPtr<BaseDynInst<Impl> > BaseDynInst< Impl >::BaseDynInstPtr |

Definition at line 90 of file base_dyn_inst.hh.

◆ DynInstPtr

| typedef Impl::DynInstPtr BaseDynInst< Impl >::DynInstPtr |

Definition at line 89 of file base_dyn_inst.hh.

◆ ImplCPU

| typedef Impl::CPUType BaseDynInst< Impl >::ImplCPU |

Definition at line 80 of file base_dyn_inst.hh.

◆ ImplState

| typedef ImplCPU::ImplState BaseDynInst< Impl >::ImplState |

Definition at line 81 of file base_dyn_inst.hh.

◆ ListIt

| typedef std::list<DynInstPtr>::iterator BaseDynInst< Impl >::ListIt |

Definition at line 93 of file base_dyn_inst.hh.

◆ LQIterator

| using BaseDynInst< Impl >::LQIterator = typename Impl::CPUPol::LSQUnit::LQIterator |

Definition at line 85 of file base_dyn_inst.hh.

◆ LSQRequestPtr

| using BaseDynInst< Impl >::LSQRequestPtr = typename Impl::CPUPol::LSQ::LSQRequest* |

Definition at line 84 of file base_dyn_inst.hh.

◆ SQIterator

| using BaseDynInst< Impl >::SQIterator = typename Impl::CPUPol::LSQUnit::SQIterator |

Definition at line 86 of file base_dyn_inst.hh.

◆ VecRegContainer

| using BaseDynInst< Impl >::VecRegContainer = TheISA::VecRegContainer |

Definition at line 82 of file base_dyn_inst.hh.

Member Enumeration Documentation

◆ anonymous enum

| anonymous enum |

| Enumerator | |

|---|---|

| MaxInstSrcRegs | |

| MaxInstDestRegs | Max source regs. |

Definition at line 95 of file base_dyn_inst.hh.

◆ Flags

|

protected |

Definition at line 130 of file base_dyn_inst.hh.

◆ Status

|

protected |

| Enumerator | |

|---|---|

| IqEntry | |

| RobEntry | Instruction is in the IQ. |

| LsqEntry | Instruction is in the ROB. |

| Completed | Instruction is in the LSQ. |

| ResultReady | Instruction has completed. |

| CanIssue | Instruction has its result. |

| Issued | Instruction can issue and execute. |

| Executed | Instruction has issued. |

| CanCommit | Instruction has executed. |

| AtCommit | Instruction can commit. |

| Committed | Instruction has reached commit. |

| Squashed | Instruction has committed. |

| SquashedInIQ | Instruction is squashed. |

| SquashedInLSQ | Instruction is squashed in the IQ. |

| SquashedInROB | Instruction is squashed in the LSQ. |

| PinnedRegsRenamed | Instruction is squashed in the ROB. |

| PinnedRegsWritten | Pinned registers are renamed. |

| PinnedRegsSquashDone | Pinned registers are written back. |

| RecoverInst | Regs pinning status updated after squash. |

| BlockingInst | Is a recover instruction. |

| ThreadsyncWait | Is a blocking instruction. |

| SerializeBefore | Is a thread synchronization instruction. |

| SerializeAfter | Needs to serialize on instructions ahead of it. |

| SerializeHandled | Needs to serialize instructions behind it. |

| NumStatus | Serialization has been handled. |

Definition at line 101 of file base_dyn_inst.hh.

Constructor & Destructor Documentation

◆ BaseDynInst() [1/2]

| BaseDynInst< Impl >::BaseDynInst | ( | const StaticInstPtr & | staticInst, |

| const StaticInstPtr & | macroop, | ||

| TheISA::PCState | pc, | ||

| TheISA::PCState | predPC, | ||

| InstSeqNum | seq_num, | ||

| ImplCPU * | cpu | ||

| ) |

BaseDynInst constructor given a binary instruction.

- Parameters

-

staticInst A StaticInstPtr to the underlying instruction. pc The PC state for the instruction. predPC The predicted next PC state for the instruction. seq_num The sequence number of the instruction. cpu Pointer to the instruction's CPU.

Definition at line 60 of file base_dyn_inst_impl.hh.

References BaseDynInst< Impl >::initVars(), BaseDynInst< Impl >::pc, BaseDynInst< Impl >::predPC, and BaseDynInst< Impl >::seqNum.

◆ BaseDynInst() [2/2]

| BaseDynInst< Impl >::BaseDynInst | ( | const StaticInstPtr & | staticInst, |

| const StaticInstPtr & | macroop | ||

| ) |

BaseDynInst constructor given a StaticInst pointer.

- Parameters

-

_staticInst The StaticInst for this BaseDynInst.

Definition at line 81 of file base_dyn_inst_impl.hh.

References BaseDynInst< Impl >::initVars(), and BaseDynInst< Impl >::seqNum.

◆ ~BaseDynInst()

| BaseDynInst< Impl >::~BaseDynInst |

BaseDynInst destructor.

Definition at line 141 of file base_dyn_inst_impl.hh.

Member Function Documentation

◆ armMonitor()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 1048 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and BaseDynInst< Impl >::threadNumber.

◆ branchTarget()

|

inline |

Returns the branch target address.

Definition at line 660 of file base_dyn_inst.hh.

References StaticInst::branchTarget(), BaseDynInst< Impl >::pc, and BaseDynInst< Impl >::staticInst.

◆ clearCanCommit()

|

inline |

Clears this instruction as being ready to commit.

Definition at line 854 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::CanCommit, and BaseDynInst< Impl >::status.

◆ clearCanIssue()

|

inline |

Clears this instruction being able to issue.

Definition at line 833 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::CanIssue, and BaseDynInst< Impl >::status.

◆ clearHtmTransactionalState()

|

inline |

◆ clearInIQ()

|

inline |

Sets this instruction as a entry the IQ.

Definition at line 881 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::IqEntry, and BaseDynInst< Impl >::status.

◆ clearInROB()

|

inline |

Sets this instruction as a entry the ROB.

Definition at line 917 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::RobEntry, and BaseDynInst< Impl >::status.

◆ clearIssued()

|

inline |

Clears this instruction as being issued.

Definition at line 842 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Issued, and BaseDynInst< Impl >::status.

◆ clearSerializeAfter()

|

inline |

Clears the serializeAfter part of this instruction.

Definition at line 641 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeAfter, and BaseDynInst< Impl >::status.

◆ clearSerializeBefore()

|

inline |

Clears the serializeBefore part of this instruction.

Definition at line 632 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeBefore, and BaseDynInst< Impl >::status.

◆ contextId()

|

inline |

Read this context's system-wide ID.

Definition at line 475 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::thread.

◆ cpuId()

|

inline |

Read this CPU's ID.

Definition at line 466 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu.

◆ demapDataPage()

|

inline |

Definition at line 305 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and MipsISA::vaddr.

◆ demapInstPage()

|

inline |

Definition at line 300 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and MipsISA::vaddr.

◆ demapPage()

|

inlineoverridevirtual |

Invalidate a page in the DTLB and ITLB.

Implements ExecContext.

Definition at line 295 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and MipsISA::vaddr.

◆ destRegIdx()

|

inline |

Returns the logical register index of the i'th destination register.

Definition at line 687 of file base_dyn_inst.hh.

References StaticInst::destRegIdx(), ArmISA::i, and BaseDynInst< Impl >::staticInst.

◆ doneTargCalc()

|

inline |

Checks whether or not this instruction has had its branch target calculated yet.

For now it is not utilized and is hacked to be always false.

- Todo:

- : Actually use this instruction.

Definition at line 488 of file base_dyn_inst.hh.

◆ dump() [1/2]

| void BaseDynInst< Impl >::dump |

Dumps out contents of this BaseDynInst.

Definition at line 184 of file base_dyn_inst_impl.hh.

References cprintf(), and MipsISA::pc.

◆ dump() [2/2]

| void BaseDynInst< Impl >::dump | ( | std::string & | outstring | ) |

Dumps out contents of this BaseDynInst into given string.

Definition at line 193 of file base_dyn_inst_impl.hh.

References MipsISA::pc, and ArmISA::s.

◆ eaSrcsReady()

| bool BaseDynInst< Impl >::eaSrcsReady |

Returns whether or not the eff.

addr. source registers are ready.

Definition at line 224 of file base_dyn_inst_impl.hh.

References ArmISA::i.

◆ effAddrValid() [1/2]

|

inline |

Is the effective virtual address valid.

Definition at line 277 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::EffAddrValid, and BaseDynInst< Impl >::instFlags.

◆ effAddrValid() [2/2]

|

inline |

Definition at line 278 of file base_dyn_inst.hh.

References ArmISA::b, BaseDynInst< Impl >::EffAddrValid, and BaseDynInst< Impl >::instFlags.

◆ flattenDestReg()

|

inline |

Flattens a destination architectural register index into a logical index.

Definition at line 431 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::_flatDestRegIdx.

◆ flattenedDestRegIdx()

|

inline |

Returns the flattened register index of the i'th destination register.

Definition at line 390 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::_flatDestRegIdx.

◆ getAddrMonitor()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 1063 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and BaseDynInst< Impl >::threadNumber.

◆ getCpuPtr()

|

inline |

Definition at line 158 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu.

◆ getFault() [1/2]

|

inline |

TODO: This I added for the LSQRequest side to be able to modify the fault.

There should be a better mechanism in place.

Definition at line 481 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::fault.

◆ getFault() [2/2]

|

inline |

Returns the fault type.

Definition at line 478 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::fault.

◆ getHtmTransactionalDepth()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 598 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::htmDepth, and BaseDynInst< Impl >::inHtmTransactionalState().

◆ getHtmTransactionUid()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 578 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::HtmFromTransaction, BaseDynInst< Impl >::htmUid, and BaseDynInst< Impl >::instFlags.

Referenced by BaseDynInst< Impl >::clearHtmTransactionalState().

◆ getInstListIt()

|

inline |

Returns iterator to this instruction in the list of all insts.

Definition at line 1025 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instListIt.

◆ hasRequest()

|

inline |

Has this instruction generated a memory request.

Definition at line 1020 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::ReqMade.

◆ hitExternalSnoop() [1/2]

|

inline |

True if the address hit a external snoop while sitting in the LSQ.

If this is true and a older instruction sees it, this instruction must reexecute

Definition at line 351 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::HitExternalSnoop, and BaseDynInst< Impl >::instFlags.

◆ hitExternalSnoop() [2/2]

|

inline |

Definition at line 352 of file base_dyn_inst.hh.

References ArmISA::f, BaseDynInst< Impl >::HitExternalSnoop, and BaseDynInst< Impl >::instFlags.

◆ inHtmTransactionalState()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 592 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::HtmFromTransaction, and BaseDynInst< Impl >::instFlags.

Referenced by BaseDynInst< Impl >::clearHtmTransactionalState(), and BaseDynInst< Impl >::getHtmTransactionalDepth().

◆ initiateHtmCmd()

|

overridevirtual |

Initiate an HTM command, e.g.

tell Ruby we're starting/stopping a transaction

Implements ExecContext.

Definition at line 1084 of file base_dyn_inst.hh.

◆ initiateMemAMO()

|

override |

Definition at line 1106 of file base_dyn_inst.hh.

References addr.

◆ initiateMemRead()

|

override |

Definition at line 1071 of file base_dyn_inst.hh.

References addr.

◆ initVars()

|

private |

Function to initialize variables in the constructors.

Definition at line 91 of file base_dyn_inst_impl.hh.

References DPRINTF, NoFault, and ArmISA::status.

Referenced by BaseDynInst< Impl >::BaseDynInst().

◆ instAddr()

|

inline |

Read the PC of this instruction.

Definition at line 970 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::pc.

◆ isAtCommit()

|

inline |

Definition at line 861 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::AtCommit, and BaseDynInst< Impl >::status.

◆ isAtomic()

|

inline |

Definition at line 529 of file base_dyn_inst.hh.

References StaticInst::isAtomic(), and BaseDynInst< Impl >::staticInst.

◆ isCall()

|

inline |

Definition at line 538 of file base_dyn_inst.hh.

References StaticInst::isCall(), and BaseDynInst< Impl >::staticInst.

◆ isCommitted()

|

inline |

Returns whether or not this instruction is committed.

Definition at line 867 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Committed, and BaseDynInst< Impl >::status.

◆ isCompleted()

|

inline |

Returns whether or not this instruction is completed.

Definition at line 818 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Completed, and BaseDynInst< Impl >::status.

◆ isCondCtrl()

|

inline |

Definition at line 542 of file base_dyn_inst.hh.

References StaticInst::isCondCtrl(), and BaseDynInst< Impl >::staticInst.

◆ isCondDelaySlot()

|

inline |

Definition at line 544 of file base_dyn_inst.hh.

References StaticInst::isCondDelaySlot(), and BaseDynInst< Impl >::staticInst.

◆ isControl()

|

inline |

Definition at line 537 of file base_dyn_inst.hh.

References StaticInst::isControl(), and BaseDynInst< Impl >::staticInst.

◆ isDataPrefetch()

|

inline |

Definition at line 533 of file base_dyn_inst.hh.

References StaticInst::isDataPrefetch(), and BaseDynInst< Impl >::staticInst.

◆ isDelayedCommit()

|

inline |

Definition at line 567 of file base_dyn_inst.hh.

References StaticInst::isDelayedCommit(), and BaseDynInst< Impl >::staticInst.

◆ isDirectCtrl()

|

inline |

Definition at line 540 of file base_dyn_inst.hh.

References StaticInst::isDirectCtrl(), and BaseDynInst< Impl >::staticInst.

◆ isExecuted()

|

inline |

Returns whether or not this instruction has executed.

Definition at line 848 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Executed, and BaseDynInst< Impl >::status.

◆ isFirstMicroop()

|

inline |

Definition at line 569 of file base_dyn_inst.hh.

References StaticInst::isFirstMicroop(), and BaseDynInst< Impl >::staticInst.

◆ isFloating()

|

inline |

Definition at line 535 of file base_dyn_inst.hh.

References StaticInst::isFloating(), and BaseDynInst< Impl >::staticInst.

◆ isHtmCancel()

|

inline |

Definition at line 574 of file base_dyn_inst.hh.

References StaticInst::isHtmCancel(), and BaseDynInst< Impl >::staticInst.

◆ isHtmCmd()

|

inline |

Definition at line 575 of file base_dyn_inst.hh.

References StaticInst::isHtmCmd(), and BaseDynInst< Impl >::staticInst.

◆ isHtmStart()

|

inline |

Definition at line 572 of file base_dyn_inst.hh.

References StaticInst::isHtmStart(), and BaseDynInst< Impl >::staticInst.

◆ isHtmStop()

|

inline |

Definition at line 573 of file base_dyn_inst.hh.

References StaticInst::isHtmStop(), and BaseDynInst< Impl >::staticInst.

◆ isIndirectCtrl()

|

inline |

Definition at line 541 of file base_dyn_inst.hh.

References StaticInst::isIndirectCtrl(), and BaseDynInst< Impl >::staticInst.

◆ isInIQ()

|

inline |

Returns whether or not this instruction has issued.

Definition at line 884 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::IqEntry, and BaseDynInst< Impl >::status.

◆ isInLSQ()

|

inline |

Returns whether or not this instruction is in the LSQ.

Definition at line 902 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::LsqEntry, and BaseDynInst< Impl >::status.

◆ isInROB()

|

inline |

Returns whether or not this instruction is in the ROB.

Definition at line 920 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::RobEntry, and BaseDynInst< Impl >::status.

◆ isInstPrefetch()

|

inline |

Definition at line 532 of file base_dyn_inst.hh.

References StaticInst::isInstPrefetch(), and BaseDynInst< Impl >::staticInst.

◆ isInteger()

|

inline |

Definition at line 534 of file base_dyn_inst.hh.

References StaticInst::isInteger(), and BaseDynInst< Impl >::staticInst.

◆ isIprAccess()

|

inline |

Definition at line 562 of file base_dyn_inst.hh.

References StaticInst::isIprAccess(), and BaseDynInst< Impl >::staticInst.

◆ isIssued()

|

inline |

Returns whether or not this instruction has issued.

Definition at line 839 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Issued, and BaseDynInst< Impl >::status.

◆ isLastMicroop()

|

inline |

Definition at line 568 of file base_dyn_inst.hh.

References StaticInst::isLastMicroop(), and BaseDynInst< Impl >::staticInst.

◆ isLoad()

|

inline |

Definition at line 527 of file base_dyn_inst.hh.

References StaticInst::isLoad(), and BaseDynInst< Impl >::staticInst.

◆ isMacroop()

|

inline |

Definition at line 565 of file base_dyn_inst.hh.

References StaticInst::isMacroop(), and BaseDynInst< Impl >::staticInst.

◆ isMemBarrier()

|

inline |

Definition at line 558 of file base_dyn_inst.hh.

References StaticInst::isMemBarrier(), and BaseDynInst< Impl >::staticInst.

◆ isMemRef()

|

inline |

Definition at line 526 of file base_dyn_inst.hh.

References StaticInst::isMemRef(), and BaseDynInst< Impl >::staticInst.

◆ isMicroBranch()

|

inline |

Definition at line 570 of file base_dyn_inst.hh.

References StaticInst::isMicroBranch(), and BaseDynInst< Impl >::staticInst.

◆ isMicroop()

|

inline |

Definition at line 566 of file base_dyn_inst.hh.

References StaticInst::isMicroop(), and BaseDynInst< Impl >::staticInst.

◆ isNonSpeculative()

|

inline |

Definition at line 560 of file base_dyn_inst.hh.

References StaticInst::isNonSpeculative(), and BaseDynInst< Impl >::staticInst.

◆ isNop()

|

inline |

Definition at line 525 of file base_dyn_inst.hh.

References StaticInst::isNop(), and BaseDynInst< Impl >::staticInst.

◆ isPinnedRegsRenamed()

|

inline |

Returns whether pinned registers are renamed.

Definition at line 929 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::PinnedRegsRenamed, and BaseDynInst< Impl >::status.

◆ isPinnedRegsSquashDone()

|

inline |

Return whether dest registers' pinning status updated after squash.

Definition at line 954 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::PinnedRegsSquashDone, and BaseDynInst< Impl >::status.

◆ isPinnedRegsWritten()

|

inline |

Returns whether destination registers are written.

Definition at line 941 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::PinnedRegsWritten, and BaseDynInst< Impl >::status.

◆ isQuiesce()

|

inline |

Definition at line 561 of file base_dyn_inst.hh.

References StaticInst::isQuiesce(), and BaseDynInst< Impl >::staticInst.

◆ isReadySrcRegIdx()

|

inline |

Returns if a source register is ready.

Definition at line 809 of file base_dyn_inst.hh.

◆ isResultReady()

|

inline |

Returns whether or not the result is ready.

Definition at line 824 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::ResultReady, and BaseDynInst< Impl >::status.

◆ isReturn()

|

inline |

Definition at line 539 of file base_dyn_inst.hh.

References StaticInst::isReturn(), and BaseDynInst< Impl >::staticInst.

◆ isSerializeAfter()

|

inline |

Definition at line 553 of file base_dyn_inst.hh.

References StaticInst::isSerializeAfter(), BaseDynInst< Impl >::SerializeAfter, BaseDynInst< Impl >::staticInst, and BaseDynInst< Impl >::status.

◆ isSerializeBefore()

|

inline |

Definition at line 548 of file base_dyn_inst.hh.

References StaticInst::isSerializeBefore(), BaseDynInst< Impl >::SerializeBefore, BaseDynInst< Impl >::staticInst, and BaseDynInst< Impl >::status.

◆ isSerializeHandled()

|

inline |

Checks if the serialization part of this instruction has been handled.

This does not apply to the temporary serializing state; it only applies to this instruction's own permanent serializing state.

Definition at line 654 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeHandled, and BaseDynInst< Impl >::status.

◆ isSerializing()

|

inline |

Definition at line 546 of file base_dyn_inst.hh.

References StaticInst::isSerializing(), and BaseDynInst< Impl >::staticInst.

◆ isSquashAfter()

|

inline |

Definition at line 557 of file base_dyn_inst.hh.

References StaticInst::isSquashAfter(), and BaseDynInst< Impl >::staticInst.

◆ isSquashed()

|

inline |

Returns whether or not this instruction is squashed.

Definition at line 873 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Squashed, and BaseDynInst< Impl >::status.

◆ isSquashedInIQ()

|

inline |

Returns whether or not this instruction is squashed in the IQ.

Definition at line 890 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SquashedInIQ, and BaseDynInst< Impl >::status.

◆ isSquashedInLSQ()

|

inline |

Returns whether or not this instruction is squashed in the LSQ.

Definition at line 908 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SquashedInLSQ, and BaseDynInst< Impl >::status.

◆ isSquashedInROB()

|

inline |

Returns whether or not this instruction is squashed in the ROB.

Definition at line 926 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SquashedInROB, and BaseDynInst< Impl >::status.

◆ isStore()

|

inline |

Definition at line 528 of file base_dyn_inst.hh.

References StaticInst::isStore(), and BaseDynInst< Impl >::staticInst.

◆ isStoreConditional()

|

inline |

Definition at line 530 of file base_dyn_inst.hh.

References StaticInst::isStoreConditional(), and BaseDynInst< Impl >::staticInst.

◆ isSyscall()

|

inline |

Definition at line 564 of file base_dyn_inst.hh.

References StaticInst::isSyscall(), and BaseDynInst< Impl >::staticInst.

◆ isTempSerializeAfter()

|

inline |

Checks if this serializeAfter is only temporarily set.

Definition at line 644 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeAfter, and BaseDynInst< Impl >::status.

◆ isTempSerializeBefore()

|

inline |

Checks if this serializeBefore is only temporarily set.

Definition at line 635 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeBefore, and BaseDynInst< Impl >::status.

◆ isThreadSync()

|

inline |

Definition at line 545 of file base_dyn_inst.hh.

References StaticInst::isThreadSync(), and BaseDynInst< Impl >::staticInst.

◆ isTranslationDelayed()

|

inline |

Returns true if the DTB address translation is being delayed due to a hw page table walk.

Definition at line 359 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::translationCompleted(), and BaseDynInst< Impl >::translationStarted().

◆ isUncondCtrl()

|

inline |

Definition at line 543 of file base_dyn_inst.hh.

References StaticInst::isUncondCtrl(), and BaseDynInst< Impl >::staticInst.

◆ isUnverifiable()

|

inline |

Definition at line 563 of file base_dyn_inst.hh.

References StaticInst::isUnverifiable(), and BaseDynInst< Impl >::staticInst.

◆ isVector()

|

inline |

Definition at line 536 of file base_dyn_inst.hh.

References StaticInst::isVector(), and BaseDynInst< Impl >::staticInst.

◆ isWriteBarrier()

|

inline |

Definition at line 559 of file base_dyn_inst.hh.

References StaticInst::isWriteBarrier(), and BaseDynInst< Impl >::staticInst.

◆ markSrcRegReady() [1/2]

| void BaseDynInst< Impl >::markSrcRegReady |

Records that one of the source registers is ready.

Definition at line 204 of file base_dyn_inst_impl.hh.

References DPRINTF.

◆ markSrcRegReady() [2/2]

| void BaseDynInst< Impl >::markSrcRegReady | ( | RegIndex | src_idx | ) |

Marks a specific register as ready.

Definition at line 215 of file base_dyn_inst_impl.hh.

◆ memOpDone() [1/2]

|

inline |

Whether or not the memory operation is done.

Definition at line 281 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::MemOpDone.

◆ memOpDone() [2/2]

|

inline |

Definition at line 282 of file base_dyn_inst.hh.

References ArmISA::f, BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::MemOpDone.

◆ microPC()

|

inline |

Read the micro PC of this instruction.

Definition at line 976 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::pc.

◆ mispredicted()

|

inline |

Returns whether the instruction mispredicted.

Definition at line 515 of file base_dyn_inst.hh.

References ArmISA::advancePC(), BaseDynInst< Impl >::pc, BaseDynInst< Impl >::predPC, and BaseDynInst< Impl >::staticInst.

◆ mwait()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 1053 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and BaseDynInst< Impl >::threadNumber.

◆ mwaitAtomic()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 1058 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu, and BaseDynInst< Impl >::threadNumber.

◆ newHtmTransactionUid()

|

inlineoverridevirtual |

◆ nextInstAddr()

|

inline |

Read the PC of the next instruction.

Definition at line 973 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::pc.

◆ notAnInst()

|

inline |

Definition at line 284 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::NotAnInst.

◆ numCCDestRegs()

|

inline |

Definition at line 673 of file base_dyn_inst.hh.

References StaticInst::numCCDestRegs(), and BaseDynInst< Impl >::staticInst.

◆ numDestRegs()

|

inline |

Returns the number of destination registers.

Definition at line 667 of file base_dyn_inst.hh.

References StaticInst::numDestRegs(), and BaseDynInst< Impl >::staticInst.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ numFPDestRegs()

|

inline |

Definition at line 671 of file base_dyn_inst.hh.

References StaticInst::numFPDestRegs(), and BaseDynInst< Impl >::staticInst.

◆ numIntDestRegs()

|

inline |

Definition at line 672 of file base_dyn_inst.hh.

References StaticInst::numIntDestRegs(), and BaseDynInst< Impl >::staticInst.

◆ numSrcRegs()

|

inline |

Returns the number of source registers.

Definition at line 664 of file base_dyn_inst.hh.

References StaticInst::numSrcRegs(), and BaseDynInst< Impl >::staticInst.

◆ numVecDestRegs()

|

inline |

Definition at line 674 of file base_dyn_inst.hh.

References StaticInst::numVecDestRegs(), and BaseDynInst< Impl >::staticInst.

◆ numVecElemDestRegs()

|

inline |

Definition at line 676 of file base_dyn_inst.hh.

References StaticInst::numVecElemDestRegs(), and BaseDynInst< Impl >::staticInst.

◆ numVecPredDestRegs()

|

inline |

Definition at line 681 of file base_dyn_inst.hh.

References StaticInst::numVecPredDestRegs(), and BaseDynInst< Impl >::staticInst.

◆ opClass()

|

inline |

Returns the opclass of this instruction.

Definition at line 657 of file base_dyn_inst.hh.

References StaticInst::opClass(), and BaseDynInst< Impl >::staticInst.

◆ pcState() [1/2]

|

inlineoverridevirtual |

Read the PC state of this instruction.

Implements ExecContext.

Definition at line 964 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::pc.

◆ pcState() [2/2]

|

inlineoverridevirtual |

Set the PC state of this instruction.

Implements ExecContext.

Definition at line 967 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::pc, and X86ISA::val.

◆ popResult()

|

inline |

Pops a result off the instResult queue.

If the result stack is empty, return the default value.

Definition at line 699 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instResult, and ArmISA::t.

◆ possibleLoadViolation() [1/2]

|

inline |

True if this address was found to match a previous load and they issued out of order.

If that happend, then it's only a problem if an incoming snoop invalidate modifies the line, in which case we need to squash. If nothing modified the line the order doesn't matter.

Definition at line 337 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::PossibleLoadViolation.

◆ possibleLoadViolation() [2/2]

|

inline |

Definition at line 342 of file base_dyn_inst.hh.

References ArmISA::f, BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::PossibleLoadViolation.

◆ predInstAddr()

|

inline |

Returns the predicted PC immediately after the branch.

Definition at line 496 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::predPC.

◆ predMicroPC()

|

inline |

Returns the predicted micro PC after the branch.

Definition at line 502 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::predPC.

◆ predNextInstAddr()

|

inline |

Returns the predicted PC two instructions after the branch.

Definition at line 499 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::predPC.

◆ prevDestRegIdx()

|

inline |

Returns the physical register index of the previous physical register that remapped to the same logical register index.

Definition at line 399 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::_prevDestRegIdx.

Referenced by BaseO3DynInst< Impl >::forwardOldRegs().

◆ readMemAccPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 991 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::MemAccPredicate.

◆ readPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 978 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::Predicate.

◆ readPredTaken()

|

inline |

Returns whether the instruction was predicted taken or not.

Definition at line 505 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::PredTaken.

◆ readPredTarg()

|

inline |

Definition at line 493 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::predPC.

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements ExecContext.

Definition at line 1033 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::thread.

◆ readyToCommit()

|

inline |

Returns whether or not this instruction is ready to commit.

Definition at line 857 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::CanCommit, and BaseDynInst< Impl >::status.

◆ readyToIssue()

|

inline |

Returns whether or not this instruction is ready to issue.

Definition at line 830 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::CanIssue, and BaseDynInst< Impl >::status.

◆ recordResult()

|

inline |

Records changes to result?

Definition at line 274 of file base_dyn_inst.hh.

References ArmISA::f, BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::RecordResult.

◆ removeInLSQ()

|

inline |

Sets this instruction as a entry the LSQ.

Definition at line 899 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::LsqEntry, and BaseDynInst< Impl >::status.

◆ renamedDestRegIdx()

|

inline |

Returns the physical register index of the i'th destination register.

Definition at line 373 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx.

◆ renameDestReg()

|

inline |

Renames a destination register to a physical register.

Also records the previous physical register that the logical register mapped to.

Definition at line 408 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::_destRegIdx, BaseDynInst< Impl >::_prevDestRegIdx, PhysRegId::isPinned(), and BaseDynInst< Impl >::setPinnedRegsRenamed().

◆ renamedSrcRegIdx()

|

inline |

Returns the physical register index of the i'th source register.

Definition at line 380 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx, and ArmISA::MaxInstSrcRegs.

◆ renameSrcReg()

|

inline |

Renames a source logical register to the physical register which has/will produce that logical register's result.

- Todo:

- : add in whether or not the source register is ready.

Definition at line 422 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::_srcRegIdx.

◆ requestorId()

|

inline |

Read this CPU's data requestor ID.

Definition at line 472 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu.

◆ resultSize()

|

inline |

Return the size of the instResult queue.

Definition at line 693 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instResult.

◆ setAtCommit()

|

inline |

Definition at line 859 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::AtCommit, and BaseDynInst< Impl >::status.

◆ setCanCommit()

|

inline |

Sets this instruction as ready to commit.

Definition at line 851 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::CanCommit, and BaseDynInst< Impl >::status.

◆ setCanIssue()

|

inline |

Sets this instruction as ready to issue.

Definition at line 827 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::CanIssue, and BaseDynInst< Impl >::status.

◆ setCCRegOperand()

|

inlineoverridevirtual |

Records a CC register being set to a value.

Implements ExecContext.

Reimplemented in BaseO3DynInst< Impl >.

Definition at line 765 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::setScalarResult(), and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setCCRegOperand().

◆ setCommitted()

|

inline |

Sets this instruction as committed.

Definition at line 864 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Committed, and BaseDynInst< Impl >::status.

◆ setCompleted()

|

inline |

Sets this instruction as completed.

Definition at line 815 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Completed, and BaseDynInst< Impl >::status.

◆ setExecuted()

|

inline |

Sets this instruction as executed.

Definition at line 845 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Executed, and BaseDynInst< Impl >::status.

◆ setFloatRegOperandBits()

|

inlineoverridevirtual |

Records an fp register being set to an integer value.

Implements ExecContext.

Reimplemented in BaseO3DynInst< Impl >.

Definition at line 780 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::setScalarResult(), and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setFloatRegOperandBits().

◆ setHtmTransactionalState()

|

inline |

Definition at line 607 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::htmDepth, BaseDynInst< Impl >::HtmFromTransaction, BaseDynInst< Impl >::htmUid, and BaseDynInst< Impl >::instFlags.

◆ setInIQ()

|

inline |

Sets this instruction as a entry the IQ.

Definition at line 878 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::IqEntry, and BaseDynInst< Impl >::status.

◆ setInLSQ()

|

inline |

Sets this instruction as a entry the LSQ.

Definition at line 896 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::LsqEntry, and BaseDynInst< Impl >::status.

◆ setInROB()

|

inline |

Sets this instruction as a entry the ROB.

Definition at line 914 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::RobEntry, and BaseDynInst< Impl >::status.

◆ setInstListIt()

|

inline |

Sets iterator for this instruction in the list of all insts.

Definition at line 1028 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instListIt.

◆ setIntRegOperand()

|

inlineoverridevirtual |

Records an integer register being set to a value.

Implements ExecContext.

Reimplemented in BaseO3DynInst< Impl >.

Definition at line 758 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::setScalarResult(), and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setIntRegOperand().

◆ setIssued()

|

inline |

Sets this instruction as issued from the IQ.

Definition at line 836 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Issued, and BaseDynInst< Impl >::status.

◆ setMemAccPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 997 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, BaseDynInst< Impl >::MemAccPredicate, and X86ISA::val.

◆ setNotAnInst()

|

inline |

Definition at line 285 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::NotAnInst.

◆ setPinnedRegsRenamed()

|

inline |

Sets the destination registers as renamed.

Definition at line 933 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::PinnedRegsRenamed, BaseDynInst< Impl >::PinnedRegsSquashDone, BaseDynInst< Impl >::PinnedRegsWritten, and BaseDynInst< Impl >::status.

Referenced by BaseDynInst< Impl >::renameDestReg().

◆ setPinnedRegsSquashDone()

|

inline |

Sets dest registers' status updated after squash.

Definition at line 958 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::PinnedRegsSquashDone, and BaseDynInst< Impl >::status.

◆ setPinnedRegsWritten()

|

inline |

Sets destination registers as written.

Definition at line 945 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::PinnedRegsRenamed, BaseDynInst< Impl >::PinnedRegsSquashDone, BaseDynInst< Impl >::PinnedRegsWritten, and BaseDynInst< Impl >::status.

◆ setPredicate()

|

inlineoverridevirtual |

Implements ExecContext.

Definition at line 981 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, BaseDynInst< Impl >::Predicate, Trace::InstRecord::setPredicate(), BaseDynInst< Impl >::traceData, and X86ISA::val.

◆ setPredTaken()

|

inline |

Definition at line 508 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::PredTaken.

◆ setPredTarg()

|

inline |

Set the predicted target of this current instruction.

Definition at line 491 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::predPC.

◆ setRequest()

|

inline |

Assert this instruction has generated a memory request.

Definition at line 1022 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::ReqMade.

◆ setResultReady()

|

inline |

Marks the result as ready.

Definition at line 821 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::ResultReady, and BaseDynInst< Impl >::status.

◆ setScalarResult()

|

inline |

Pushes a result onto the instResult queue.

Scalar result.

Definition at line 714 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, BaseDynInst< Impl >::instResult, BaseDynInst< Impl >::RecordResult, InstResult::Scalar, and ArmISA::t.

Referenced by BaseDynInst< Impl >::setCCRegOperand(), BaseDynInst< Impl >::setFloatRegOperandBits(), and BaseDynInst< Impl >::setIntRegOperand().

◆ setSerializeAfter()

|

inline |

Temporarily sets this instruction as a serialize after instruction.

Definition at line 638 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeAfter, and BaseDynInst< Impl >::status.

◆ setSerializeBefore()

|

inline |

Temporarily sets this instruction as a serialize before instruction.

Definition at line 629 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeBefore, and BaseDynInst< Impl >::status.

◆ setSerializeHandled()

|

inline |

Sets the serialization part of this instruction as handled.

Definition at line 647 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SerializeHandled, and BaseDynInst< Impl >::status.

◆ setSquashed()

| void BaseDynInst< Impl >::setSquashed |

Sets this instruction as squashed.

Definition at line 242 of file base_dyn_inst_impl.hh.

References PhysRegId::incrNumPinnedWrites(), PhysRegId::incrNumPinnedWritesToComplete(), PhysRegId::isPinned(), and ArmISA::status.

◆ setSquashedInIQ()

|

inline |

Sets this instruction as squashed in the IQ.

Definition at line 887 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Squashed, BaseDynInst< Impl >::SquashedInIQ, and BaseDynInst< Impl >::status.

◆ setSquashedInLSQ()

|

inline |

Sets this instruction as squashed in the LSQ.

Definition at line 905 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::Squashed, BaseDynInst< Impl >::SquashedInLSQ, and BaseDynInst< Impl >::status.

◆ setSquashedInROB()

|

inline |

Sets this instruction as squashed in the ROB.

Definition at line 923 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::SquashedInROB, and BaseDynInst< Impl >::status.

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements ExecContext.

Definition at line 1040 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::thread.

◆ setThreadState()

|

inline |

Sets the pointer to the thread state.

Definition at line 1006 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::thread.

◆ setTid()

|

inline |

Sets the thread id.

Definition at line 1003 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::threadNumber.

◆ setVecElemOperand()

|

inlineoverridevirtual |

Record a vector register being set to a value.

Implements ExecContext.

Reimplemented in BaseO3DynInst< Impl >.

Definition at line 787 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::setVecElemResult(), and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setVecElemOperand().

◆ setVecElemResult()

|

inline |

Vector element result.

Definition at line 736 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, BaseDynInst< Impl >::instResult, BaseDynInst< Impl >::RecordResult, ArmISA::t, and InstResult::VecElem.

Referenced by BaseDynInst< Impl >::setVecElemOperand().

◆ setVecPredRegOperand()

|

inlineoverridevirtual |

Record a vector register being set to a value.

Implements ExecContext.

Reimplemented in BaseO3DynInst< Impl >.

Definition at line 795 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::setVecPredResult(), and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setVecPredRegOperand().

◆ setVecPredResult()

|

inline |

Predicate result.

Definition at line 747 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, BaseDynInst< Impl >::instResult, BaseDynInst< Impl >::RecordResult, ArmISA::t, and InstResult::VecPredReg.

Referenced by BaseDynInst< Impl >::setVecPredRegOperand().

◆ setVecRegOperand()

|

inlineoverridevirtual |

Record a vector register being set to a value.

Implements ExecContext.

Reimplemented in BaseO3DynInst< Impl >.

Definition at line 772 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::setVecResult(), and X86ISA::val.

Referenced by BaseO3DynInst< Impl >::setVecRegOperand().

◆ setVecResult()

Full vector result.

Definition at line 725 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, BaseDynInst< Impl >::instResult, BaseDynInst< Impl >::RecordResult, ArmISA::t, and InstResult::VecReg.

Referenced by BaseDynInst< Impl >::setVecRegOperand().

◆ socketId()

|

inline |

Read this CPU's Socket ID.

Definition at line 469 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::cpu.

◆ srcRegIdx()

|

inline |

Returns the logical register index of the i'th source register.

Definition at line 690 of file base_dyn_inst.hh.

References ArmISA::i, StaticInst::srcRegIdx(), and BaseDynInst< Impl >::staticInst.

◆ strictlyOrdered() [1/2]

|

inline |

Is this instruction's memory access strictly ordered?

Definition at line 1016 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::IsStrictlyOrdered.

◆ strictlyOrdered() [2/2]

|

inline |

Definition at line 1017 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, BaseDynInst< Impl >::IsStrictlyOrdered, and PowerISA::so.

◆ tcBase()

|

inlineoverridevirtual |

Returns the thread context.

Implements ExecContext.

Definition at line 1009 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::thread.

◆ translationCompleted() [1/2]

|

inline |

True if the DTB address translation has completed.

Definition at line 328 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::TranslationCompleted.

Referenced by BaseDynInst< Impl >::isTranslationDelayed().

◆ translationCompleted() [2/2]

|

inline |

Definition at line 329 of file base_dyn_inst.hh.

References ArmISA::f, BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::TranslationCompleted.

◆ translationStarted() [1/2]

|

inline |

True if the DTB address translation has started.

Definition at line 324 of file base_dyn_inst.hh.

References BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::TranslationStarted.

Referenced by BaseDynInst< Impl >::isTranslationDelayed().

◆ translationStarted() [2/2]

|

inline |

Definition at line 325 of file base_dyn_inst.hh.

References ArmISA::f, BaseDynInst< Impl >::instFlags, and BaseDynInst< Impl >::TranslationStarted.

◆ writeMem()

|

override |

Definition at line 1093 of file base_dyn_inst.hh.

Member Data Documentation

◆ _destRegIdx

|

protected |

Physical register index of the destination registers of this instruction.

Definition at line 259 of file base_dyn_inst.hh.

Referenced by BaseO3DynInst< Impl >::getWritableVecPredRegOperand(), BaseO3DynInst< Impl >::getWritableVecRegOperand(), BaseDynInst< Impl >::renamedDestRegIdx(), BaseDynInst< Impl >::renameDestReg(), BaseO3DynInst< Impl >::setCCRegOperand(), BaseO3DynInst< Impl >::setFloatRegOperandBits(), BaseO3DynInst< Impl >::setIntRegOperand(), BaseO3DynInst< Impl >::setVecElemOperand(), BaseO3DynInst< Impl >::setVecLaneOperandT(), BaseO3DynInst< Impl >::setVecPredRegOperand(), and BaseO3DynInst< Impl >::setVecRegOperand().

◆ _flatDestRegIdx

|

protected |

Flattened register index of the destination registers of this instruction.

Definition at line 254 of file base_dyn_inst.hh.

Referenced by BaseDynInst< Impl >::flattenDestReg(), and BaseDynInst< Impl >::flattenedDestRegIdx().

◆ _prevDestRegIdx

|

protected |