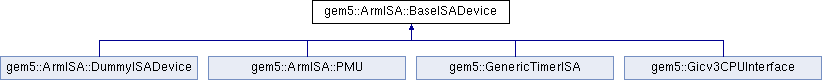

Base class for devices that use the MiscReg interfaces. More...

#include <isa_device.hh>

Public Member Functions | |

| BaseISADevice () | |

| virtual | ~BaseISADevice () |

| virtual void | setISA (ISA *isa) |

| virtual void | setThreadContext (ThreadContext *tc) |

| virtual void | setMiscReg (int misc_reg, RegVal val)=0 |

| Write to a system register belonging to this device. | |

| virtual RegVal | readMiscReg (int misc_reg)=0 |

| Read a system register belonging to this device. | |

Protected Attributes | |

| ISA * | isa |

Detailed Description

Base class for devices that use the MiscReg interfaces.

This class provides a well-defined interface that the ArmISA class can use when forwarding MiscReg accesses to a device model (e.g., a PMU or GIC).

Definition at line 61 of file isa_device.hh.

Constructor & Destructor Documentation

◆ BaseISADevice()

| gem5::ArmISA::BaseISADevice::BaseISADevice | ( | ) |

Definition at line 49 of file isa_device.cc.

References isa.

Referenced by gem5::ArmISA::DummyISADevice::DummyISADevice(), gem5::Gicv3CPUInterface::Gicv3CPUInterface(), and gem5::ArmISA::PMU::PMU().

◆ ~BaseISADevice()

|

inlinevirtual |

Definition at line 65 of file isa_device.hh.

Member Function Documentation

◆ readMiscReg()

|

pure virtual |

Read a system register belonging to this device.

- Parameters

-

misc_reg Register number (see regs/misc.hh)

- Returns

- Register value.

Implemented in gem5::ArmISA::DummyISADevice, gem5::ArmISA::PMU, gem5::GenericTimerISA, and gem5::Gicv3CPUInterface.

Referenced by gem5::ArmISA::ISA::readMiscReg().

◆ setISA()

|

virtual |

Definition at line 55 of file isa_device.cc.

References isa.

Referenced by gem5::Gicv3CPUInterface::Gicv3CPUInterface().

◆ setMiscReg()

|

pure virtual |

Write to a system register belonging to this device.

Implemented in gem5::ArmISA::DummyISADevice, gem5::ArmISA::PMU, gem5::GenericTimerISA, and gem5::Gicv3CPUInterface.

References gem5::X86ISA::val.

Referenced by gem5::ArmISA::ISA::setMiscReg().

◆ setThreadContext()

|

inlinevirtual |

Reimplemented in gem5::ArmISA::PMU, and gem5::Gicv3CPUInterface.

Definition at line 68 of file isa_device.hh.

Member Data Documentation

◆ isa

|

protected |

Definition at line 87 of file isa_device.hh.

Referenced by BaseISADevice(), gem5::Gicv3CPUInterface::bpr1(), gem5::Gicv3CPUInterface::dropPriority(), gem5::Gicv3CPUInterface::eoiMaintenanceInterruptStatus(), gem5::Gicv3CPUInterface::getHPPIR1(), gem5::Gicv3CPUInterface::getHPPVILR(), gem5::Gicv3CPUInterface::groupEnabled(), gem5::Gicv3CPUInterface::groupPriorityMask(), gem5::Gicv3CPUInterface::highestActiveGroup(), gem5::Gicv3CPUInterface::highestActivePriority(), gem5::Gicv3CPUInterface::hppiCanPreempt(), gem5::Gicv3CPUInterface::hppviCanPreempt(), gem5::Gicv3CPUInterface::isEOISplitMode(), gem5::Gicv3CPUInterface::maintenanceInterruptStatus(), gem5::Gicv3CPUInterface::readBankedMiscReg(), gem5::Gicv3CPUInterface::readMiscReg(), gem5::Gicv3CPUInterface::setBankedMiscReg(), setISA(), gem5::Gicv3CPUInterface::setMiscReg(), gem5::Gicv3CPUInterface::virtualActivateIRQ(), gem5::Gicv3CPUInterface::virtualDeactivateIRQ(), gem5::Gicv3CPUInterface::virtualDropPriority(), gem5::Gicv3CPUInterface::virtualFindActive(), gem5::Gicv3CPUInterface::virtualGroupPriorityMask(), gem5::Gicv3CPUInterface::virtualHighestActivePriority(), gem5::Gicv3CPUInterface::virtualIncrementEOICount(), gem5::Gicv3CPUInterface::virtualIsEOISplitMode(), and gem5::Gicv3CPUInterface::virtualUpdate().

The documentation for this class was generated from the following files:

- arch/arm/isa_device.hh

- arch/arm/isa_device.cc

Generated on Sat Oct 18 2025 08:06:56 for gem5 by doxygen 1.14.0