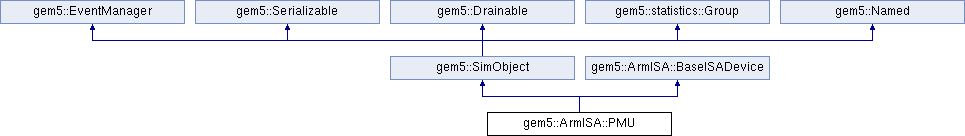

Model of an ARM PMU version 3. More...

#include <pmu.hh>

Classes | |

| struct | CounterState |

| State of a counter within the PMU. More... | |

| struct | PMUEvent |

| Event definition base class. More... | |

| struct | RegularEvent |

| struct | Stats |

| class | SWIncrementEvent |

Public Types | |

| using | EventTypeId = std::underlying_type_t<enums::EventTypeId> |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| PMU (const ArmPMUParams &p) | |

| ~PMU () | |

| void | addEventProbe (EventTypeId id, SimObject *obj, const char *name) |

| void | addSoftwareIncrementEvent (EventTypeId id) |

| void | registerEvent (EventTypeId id) |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| void | drainResume () override |

| Resume execution after a successful drain. | |

| void | regProbeListeners () override |

| Register probe listeners for this object. | |

| void | setThreadContext (ThreadContext *tc) override |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Set a register within the PMU. | |

| RegVal | readMiscReg (int misc_reg) override |

| Read a register within the PMU. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::ArmISA::BaseISADevice | |

| BaseISADevice () | |

| virtual | ~BaseISADevice () |

| virtual void | setISA (ISA *isa) |

Protected Member Functions | |

| BitUnion32 (PMCR_t) Bitfield< 0 > e | |

| EndBitUnion (PMCR_t) BitUnion32(PMSELR_t) Bitfield< 4 | |

| EndBitUnion (PMSELR_t) BitUnion32(PMEVTYPER_t) Bitfield< 15 | |

| EndBitUnion (PMEVTYPER_t) typedef unsigned int CounterId | |

| Counter ID within the PMU. | |

| RegVal | readMiscRegInt (int misc_reg) |

| void | setControlReg (PMCR_t val) |

| PMCR write handling. | |

| void | resetEventCounts () |

| Reset all event counters excluding the cycle counter to zero. | |

| void | raiseInterrupt () |

| Deliver a PMU interrupt to the GIC. | |

| void | clearInterrupt () |

| Clear a PMU interrupt. | |

| uint64_t | getCounterValue (CounterId id) const |

| Get the value of a performance counter. | |

| void | setCounterValue (CounterId id, uint64_t val) |

| Set the value of a performance counter. | |

| PMEVTYPER_t | getCounterTypeRegister (CounterId id) const |

| Get the type and filter settings of a counter (PMEVTYPER) | |

| void | setCounterTypeRegister (CounterId id, PMEVTYPER_t type) |

| Set the type and filter settings of a performance counter (PMEVTYPER) | |

| void | setOverflowStatus (RegVal new_val) |

| Used for writing the Overflow Flag Status Register (SET/CLR) | |

| std::shared_ptr< PMUEvent > | getEvent (EventTypeId eventId) |

| Obtain the event of a given id. | |

| bool | isValidCounter (CounterId id) const |

| Is this a valid counter ID? | |

| CounterState & | getCounter (CounterId id) |

| Return the state of a counter. | |

| const CounterState & | getCounter (CounterId id) const |

| Return the state of a counter. | |

| void | updateCounter (CounterState &ctr) |

| Depending on counter configuration, add or remove the probes driving the counter. | |

| bool | isFiltered (const CounterState &ctr) const |

| Check if a counter's settings allow it to be counted. | |

| void | updateAllCounters () |

| Call updateCounter() for each counter in the PMU if the counter's state has changed. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

Protected Attributes | |

| Bitfield< 1 > | p |

| Bitfield< 2 > | c |

| Bitfield< 3 > | d |

| Bitfield< 4 > | x |

| Bitfield< 5 > | dp |

| Bitfield< 6 > | lc |

| Bitfield< 15, 11 > | n |

| Bitfield< 23, 16 > | idcode |

| Bitfield< 31, 24 > | imp |

| sel | |

| evtCount | |

| Bitfield< 26 > | m |

| Bitfield< 27 > | nsh |

| Bitfield< 28 > | nsu |

| Bitfield< 29 > | nsk |

| Bitfield< 30 > | u |

| Bitfield< 31 > | p |

| bool | use64bitCounters |

| Determine whether to use 64-bit or 32-bit counters. | |

| std::set< EventTypeId > | statCounters |

| Determine whether we merge event counting with the stats framework. | |

| RegVal | reg_pmcnten |

| Performance Monitor Count Enable Register. | |

| PMCR_t | reg_pmcr |

| Performance Monitor Control Register. | |

| PMSELR_t | reg_pmselr |

| Performance Monitor Selection Register. | |

| RegVal | reg_pminten |

| Performance Monitor Interrupt Enable Register. | |

| RegVal | reg_pmovsr |

| Performance Monitor Overflow Status Register. | |

| uint64_t | reg_pmceid0 |

| Performance counter ID register. | |

| uint64_t | reg_pmceid1 |

| unsigned | clock_remainder |

| Remainder part when the clock counter is divided by 64. | |

| uint64_t | maximumCounterCount |

| The number of regular event counters. | |

| std::vector< CounterState > | counters |

| State of all general-purpose counters supported by PMU. | |

| CounterState | cycleCounter |

| State of the cycle counter. | |

| const EventTypeId | cycleCounterEventId |

| The id of the counter hardwired to the cpu cycle counter. | |

| std::shared_ptr< SWIncrementEvent > | swIncrementEvent |

| The event that implements the software increment. | |

| PMCR_t | reg_pmcr_conf |

| Constant (configuration-dependent) part of the PMCR. | |

| ArmInterruptPin * | interrupt |

| Performance monitor interrupt number. | |

| std::map< EventTypeId, std::shared_ptr< PMUEvent > > | eventMap |

| List of event types supported by this PMU. | |

| const bool | exitOnPMUControl |

| Exit simloop on PMU reset or disable. | |

| bool | exitOnPMUInterrupt |

| Exit simloop on PMU interrupt. | |

| gem5::ArmISA::PMU::Stats | stats |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

| Protected Attributes inherited from gem5::ArmISA::BaseISADevice | |

| ISA * | isa |

Static Protected Attributes | |

| static const CounterId | PMCCNTR = 31 |

| Cycle Count Register Number. | |

| static const RegVal | reg_pmcr_wr_mask = 0x39 |

| PMCR write mask when accessed from the guest. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

Detailed Description

Model of an ARM PMU version 3.

This class implements a subset of the ARM PMU v3 specification as described in the ARMv8 reference manual. It supports most of the features of the PMU, however the following features are known to be missing:

- Event filtering (e.g., from different privilege levels).

- Access controls (the PMU currently ignores the execution level).

- The chain counter (event no. 0x1E) is unimplemented.

The PMU itself does not implement any events, in merely provides an interface for the configuration scripts to hook up probes that drive events. Configuration scripts should call addEventProbe() to configure custom events or high-level methods to configure architected events. The Python implementation of addEventProbe() automatically delays event type registration until after instantiation.

In order to support CPU switching and some combined counters (e.g., memory references synthesized from loads and stores), the PMU allows multiple probes per event type. When creating a system that switches between CPU models that share the same PMU, PMU events for all of the CPU models can be registered with the PMU.

- See also

- The ARM Architecture Refererence Manual (DDI 0487A)

Member Typedef Documentation

◆ EventTypeId

| using gem5::ArmISA::PMU::EventTypeId = std::underlying_type_t<enums::EventTypeId> |

Constructor & Destructor Documentation

◆ PMU()

| gem5::ArmISA::PMU::PMU | ( | const ArmPMUParams & | p | ) |

Definition at line 58 of file pmu.cc.

References gem5::ArmISA::BaseISADevice::BaseISADevice(), clock_remainder, cycleCounter, cycleCounterEventId, DPRINTF, exitOnPMUControl, exitOnPMUInterrupt, fatal, interrupt, maximumCounterCount, p, reg_pmceid0, reg_pmceid1, reg_pmcnten, reg_pmcr, reg_pmcr_conf, reg_pminten, reg_pmovsr, reg_pmselr, gem5::SimObject::SimObject(), statCounters, stats, swIncrementEvent, use64bitCounters, and warn_if.

Referenced by gem5::ArmISA::PMU::CounterState::CounterState(), and gem5::ArmISA::PMU::Stats::Stats().

◆ ~PMU()

Member Function Documentation

◆ addEventProbe()

| void gem5::ArmISA::PMU::addEventProbe | ( | EventTypeId | id, |

| SimObject * | obj, | ||

| const char * | name ) |

Definition at line 138 of file pmu.cc.

References DPRINTF, gem5::MipsISA::event, eventMap, fatal_if, gem5::ArmISA::id, gem5::Named::name(), registerEvent(), gem5::SimObject::SimObject(), statCounters, and stats.

◆ addSoftwareIncrementEvent()

| void gem5::ArmISA::PMU::addSoftwareIncrementEvent | ( | EventTypeId | id | ) |

Definition at line 114 of file pmu.cc.

References DPRINTF, eventMap, fatal_if, gem5::ArmISA::id, registerEvent(), statCounters, stats, and swIncrementEvent.

◆ BitUnion32()

|

protected |

References gem5::ArmISA::e.

Referenced by EndBitUnion().

◆ clearInterrupt()

|

protected |

◆ drainResume()

|

overridevirtual |

Resume execution after a successful drain.

Reimplemented from gem5::Drainable.

Definition at line 177 of file pmu.cc.

References updateAllCounters().

◆ EndBitUnion() [1/3]

|

protected |

Referenced by EndBitUnion(), and EndBitUnion().

◆ EndBitUnion() [2/3]

|

protected |

This value is typically used to index into various registers controlling interrupts and overflows. The value normally in the [0, 31] range, where 31 refers to the cycle counter.

References EndBitUnion().

◆ EndBitUnion() [3/3]

|

protected |

References BitUnion32(), and EndBitUnion().

◆ getCounter() [1/2]

|

inlineprotected |

Return the state of a counter.

- Parameters

-

id ID of counter within the PMU.

- Returns

- Reference to a CounterState instance representing the counter.

Definition at line 559 of file pmu.hh.

References counters, cycleCounter, gem5::ArmISA::id, isValidCounter(), and PMCCNTR.

Referenced by getCounterTypeRegister(), getCounterValue(), setCounterTypeRegister(), and setCounterValue().

◆ getCounter() [2/2]

|

inlineprotected |

Return the state of a counter.

- Parameters

-

id ID of counter within the PMU.

- Returns

- Reference to a CounterState instance representing the counter.

Definition at line 571 of file pmu.hh.

References counters, cycleCounter, gem5::ArmISA::id, isValidCounter(), and PMCCNTR.

◆ getCounterTypeRegister()

|

protected |

Get the type and filter settings of a counter (PMEVTYPER)

This method implements a read from a PMEVTYPER register. It returns the type value and filter settings of a general purpose performance counter or the cycle counter. Non-existing counters are treated as constant '0'.

- Returns

- Performance counter type ID.

Definition at line 670 of file pmu.cc.

References gem5::ArmISA::PMU::CounterState::eventId, gem5::ArmISA::PMU::CounterState::filter, getCounter(), isValidCounter(), and gem5::X86ISA::type.

Referenced by readMiscRegInt().

◆ getCounterValue()

|

inlineprotected |

Get the value of a performance counter.

This method returns the value of a general purpose performance counter or the fixed-function cycle counter. Non-existing counters are treated as constant '0'.

- Returns

- Value of the performance counter, 0 if the counter does not exist.

Definition at line 232 of file pmu.hh.

References getCounter(), getCounterValue(), gem5::ArmISA::PMU::CounterState::getValue(), and isValidCounter().

Referenced by getCounterValue(), and readMiscRegInt().

◆ getEvent()

|

protected |

Obtain the event of a given id.

- Parameters

-

the id of the event to obtain

- Returns

- a pointer to the event with id eventId

Definition at line 800 of file pmu.cc.

References eventMap, and warn.

Referenced by regProbeListeners().

◆ isFiltered()

|

protected |

Check if a counter's settings allow it to be counted.

- Parameters

-

ctr Counter state instance representing this counter.

- Returns

- false if the counter is active, true otherwise.

Referenced by gem5::ArmISA::PMU::CounterState::add().

◆ isValidCounter()

|

inlineprotected |

Is this a valid counter ID?

- Parameters

-

id ID of counter within the PMU.

- Returns

- true if counter is within the allowed range or the cycle counter, false otherwise.

Definition at line 548 of file pmu.hh.

References counters, and PMCCNTR.

Referenced by getCounter(), getCounter(), getCounterTypeRegister(), getCounterValue(), setCounterTypeRegister(), and setCounterValue().

◆ raiseInterrupt()

|

protected |

Deliver a PMU interrupt to the GIC.

Definition at line 722 of file pmu.cc.

References DPRINTF, exitOnPMUInterrupt, gem5::exitSimLoop(), inform, interrupt, and warn_once.

Referenced by setOverflowStatus().

◆ readMiscReg()

|

overridevirtual |

Read a register within the PMU.

- Parameters

-

misc_reg Register number (see regs/misc.hh)

- Returns

- Register value.

Implements gem5::ArmISA::BaseISADevice.

Definition at line 323 of file pmu.cc.

References DPRINTF, gem5::ArmISA::miscRegName, readMiscRegInt(), gem5::ArmISA::unflattenMiscReg(), and gem5::X86ISA::val.

◆ readMiscRegInt()

|

protected |

Definition at line 332 of file pmu.cc.

References cycleCounter, getCounterTypeRegister(), getCounterValue(), gem5::ArmISA::MISCREG_PMCCFILTR, gem5::ArmISA::MISCREG_PMCCFILTR_EL0, gem5::ArmISA::MISCREG_PMCCNTR, gem5::ArmISA::MISCREG_PMCCNTR_EL0, gem5::ArmISA::MISCREG_PMCEID0, gem5::ArmISA::MISCREG_PMCEID0_EL0, gem5::ArmISA::MISCREG_PMCEID1, gem5::ArmISA::MISCREG_PMCEID1_EL0, gem5::ArmISA::MISCREG_PMCNTENCLR, gem5::ArmISA::MISCREG_PMCNTENCLR_EL0, gem5::ArmISA::MISCREG_PMCNTENSET, gem5::ArmISA::MISCREG_PMCNTENSET_EL0, gem5::ArmISA::MISCREG_PMCR, gem5::ArmISA::MISCREG_PMCR_EL0, gem5::ArmISA::MISCREG_PMEVCNTR0, gem5::ArmISA::MISCREG_PMEVCNTR0_EL0, gem5::ArmISA::MISCREG_PMEVTYPER0, gem5::ArmISA::MISCREG_PMEVTYPER0_EL0, gem5::ArmISA::MISCREG_PMINTENCLR, gem5::ArmISA::MISCREG_PMINTENCLR_EL1, gem5::ArmISA::MISCREG_PMINTENSET, gem5::ArmISA::MISCREG_PMINTENSET_EL1, gem5::ArmISA::MISCREG_PMOVSCLR_EL0, gem5::ArmISA::MISCREG_PMOVSR, gem5::ArmISA::MISCREG_PMOVSSET, gem5::ArmISA::MISCREG_PMOVSSET_EL0, gem5::ArmISA::MISCREG_PMSELR, gem5::ArmISA::MISCREG_PMSELR_EL0, gem5::ArmISA::MISCREG_PMSWINC, gem5::ArmISA::MISCREG_PMSWINC_EL0, gem5::ArmISA::MISCREG_PMUSERENR, gem5::ArmISA::MISCREG_PMUSERENR_EL0, gem5::ArmISA::MISCREG_PMXEVCNTR, gem5::ArmISA::MISCREG_PMXEVCNTR_EL0, gem5::ArmISA::MISCREG_PMXEVTYPER, gem5::ArmISA::MISCREG_PMXEVTYPER_EL0, gem5::ArmISA::MISCREG_PMXEVTYPER_PMCCFILTR, gem5::ArmISA::miscRegName, panic, PMCCNTR, reg_pmceid0, reg_pmceid1, reg_pmcnten, reg_pmcr, reg_pmcr_conf, reg_pmcr_wr_mask, reg_pminten, reg_pmovsr, reg_pmselr, gem5::ArmISA::unflattenMiscReg(), and warn.

Referenced by readMiscReg().

◆ registerEvent()

| void gem5::ArmISA::PMU::registerEvent | ( | EventTypeId | id | ) |

Definition at line 161 of file pmu.cc.

References reg_pmceid0, and reg_pmceid1.

Referenced by addEventProbe(), and addSoftwareIncrementEvent().

◆ regProbeListeners()

|

overridevirtual |

Register probe listeners for this object.

No probe listeners by default, so do nothing in base.

Reimplemented from gem5::SimObject.

Definition at line 184 of file pmu.cc.

References counters, cycleCounter, cycleCounterEventId, gem5::MipsISA::event, getEvent(), gem5::MipsISA::index, maximumCounterCount, panic_if, statCounters, and use64bitCounters.

◆ resetEventCounts()

|

protected |

Reset all event counters excluding the cycle counter to zero.

Definition at line 650 of file pmu.cc.

References counters.

Referenced by setControlReg().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 750 of file pmu.cc.

References clock_remainder, counters, gem5::csprintf(), cycleCounter, DPRINTF, gem5::ArmISA::i, reg_pmceid0, reg_pmceid1, reg_pmcnten, reg_pmcr, reg_pminten, reg_pmovsr, reg_pmselr, SERIALIZE_SCALAR, gem5::Serializable::serializeSection(), and use64bitCounters.

◆ setControlReg()

|

protected |

PMCR write handling.

The PMCR register needs special handling since writing to it changes PMU-global state (e.g., resets all counters).

- Parameters

-

val New PMCR value

Definition at line 421 of file pmu.cc.

References clock_remainder, cycleCounter, DPRINTF, exitOnPMUControl, gem5::exitSimLoop(), inform, reg_pmcr, reg_pmcr_wr_mask, resetEventCounts(), updateAllCounters(), and gem5::X86ISA::val.

Referenced by setMiscReg().

◆ setCounterTypeRegister()

|

protected |

Set the type and filter settings of a performance counter (PMEVTYPER)

This method implements a write to a PMEVTYPER register. It sets the type value and filter settings of a general purpose performance counter or the cycle counter. Writes to non-existing counters are ignored. The method automatically updates the probes used by the counter if it is enabled.

Definition at line 684 of file pmu.cc.

References DPRINTF, gem5::ArmISA::PMU::CounterState::eventId, gem5::ArmISA::PMU::CounterState::filter, getCounter(), isValidCounter(), PMCCNTR, updateCounter(), gem5::X86ISA::val, and warn_once.

Referenced by setMiscReg().

◆ setCounterValue()

|

protected |

Set the value of a performance counter.

This method sets the value of a general purpose performance counter or the fixed-function cycle counter. Writes to non-existing counters are ignored.

Definition at line 657 of file pmu.cc.

References getCounter(), isValidCounter(), gem5::ArmISA::PMU::CounterState::setValue(), gem5::X86ISA::val, and warn_once.

Referenced by setMiscReg().

◆ setMiscReg()

|

overridevirtual |

Set a register within the PMU.

Implements gem5::ArmISA::BaseISADevice.

Definition at line 208 of file pmu.cc.

References cycleCounter, DPRINTF, gem5::ArmISA::MISCREG_PMCCFILTR, gem5::ArmISA::MISCREG_PMCCFILTR_EL0, gem5::ArmISA::MISCREG_PMCCNTR, gem5::ArmISA::MISCREG_PMCCNTR_EL0, gem5::ArmISA::MISCREG_PMCEID0, gem5::ArmISA::MISCREG_PMCEID0_EL0, gem5::ArmISA::MISCREG_PMCEID1, gem5::ArmISA::MISCREG_PMCEID1_EL0, gem5::ArmISA::MISCREG_PMCNTENCLR, gem5::ArmISA::MISCREG_PMCNTENCLR_EL0, gem5::ArmISA::MISCREG_PMCNTENSET, gem5::ArmISA::MISCREG_PMCNTENSET_EL0, gem5::ArmISA::MISCREG_PMCR, gem5::ArmISA::MISCREG_PMCR_EL0, gem5::ArmISA::MISCREG_PMEVCNTR0, gem5::ArmISA::MISCREG_PMEVCNTR0_EL0, gem5::ArmISA::MISCREG_PMEVTYPER0, gem5::ArmISA::MISCREG_PMEVTYPER0_EL0, gem5::ArmISA::MISCREG_PMINTENCLR, gem5::ArmISA::MISCREG_PMINTENCLR_EL1, gem5::ArmISA::MISCREG_PMINTENSET, gem5::ArmISA::MISCREG_PMINTENSET_EL1, gem5::ArmISA::MISCREG_PMOVSCLR_EL0, gem5::ArmISA::MISCREG_PMOVSR, gem5::ArmISA::MISCREG_PMOVSSET, gem5::ArmISA::MISCREG_PMOVSSET_EL0, gem5::ArmISA::MISCREG_PMSELR, gem5::ArmISA::MISCREG_PMSELR_EL0, gem5::ArmISA::MISCREG_PMSWINC, gem5::ArmISA::MISCREG_PMSWINC_EL0, gem5::ArmISA::MISCREG_PMUSERENR, gem5::ArmISA::MISCREG_PMUSERENR_EL0, gem5::ArmISA::MISCREG_PMXEVCNTR, gem5::ArmISA::MISCREG_PMXEVCNTR_EL0, gem5::ArmISA::MISCREG_PMXEVTYPER, gem5::ArmISA::MISCREG_PMXEVTYPER_EL0, gem5::ArmISA::MISCREG_PMXEVTYPER_PMCCFILTR, gem5::ArmISA::miscRegName, panic, PMCCNTR, reg_pmcnten, reg_pminten, reg_pmovsr, reg_pmselr, setControlReg(), setCounterTypeRegister(), setCounterValue(), setOverflowStatus(), swIncrementEvent, gem5::ArmISA::unflattenMiscReg(), updateAllCounters(), gem5::X86ISA::val, and warn.

◆ setOverflowStatus()

|

protected |

Used for writing the Overflow Flag Status Register (SET/CLR)

This method implements a write to the PMOVSSET/PMOVSCLR registers. It is capturing change of state in the register bits so that the overflow interrupt can be raised/cleared as a side effect of the write.

- Parameters

-

new_val New value of the Overflow Status Register

Definition at line 708 of file pmu.cc.

References clearInterrupt(), raiseInterrupt(), reg_pminten, and reg_pmovsr.

Referenced by setMiscReg().

◆ setThreadContext()

|

overridevirtual |

Reimplemented from gem5::ArmISA::BaseISADevice.

Definition at line 104 of file pmu.cc.

References gem5::ThreadContext::contextId(), DPRINTF, interrupt, and gem5::SimObject::params().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 771 of file pmu.cc.

References clock_remainder, counters, gem5::csprintf(), cycleCounter, DPRINTF, gem5::ArmISA::i, gem5::paramIn(), reg_pmceid0, reg_pmceid1, reg_pmcnten, reg_pmcr, reg_pminten, reg_pmovsr, reg_pmselr, UNSERIALIZE_OPT_SCALAR, UNSERIALIZE_SCALAR, gem5::Serializable::unserializeSection(), and use64bitCounters.

◆ updateAllCounters()

|

protected |

Call updateCounter() for each counter in the PMU if the counter's state has changed.

- See also

- updateCounter()

Definition at line 459 of file pmu.cc.

References counters, cycleCounter, gem5::X86ISA::enable, gem5::ArmISA::PMU::CounterState::enabled, gem5::ArmISA::i, PMCCNTR, reg_pmcnten, reg_pmcr, and updateCounter().

Referenced by drainResume(), setControlReg(), and setMiscReg().

◆ updateCounter()

|

protected |

Depending on counter configuration, add or remove the probes driving the counter.

Look at the state of a counter and (re-)attach the probes needed to drive a counter if it is currently active. All probes for the counter are detached if the counter is inactive.

- Parameters

-

id ID of counter within the PMU. ctr Reference to the counter's state

Definition at line 626 of file pmu.cc.

References gem5::ArmISA::PMU::CounterState::attach(), gem5::ArmISA::PMU::CounterState::detach(), DPRINTF, gem5::ArmISA::PMU::CounterState::enabled, gem5::ArmISA::PMU::CounterState::eventId, eventMap, gem5::ArmISA::PMU::CounterState::getCounterId(), and warn.

Referenced by setCounterTypeRegister(), and updateAllCounters().

Member Data Documentation

◆ c

◆ clock_remainder

|

protected |

Remainder part when the clock counter is divided by 64.

Definition at line 640 of file pmu.hh.

Referenced by PMU(), serialize(), setControlReg(), and unserialize().

◆ counters

|

protected |

State of all general-purpose counters supported by PMU.

Definition at line 646 of file pmu.hh.

Referenced by getCounter(), getCounter(), isValidCounter(), regProbeListeners(), resetEventCounts(), serialize(), unserialize(), and updateAllCounters().

◆ cycleCounter

|

protected |

State of the cycle counter.

Definition at line 649 of file pmu.hh.

Referenced by getCounter(), getCounter(), PMU(), readMiscRegInt(), regProbeListeners(), serialize(), setControlReg(), setMiscReg(), unserialize(), and updateAllCounters().

◆ cycleCounterEventId

|

protected |

The id of the counter hardwired to the cpu cycle counter.

Definition at line 652 of file pmu.hh.

Referenced by PMU(), and regProbeListeners().

◆ d

◆ dp

◆ eventMap

|

protected |

List of event types supported by this PMU.

Definition at line 670 of file pmu.hh.

Referenced by addEventProbe(), addSoftwareIncrementEvent(), getEvent(), and updateCounter().

◆ evtCount

◆ exitOnPMUControl

|

protected |

Exit simloop on PMU reset or disable.

Definition at line 675 of file pmu.hh.

Referenced by PMU(), and setControlReg().

◆ exitOnPMUInterrupt

|

protected |

Exit simloop on PMU interrupt.

Definition at line 680 of file pmu.hh.

Referenced by PMU(), and raiseInterrupt().

◆ idcode

◆ imp

◆ interrupt

|

protected |

Performance monitor interrupt number.

Definition at line 665 of file pmu.hh.

Referenced by clearInterrupt(), PMU(), raiseInterrupt(), and setThreadContext().

◆ lc

◆ m

◆ maximumCounterCount

|

protected |

The number of regular event counters.

Definition at line 643 of file pmu.hh.

Referenced by PMU(), and regProbeListeners().

◆ n

◆ nsh

◆ nsk

◆ nsu

◆ p [1/2]

|

protected |

◆ p [2/2]

◆ PMCCNTR

|

staticprotected |

Cycle Count Register Number.

Definition at line 192 of file pmu.hh.

Referenced by getCounter(), getCounter(), isValidCounter(), readMiscRegInt(), setCounterTypeRegister(), setMiscReg(), and updateAllCounters().

◆ reg_pmceid0

|

protected |

Performance counter ID register.

These registers contain a bitmask of available architected counters.

Definition at line 636 of file pmu.hh.

Referenced by PMU(), readMiscRegInt(), registerEvent(), serialize(), and unserialize().

◆ reg_pmceid1

|

protected |

Definition at line 637 of file pmu.hh.

Referenced by PMU(), readMiscRegInt(), registerEvent(), serialize(), and unserialize().

◆ reg_pmcnten

|

protected |

Performance Monitor Count Enable Register.

Definition at line 616 of file pmu.hh.

Referenced by PMU(), readMiscRegInt(), serialize(), setMiscReg(), unserialize(), and updateAllCounters().

◆ reg_pmcr

|

protected |

Performance Monitor Control Register.

Definition at line 619 of file pmu.hh.

Referenced by PMU(), readMiscRegInt(), serialize(), setControlReg(), unserialize(), and updateAllCounters().

◆ reg_pmcr_conf

|

protected |

Constant (configuration-dependent) part of the PMCR.

Definition at line 659 of file pmu.hh.

Referenced by PMU(), and readMiscRegInt().

◆ reg_pmcr_wr_mask

|

staticprotected |

PMCR write mask when accessed from the guest.

Definition at line 662 of file pmu.hh.

Referenced by readMiscRegInt(), and setControlReg().

◆ reg_pminten

|

protected |

Performance Monitor Interrupt Enable Register.

Definition at line 625 of file pmu.hh.

Referenced by PMU(), readMiscRegInt(), serialize(), setMiscReg(), setOverflowStatus(), and unserialize().

◆ reg_pmovsr

|

protected |

Performance Monitor Overflow Status Register.

Definition at line 628 of file pmu.hh.

Referenced by PMU(), readMiscRegInt(), serialize(), setMiscReg(), setOverflowStatus(), and unserialize().

◆ reg_pmselr

|

protected |

Performance Monitor Selection Register.

Definition at line 622 of file pmu.hh.

Referenced by PMU(), readMiscRegInt(), serialize(), setMiscReg(), and unserialize().

◆ sel

◆ statCounters

|

protected |

Determine whether we merge event counting with the stats framework.

Definition at line 613 of file pmu.hh.

Referenced by addEventProbe(), addSoftwareIncrementEvent(), PMU(), and regProbeListeners().

◆ stats

|

protected |

Referenced by addEventProbe(), addSoftwareIncrementEvent(), and PMU().

◆ swIncrementEvent

|

protected |

The event that implements the software increment.

Definition at line 655 of file pmu.hh.

Referenced by addSoftwareIncrementEvent(), PMU(), and setMiscReg().

◆ u

◆ use64bitCounters

|

protected |

Determine whether to use 64-bit or 32-bit counters.

Definition at line 607 of file pmu.hh.

Referenced by PMU(), regProbeListeners(), serialize(), and unserialize().

◆ x

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:56 for gem5 by doxygen 1.14.0