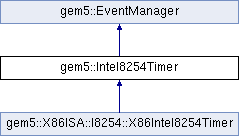

Programmable Interval Timer (Intel 8254) More...

#include <intel_8254_timer.hh>

Classes | |

| class | Counter |

| Counter element for PIT. More... | |

Public Member Functions | |

| virtual | ~Intel8254Timer () |

| Intel8254Timer (EventManager *em, const std::string &name) | |

| void | writeControl (const CtrlReg data) |

| Write control word. | |

| uint8_t | readCounter (unsigned int num) |

| void | writeCounter (unsigned int num, const uint8_t data) |

| bool | outputHigh (unsigned int num) |

| void | serialize (const std::string &base, CheckpointOut &cp) const |

| Serialize this object to the given output stream. | |

| void | unserialize (const std::string &base, CheckpointIn &cp) |

| Reconstruct the state of this object from a checkpoint. | |

| void | startup () |

| Start ticking. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

Protected Types | |

| enum | ReadWriteVal { LatchCommand , LsbOnly , MsbOnly , TwoPhase } |

| enum | ModeVal { InitTc , OneShot , RateGen , SquareWave , SoftwareStrobe , HardwareStrobe } |

Protected Member Functions | |

| BitUnion8 (CtrlReg) Bitfield< 7 | |

| EndBitUnion (CtrlReg) BitUnion8(ReadBackCommandVal) Bitfield< 4 > status | |

| SubBitUnion (select, 3, 1) Bitfield< 3 > cnt2 | |

| EndSubBitUnion (select) EndBitUnion(ReadBackCommandVal) enum SelectVal | |

| const std::string & | name () const |

| virtual void | counterInterrupt (unsigned int num) |

Protected Attributes | |

| sel | |

| Bitfield< 5, 4 > | rw |

| Bitfield< 3, 1 > | mode |

| Bitfield< 0 > | bcd |

| Bitfield< 5 > | count |

| Bitfield< 2 > | cnt1 |

| Bitfield< 1 > | cnt0 |

| std::string | _name |

| std::array< Counter, 3 > | counters |

| PIT has three seperate counters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Detailed Description

Programmable Interval Timer (Intel 8254)

Definition at line 47 of file intel_8254_timer.hh.

Member Enumeration Documentation

◆ ModeVal

|

protected |

| Enumerator | |

|---|---|

| InitTc | |

| OneShot | |

| RateGen | |

| SquareWave | |

| SoftwareStrobe | |

| HardwareStrobe | |

Definition at line 83 of file intel_8254_timer.hh.

◆ ReadWriteVal

|

protected |

| Enumerator | |

|---|---|

| LatchCommand | |

| LsbOnly | |

| MsbOnly | |

| TwoPhase | |

Definition at line 75 of file intel_8254_timer.hh.

Constructor & Destructor Documentation

◆ ~Intel8254Timer()

|

inlinevirtual |

Definition at line 227 of file intel_8254_timer.hh.

◆ Intel8254Timer()

| gem5::Intel8254Timer::Intel8254Timer | ( | EventManager * | em, |

| const std::string & | name ) |

Definition at line 39 of file intel_8254_timer.cc.

References _name, counters, gem5::X86ISA::em, gem5::EventManager::EventManager(), and name().

Referenced by gem5::Intel8254Timer::Counter::Counter(), counterInterrupt(), gem5::Intel8254Timer::Counter::CounterEvent::setTo(), and gem5::X86ISA::I8254::X86Intel8254Timer::X86Intel8254Timer().

Member Function Documentation

◆ BitUnion8()

|

protected |

Referenced by EndBitUnion().

◆ counterInterrupt()

|

inlineprotectedvirtual |

Reimplemented in gem5::X86ISA::I8254::X86Intel8254Timer.

Definition at line 219 of file intel_8254_timer.hh.

References DPRINTF, and Intel8254Timer().

◆ EndBitUnion()

|

protected |

References BitUnion8(), EndBitUnion(), and gem5::ArmISA::status.

Referenced by EndBitUnion(), and EndSubBitUnion().

◆ EndSubBitUnion()

|

inlineprotected |

Definition at line 64 of file intel_8254_timer.hh.

References EndBitUnion(), and EndSubBitUnion().

Referenced by EndSubBitUnion().

◆ name()

|

inlineprotected |

Definition at line 213 of file intel_8254_timer.hh.

References _name.

Referenced by Intel8254Timer(), and gem5::X86ISA::I8254::X86Intel8254Timer::X86Intel8254Timer().

◆ outputHigh()

|

inline |

Definition at line 250 of file intel_8254_timer.hh.

References counters.

◆ readCounter()

|

inline |

Definition at line 236 of file intel_8254_timer.hh.

References counters.

◆ serialize()

| void gem5::Intel8254Timer::serialize | ( | const std::string & | base, |

| CheckpointOut & | cp ) const |

Serialize this object to the given output stream.

- Parameters

-

base The base name of the counter object. os The stream to serialize to.

Definition at line 77 of file intel_8254_timer.cc.

References gem5::RiscvISA::base, counters, and serialize().

Referenced by serialize().

◆ startup()

| void gem5::Intel8254Timer::startup | ( | ) |

Start ticking.

Definition at line 95 of file intel_8254_timer.cc.

References counters, and startup().

Referenced by startup().

◆ SubBitUnion()

|

protected |

References SubBitUnion().

Referenced by SubBitUnion().

◆ unserialize()

| void gem5::Intel8254Timer::unserialize | ( | const std::string & | base, |

| CheckpointIn & | cp ) |

Reconstruct the state of this object from a checkpoint.

- Parameters

-

base The base name of the counter object. cp The checkpoint use. section The section name of this object

Definition at line 86 of file intel_8254_timer.cc.

References gem5::RiscvISA::base, counters, and unserialize().

Referenced by unserialize().

◆ writeControl()

| void gem5::Intel8254Timer::writeControl | ( | const CtrlReg | data | ) |

Write control word.

Definition at line 48 of file intel_8254_timer.cc.

References gem5::bits(), counters, data, LatchCommand, panic_if, sel, and writeControl().

Referenced by writeControl().

◆ writeCounter()

|

inline |

Definition at line 243 of file intel_8254_timer.hh.

Member Data Documentation

◆ _name

|

protected |

Definition at line 212 of file intel_8254_timer.hh.

Referenced by Intel8254Timer(), and name().

◆ bcd

|

protected |

Definition at line 54 of file intel_8254_timer.hh.

◆ cnt0

|

protected |

Definition at line 63 of file intel_8254_timer.hh.

◆ cnt1

|

protected |

Definition at line 62 of file intel_8254_timer.hh.

◆ count

|

protected |

Definition at line 59 of file intel_8254_timer.hh.

Referenced by gem5::Intel8254Timer::Counter::read().

◆ counters

|

protected |

PIT has three seperate counters.

Definition at line 216 of file intel_8254_timer.hh.

Referenced by Intel8254Timer(), outputHigh(), readCounter(), serialize(), startup(), unserialize(), writeControl(), and writeCounter().

◆ mode

|

protected |

Definition at line 53 of file intel_8254_timer.hh.

◆ rw

|

protected |

Definition at line 52 of file intel_8254_timer.hh.

◆ sel

|

protected |

Definition at line 51 of file intel_8254_timer.hh.

Referenced by writeControl().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:52 for gem5 by doxygen 1.14.0