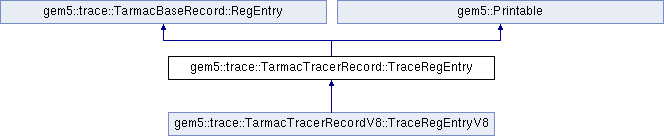

Register Entry. More...

#include <tarmac_record.hh>

Public Member Functions | |

| TraceRegEntry (const TarmacContext &tarmCtx, const RegId ®) | |

| void | update (const TarmacContext &tarmCtx) |

| This updates the register entry using the update table. | |

| virtual void | print (std::ostream &outs, int verbosity=0, const std::string &prefix="") const override |

| Public Member Functions inherited from gem5::trace::TarmacBaseRecord::RegEntry | |

| RegEntry ()=default | |

| RegEntry (const PCStateBase &pc) | |

| Public Member Functions inherited from gem5::Printable | |

| Printable () | |

| virtual | ~Printable () |

Public Attributes | |

| bool | regValid |

| True if register entry is valid. | |

| RegId | regId |

| Register ID. | |

| std::string | regName |

| Register name to be printed. | |

| Public Attributes inherited from gem5::trace::TarmacBaseRecord::RegEntry | |

| RegType | type |

| RegIndex | index |

| ISetState | isetstate |

| std::vector< uint64_t > | values |

Protected Member Functions | |

| virtual void | updateMisc (const TarmacContext &tarmCtx) |

| Register update functions. | |

| virtual void | updateCC (const TarmacContext &tarmCtx) |

| virtual void | updateFloat (const TarmacContext &tarmCtx) |

| virtual void | updateInt (const TarmacContext &tarmCtx) |

| virtual void | updateVec (const TarmacContext &tarmCtx) |

| virtual void | updatePred (const TarmacContext &tarmCtx) |

Additional Inherited Members | |

| Public Types inherited from gem5::trace::TarmacBaseRecord::RegEntry | |

| enum | RegElement { Lo = 0 , Hi = 1 , Max = 32 } |

Detailed Description

Register Entry.

Definition at line 124 of file tarmac_record.hh.

Constructor & Destructor Documentation

◆ TraceRegEntry()

| gem5::trace::TarmacTracerRecord::TraceRegEntry::TraceRegEntry | ( | const TarmacContext & | tarmCtx, |

| const RegId & | reg ) |

Definition at line 162 of file tarmac_record.cc.

References gem5::trace::InstRecord::pc, gem5::X86ISA::reg, gem5::trace::TarmacBaseRecord::RegEntry::RegEntry(), regId, and regValid.

Referenced by gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::TraceRegEntryV8().

Member Function Documentation

◆ print()

|

overridevirtual |

Implements gem5::Printable.

Reimplemented in gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8.

Definition at line 442 of file tarmac_record.cc.

References gem5::ccprintf(), gem5::curTick(), gem5::trace::TarmacBaseRecord::RegEntry::Lo, regName, regValid, and gem5::trace::TarmacBaseRecord::RegEntry::values.

◆ update()

| void gem5::trace::TarmacTracerRecord::TraceRegEntry::update | ( | const TarmacContext & | tarmCtx | ) |

This updates the register entry using the update table.

It is a required step after the register entry generation. If unupdated, the entry will be marked as invalid. The entry update cannot be done automatically at TraceRegEntry construction: the entries are extended by consequent Tarmac Tracer versions (like V8), and virtual functions should be avoided during construction.

Definition at line 172 of file tarmac_record.cc.

References gem5::CCRegClass, gem5::FloatRegClass, gem5::IntRegClass, gem5::MiscRegClass, regId, updateCC(), updateFloat(), updateInt(), updateMisc(), updatePred(), updateVec(), gem5::VecPredRegClass, and gem5::VecRegClass.

◆ updateCC()

|

protectedvirtual |

Definition at line 227 of file tarmac_record.cc.

References gem5::trace::TarmacBaseRecord::RegEntry::Lo, regId, gem5::ArmISA::cc_reg::RegName, regName, regValid, gem5::trace::InstRecord::thread, gem5::trace::TarmacContext::thread, and gem5::trace::TarmacBaseRecord::RegEntry::values.

Referenced by update().

◆ updateFloat()

|

protectedvirtual |

◆ updateInt()

|

protectedvirtual |

Reimplemented in gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8.

Definition at line 245 of file tarmac_record.cc.

References gem5::ArmISA::FramePointerReg, gem5::trace::TarmacBaseRecord::RegEntry::Lo, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::mode, gem5::ArmISA::MODE_USER, gem5::trace::opModeToStr(), gem5::ArmISA::int_reg::Pc, regId, regName, regValid, gem5::ArmISA::ReturnAddressReg, gem5::ArmISA::StackPointerReg, gem5::trace::InstRecord::thread, gem5::trace::TarmacContext::thread, and gem5::trace::TarmacBaseRecord::RegEntry::values.

Referenced by update().

◆ updateMisc()

|

protectedvirtual |

Register update functions.

Reimplemented in gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8.

Definition at line 203 of file tarmac_record.cc.

References gem5::ArmISA::cc_reg::C, gem5::ArmISA::cc_reg::Ge, gem5::trace::TarmacBaseRecord::RegEntry::Lo, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::miscRegName, gem5::ArmISA::cc_reg::Nz, regId, regName, regValid, gem5::trace::InstRecord::thread, gem5::trace::TarmacContext::thread, gem5::ArmISA::cc_reg::V, and gem5::trace::TarmacBaseRecord::RegEntry::values.

Referenced by update().

◆ updatePred()

|

inlineprotectedvirtual |

Reimplemented in gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8.

Definition at line 151 of file tarmac_record.hh.

Referenced by update().

◆ updateVec()

|

inlineprotectedvirtual |

Reimplemented in gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8.

Definition at line 150 of file tarmac_record.hh.

Referenced by update().

Member Data Documentation

◆ regId

| RegId gem5::trace::TarmacTracerRecord::TraceRegEntry::regId |

Register ID.

Definition at line 157 of file tarmac_record.hh.

Referenced by TraceRegEntry(), update(), updateCC(), updateFloat(), updateInt(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updateInt(), updateMisc(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updatePred(), and gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updateVec().

◆ regName

| std::string gem5::trace::TarmacTracerRecord::TraceRegEntry::regName |

Register name to be printed.

Definition at line 159 of file tarmac_record.hh.

Referenced by print(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::print(), updateCC(), updateFloat(), updateInt(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updateInt(), updateMisc(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updatePred(), and gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updateVec().

◆ regValid

| bool gem5::trace::TarmacTracerRecord::TraceRegEntry::regValid |

True if register entry is valid.

Definition at line 155 of file tarmac_record.hh.

Referenced by print(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::print(), TraceRegEntry(), updateCC(), updateFloat(), updateInt(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updateInt(), updateMisc(), gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updatePred(), and gem5::trace::TarmacTracerRecordV8::TraceRegEntryV8::updateVec().

The documentation for this struct was generated from the following files:

- arch/arm/tracers/tarmac_record.hh

- arch/arm/tracers/tarmac_record.cc

Generated on Sat Oct 18 2025 08:07:04 for gem5 by doxygen 1.14.0