#include <pcstate.hh>

Public Member Functions | |

| virtual | ~PCStateBase ()=default |

| template<class Target> | |

| Target & | as () |

| template<class Target> | |

| const Target & | as () const |

| virtual PCStateBase * | clone () const =0 |

| virtual void | update (const PCStateBase &other) |

| void | update (const PCStateBase *ptr) |

| virtual void | output (std::ostream &os) const =0 |

| virtual bool | equals (const PCStateBase &other) const |

| Addr | instAddr () const |

| Returns the memory address of the instruction this PC points to. | |

| MicroPC | microPC () const |

| Returns the current micropc. | |

| virtual void | uReset () |

| virtual void | set (Addr val) |

| virtual void | advance ()=0 |

| virtual bool | branching () const =0 |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Protected Member Functions | |

| PCStateBase (const PCStateBase &other) | |

| PCStateBase & | operator= (const PCStateBase &other)=default |

| PCStateBase () | |

Protected Attributes | |

| Addr | _pc = 0 |

| MicroPC | _upc = 0 |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

Detailed Description

Definition at line 58 of file pcstate.hh.

Constructor & Destructor Documentation

◆ PCStateBase() [1/2]

|

inlineprotected |

Definition at line 64 of file pcstate.hh.

References _pc, _upc, and PCStateBase().

Referenced by clone(), gem5::PowerISA::PCState::clone(), gem5::GenericISA::DelaySlotPCState< 4 >::equals(), gem5::GenericISA::PCStateWithNext::equals(), equals(), operator=(), PCStateBase(), gem5::GenericISA::PCStateWithNext::PCStateWithNext(), gem5::GenericISA::DelaySlotPCState< 4 >::update(), gem5::GenericISA::PCStateWithNext::update(), update(), update(), and gem5::PowerISA::PCState::update().

◆ PCStateBase() [2/2]

|

inlineprotected |

Definition at line 66 of file pcstate.hh.

◆ ~PCStateBase()

|

virtualdefault |

Member Function Documentation

◆ advance()

|

pure virtual |

◆ as() [1/2]

|

inline |

Definition at line 73 of file pcstate.hh.

Referenced by gem5::ArmISA::ArmStaticInst::advancePC(), gem5::ArmISA::ArmStaticInst::advancePC(), gem5::ArmISA::FpOp::advancePC(), gem5::ArmISA::FpOp::advancePC(), gem5::ArmISA::MicroOp::advancePC(), gem5::ArmISA::MicroOp::advancePC(), gem5::ArmISA::MicroOpX::advancePC(), gem5::ArmISA::MicroOpX::advancePC(), gem5::ArmISA::MightBeMicro64::advancePC(), gem5::ArmISA::MightBeMicro64::advancePC(), gem5::ArmISA::MightBeMicro::advancePC(), gem5::ArmISA::MightBeMicro::advancePC(), gem5::ArmISA::PredMicroop::advancePC(), gem5::ArmISA::PredMicroop::advancePC(), gem5::PowerISA::PowerStaticInst::advancePC(), gem5::PowerISA::PowerStaticInst::advancePC(), gem5::RiscvISA::RiscvMicroInst::advancePC(), gem5::RiscvISA::RiscvMicroInst::advancePC(), gem5::RiscvISA::RiscvStaticInst::advancePC(), gem5::SparcISA::SparcMicroInst::advancePC(), gem5::SparcISA::SparcMicroInst::advancePC(), gem5::SparcISA::SparcStaticInst::advancePC(), gem5::SparcISA::SparcStaticInst::advancePC(), gem5::X86ISA::X86MicroopBase::advancePC(), gem5::X86ISA::X86MicroopBase::advancePC(), gem5::X86ISA::X86StaticInst::advancePC(), gem5::X86ISA::X86StaticInst::advancePC(), gem5::ArmISA::SoftwareStep::advanceSS(), gem5::PowerProcess::argsInit(), gem5::ArmISA::BranchImm64::branchTarget(), gem5::ArmISA::BranchImmImmReg64::branchTarget(), gem5::ArmISA::BranchImmReg64::branchTarget(), gem5::RiscvISA::VlFFTrimVlMicroOp::branchTarget(), gem5::RiscvISA::ZcmtSecondFetchInst::branchTarget(), gem5::X86ISA::X86MicroopBase::branchTarget(), gem5::ArmISA::ArmStaticInst::buildRetPC(), gem5::PowerISA::PowerStaticInst::buildRetPC(), gem5::RiscvISA::RiscvStaticInst::buildRetPC(), gem5::SparcISA::SparcStaticInst::buildRetPC(), gem5::X86ISA::X86StaticInst::buildRetPC(), gem5::trace::ArmNativeTrace::check(), gem5::trace::SparcNativeTrace::check(), gem5::LooppointAnalysis::checkPc(), gem5::trace::ArmCapstoneDisassembler::currHandle(), gem5::ArmISA::Decoder::decode(), gem5::RiscvISA::Decoder::decode(), gem5::X86ISA::Decoder::decode(), gem5::SparcISA::doNormalFault(), gem5::SparcISA::doREDFault(), gem5::GenericISA::DelaySlotPCState< 4 >::equals(), gem5::GenericISA::PCStateWithNext::equals(), gem5::RiscvISA::PCState::equals(), gem5::DebugStep::execute(), gem5::SparcISA::SEWorkload::handleTrap(), gem5::PowerProcess::initState(), gem5::ArmISA::SupervisorCall::invoke(), gem5::RiscvISA::RiscvFault::invoke(), gem5::SparcISA::TrapInstruction::invoke(), gem5::X86ISA::X86FaultBase::invoke(), gem5::ArmISA::ArmFault::invoke64(), gem5::RiscvISA::SyscallFault::invokeSE(), gem5::ArmISA::Decoder::moreBytes(), gem5::ArmISA::ArmStaticInst::readPC(), gem5::ArmISA::SkipFunc::returnFromFuncIn(), gem5::ArmISA::HTMCheckpoint::save(), gem5::ArmISA::ArmStaticInst::setAIWNextPC(), gem5::MipsISA::MipsFaultBase::setExceptionState(), gem5::ArmISA::ArmStaticInst::setIWNextPC(), gem5::ArmISA::ArmStaticInst::setNextPC(), gem5::X86ISA::EmuLinux::syscall(), gem5::ArmISA::SelfDebug::testBreakPoints(), gem5::GenericISA::DelaySlotPCState< 4 >::update(), gem5::GenericISA::PCStateWithNext::update(), gem5::PowerISA::PCState::update(), gem5::RiscvISA::PCState::update(), gem5::trace::ArmNativeTrace::ThreadState::update(), gem5::trace::X86NativeTrace::ThreadState::update(), and gem5::X86ISA::PCState::update().

◆ as() [2/2]

|

inline |

Definition at line 80 of file pcstate.hh.

◆ branching()

|

pure virtual |

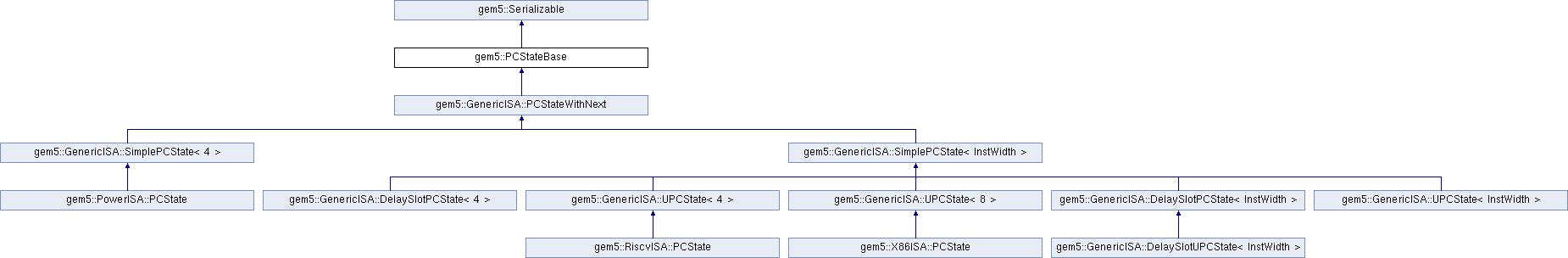

Implemented in gem5::GenericISA::DelaySlotPCState< InstWidth >, gem5::GenericISA::DelaySlotPCState< 4 >, gem5::GenericISA::DelaySlotUPCState< InstWidth >, gem5::GenericISA::DelaySlotUPCState< 4 >, gem5::GenericISA::SimplePCState< InstWidth >, gem5::GenericISA::SimplePCState< 4 >, gem5::GenericISA::UPCState< InstWidth >, gem5::GenericISA::UPCState< 4 >, gem5::GenericISA::UPCState< 8 >, gem5::RiscvISA::PCState, and gem5::X86ISA::PCState.

Referenced by gem5::BaseSimpleCPU::advancePC(), and gem5::o3::Fetch::fetch().

◆ clone()

|

pure virtual |

Implemented in gem5::GenericISA::DelaySlotPCState< InstWidth >, gem5::GenericISA::DelaySlotPCState< 4 >, gem5::GenericISA::DelaySlotUPCState< InstWidth >, gem5::GenericISA::DelaySlotUPCState< 4 >, gem5::GenericISA::SimplePCState< InstWidth >, gem5::GenericISA::SimplePCState< 4 >, gem5::GenericISA::UPCState< InstWidth >, gem5::GenericISA::UPCState< 4 >, gem5::GenericISA::UPCState< 8 >, gem5::PowerISA::PCState, gem5::RiscvISA::PCState, and gem5::X86ISA::PCState.

References PCStateBase().

Referenced by gem5::GenericISA::M5DebugFault::advancePC(), gem5::StaticInst::advancePC(), gem5::ArmISA::BranchImm64::branchTarget(), gem5::ArmISA::BranchImmImmReg64::branchTarget(), gem5::ArmISA::BranchImmReg64::branchTarget(), gem5::RiscvISA::VlFFTrimVlMicroOp::branchTarget(), gem5::X86ISA::X86MicroopBase::branchTarget(), gem5::ArmISA::ArmStaticInst::buildRetPC(), gem5::PowerISA::PowerStaticInst::buildRetPC(), gem5::RiscvISA::RiscvStaticInst::buildRetPC(), gem5::SparcISA::SparcStaticInst::buildRetPC(), gem5::X86ISA::X86StaticInst::buildRetPC(), gem5::minor::LSQ::LSQRequest::completeDisabledMemAccess(), gem5::minor::Execute::executeMemRefInst(), gem5::o3::Fetch::fetch(), gem5::SESyscallFault::invoke(), gem5::SkipFuncBase::process(), gem5::minor::Execute::tryToBranch(), gem5::minor::LSQ::tryToSendToTransfers(), gem5::minor::LSQ::LSQRequest::tryToSuppressFault(), and gem5::unserialize().

◆ equals()

|

inlinevirtual |

Reimplemented in gem5::GenericISA::DelaySlotPCState< InstWidth >, gem5::GenericISA::DelaySlotPCState< 4 >, gem5::GenericISA::PCStateWithNext, and gem5::RiscvISA::PCState.

Definition at line 97 of file pcstate.hh.

References _pc, _upc, and PCStateBase().

Referenced by gem5::GenericISA::DelaySlotPCState< 4 >::equals(), gem5::GenericISA::PCStateWithNext::equals(), and gem5::RiscvISA::PCState::equals().

◆ instAddr()

|

inline |

Returns the memory address of the instruction this PC points to.

- Returns

- Memory address of the instruction this PC points to.

Definition at line 108 of file pcstate.hh.

References _pc.

Referenced by gem5::AtOp64::addressTranslation64(), gem5::AtomicSimpleCPU::amoMem(), gem5::PowerISA::BranchDispCondOp::branchTarget(), gem5::PowerISA::BranchOp::branchTarget(), gem5::o3::Fetch::buildInst(), gem5::MipsISA::Decoder::decode(), gem5::PowerISA::Decoder::decode(), gem5::SparcISA::Decoder::decode(), gem5::o3::Fetch::doSquash(), gem5::X86ISA::EmuLinux::event(), gem5::DecoderFaultInst::execute(), gem5::o3::Fetch::fetch(), gem5::TimingSimpleCPU::htmSendAbortSignal(), gem5::TimingSimpleCPU::initiateMemAMO(), gem5::TimingSimpleCPU::initiateMemMgmtCmd(), gem5::TimingSimpleCPU::initiateMemRead(), gem5::PowerISA::TrapFault::invoke(), gem5::PowerISA::UnimplementedOpcodeFault::invoke(), gem5::X86ISA::PageFault::invoke(), gem5::ArmISA::ArmFault::invoke64(), gem5::RiscvSemihosting::isSemihostingEBreak(), gem5::mmapFunc(), gem5::BaseCPU::mwaitAtomic(), gem5::o3::Fetch::pipelineIcacheAccesses(), gem5::SimPoint::profile(), gem5::branch_prediction::SimpleIndirectPredictor::recordTarget(), gem5::BaseSimpleCPU::setupFetchRequest(), gem5::branch_prediction::BPredUnit::squash(), gem5::X86ISA::GpuTLB::translate(), gem5::X86ISA::TLB::translate(), gem5::minor::Execute::tryPCEvents(), gem5::branch_prediction::SimpleIndirectPredictor::update(), and gem5::TimingSimpleCPU::writeMem().

◆ microPC()

|

inline |

Returns the current micropc.

- Returns

- The current micropc.

Definition at line 119 of file pcstate.hh.

References _upc.

Referenced by gem5::o3::Fetch::fetch(), gem5::TimingSimpleCPU::fetch(), gem5::AtomicSimpleCPU::isCpuDrained(), gem5::TimingSimpleCPU::isCpuDrained(), gem5::o3::Fetch::pipelineIcacheAccesses(), and gem5::TimingSimpleCPU::switchOut().

◆ operator=()

|

protecteddefault |

References PCStateBase().

◆ output()

|

pure virtual |

Implemented in gem5::GenericISA::DelaySlotPCState< InstWidth >, gem5::GenericISA::DelaySlotPCState< 4 >, gem5::GenericISA::DelaySlotUPCState< InstWidth >, gem5::GenericISA::DelaySlotUPCState< 4 >, gem5::GenericISA::PCStateWithNext, gem5::GenericISA::UPCState< InstWidth >, gem5::GenericISA::UPCState< 4 >, and gem5::GenericISA::UPCState< 8 >.

References gem5::X86ISA::os.

Referenced by gem5::GenericISA::UPCState< 4 >::output().

◆ serialize()

|

inlineoverridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Reimplemented in gem5::GenericISA::PCStateWithNext.

Definition at line 141 of file pcstate.hh.

References _pc, _upc, and SERIALIZE_SCALAR.

Referenced by gem5::GenericISA::DelaySlotPCState< 4 >::serialize(), gem5::GenericISA::PCStateWithNext::serialize(), gem5::RiscvISA::PCState::serialize(), gem5::serialize(), and gem5::X86ISA::PCState::serialize().

◆ set()

|

inlinevirtual |

Reimplemented in gem5::GenericISA::DelaySlotPCState< InstWidth >, gem5::GenericISA::DelaySlotPCState< 4 >, gem5::GenericISA::DelaySlotUPCState< InstWidth >, gem5::GenericISA::DelaySlotUPCState< 4 >, gem5::GenericISA::PCStateWithNext, gem5::GenericISA::SimplePCState< InstWidth >, gem5::GenericISA::SimplePCState< 4 >, gem5::GenericISA::UPCState< InstWidth >, gem5::GenericISA::UPCState< 4 >, gem5::GenericISA::UPCState< 8 >, and gem5::X86ISA::PCState.

Definition at line 131 of file pcstate.hh.

References _pc, _upc, and gem5::X86ISA::val.

Referenced by gem5::GenericISA::PCStateWithNext::set().

◆ unserialize()

|

inlineoverridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Reimplemented in gem5::GenericISA::PCStateWithNext.

Definition at line 148 of file pcstate.hh.

References _pc, _upc, and UNSERIALIZE_SCALAR.

Referenced by gem5::GenericISA::DelaySlotPCState< 4 >::unserialize(), gem5::GenericISA::PCStateWithNext::unserialize(), gem5::RiscvISA::PCState::unserialize(), and gem5::X86ISA::PCState::unserialize().

◆ update() [1/2]

|

inlinevirtual |

Reimplemented in gem5::GenericISA::DelaySlotPCState< InstWidth >, gem5::GenericISA::DelaySlotPCState< 4 >, gem5::GenericISA::PCStateWithNext, gem5::PowerISA::PCState, gem5::RiscvISA::PCState, and gem5::X86ISA::PCState.

Definition at line 87 of file pcstate.hh.

References _pc, _upc, and PCStateBase().

Referenced by gem5::GenericISA::DelaySlotPCState< 4 >::update(), gem5::GenericISA::PCStateWithNext::update(), gem5::PowerISA::PCState::update(), gem5::RiscvISA::PCState::update(), and gem5::X86ISA::PCState::update().

◆ update() [2/2]

|

inline |

Definition at line 92 of file pcstate.hh.

References PCStateBase(), and update().

Referenced by update().

◆ uReset()

|

inlinevirtual |

Reimplemented in gem5::GenericISA::PCStateWithNext.

Definition at line 125 of file pcstate.hh.

References _upc.

Referenced by gem5::GenericISA::PCStateWithNext::uReset().

Member Data Documentation

◆ _pc

|

protected |

Definition at line 61 of file pcstate.hh.

Referenced by gem5::GenericISA::DelaySlotPCState< 4 >::advance(), gem5::GenericISA::SimplePCState< InstWidth >::advance(), equals(), instAddr(), gem5::GenericISA::PCStateWithNext::pc(), gem5::GenericISA::PCStateWithNext::pc(), PCStateBase(), serialize(), set(), unserialize(), and update().

◆ _upc

|

protected |

Definition at line 62 of file pcstate.hh.

Referenced by equals(), microPC(), PCStateBase(), serialize(), set(), gem5::GenericISA::DelaySlotUPCState< 4 >::uAdvance(), gem5::GenericISA::DelaySlotUPCState< 4 >::uEnd(), unserialize(), gem5::GenericISA::PCStateWithNext::upc(), gem5::GenericISA::PCStateWithNext::upc(), update(), and uReset().

The documentation for this class was generated from the following file:

- arch/generic/pcstate.hh

Generated on Sat Oct 18 2025 08:06:53 for gem5 by doxygen 1.14.0