#include <cache_blk.hh>

Classes | |

| class | Lock |

| Represents that the indicated thread context has a "lock" on the block, in the LL/SC sense. More... | |

Public Types | |

| enum | CoherenceBits : unsigned { WritableBit = 0x02 , ReadableBit = 0x04 , DirtyBit = 0x08 , AllBits = 0x0E } |

| Cache block's enum listing the supported coherence bits. More... | |

| Public Types inherited from gem5::TaggedEntry | |

| using | KeyType = TaggedTypes::KeyType |

| using | IndexingPolicy = TaggedIndexingPolicy |

| using | TagExtractor = std::function<Addr(Addr)> |

Public Member Functions | |

| CacheBlk () | |

| CacheBlk (const CacheBlk &)=delete | |

| CacheBlk & | operator= (const CacheBlk &)=delete |

| CacheBlk (const CacheBlk &&)=delete | |

| virtual CacheBlk & | operator= (CacheBlk &&other) |

| Move assignment operator. | |

| virtual | ~CacheBlk () |

| virtual void | invalidate () override |

| Invalidate the block and clear all state. | |

| void | setCoherenceBits (unsigned bits) |

| Sets the corresponding coherence bits. | |

| void | clearCoherenceBits (unsigned bits) |

| Clear the corresponding coherence bits. | |

| bool | isSet (unsigned bits) const |

| Checks the given coherence bits are set. | |

| bool | wasPrefetched () const |

| Check if this block was the result of a hardware prefetch, yet to be touched. | |

| void | clearPrefetched () |

| Clear the prefetching bit. | |

| void | setPrefetched () |

| Marks this blocks as a recently prefetched block. | |

| Tick | getWhenReady () const |

| Get tick at which block's data will be available for access. | |

| void | setWhenReady (const Tick tick) |

| Set tick at which block's data will be available for access. | |

| uint32_t | getTaskId () const |

| Get the task id associated to this block. | |

| uint32_t | getSrcRequestorId () const |

| Get the requestor id associated to this block. | |

| uint64_t | getPartitionId () const |

| Getter for _partitionId. | |

| unsigned | getRefCount () const |

| Get the number of references to this block since insertion. | |

| void | increaseRefCount () |

| Get the number of references to this block since insertion. | |

| Tick | getAge () const |

| Get the block's age, that is, the number of ticks since its insertion. | |

| void | insert (const KeyType &tag, const int src_requestor_ID, const uint32_t task_ID, const uint64_t partition_id) |

| Set member variables when a block insertion occurs. | |

| void | trackLoadLocked (PacketPtr pkt) |

| Track the fact that a local locked was issued to the block. | |

| void | clearLoadLocks (const RequestPtr &req) |

| Clear the any load lock that intersect the request, and is from a different context. | |

| std::string | print () const override |

| Pretty-print tag, set and way, and interpret state bits to readable form including mapping to a MOESI state. | |

| bool | checkWrite (PacketPtr pkt) |

| Handle interaction of load-locked operations and stores. | |

| virtual void | insert (const KeyType &key) |

| Insert the block by assigning it a tag and marking it valid. | |

| Public Member Functions inherited from gem5::TaggedEntry | |

| TaggedEntry () | |

| ~TaggedEntry ()=default | |

| void | registerTagExtractor (TagExtractor ext) |

| virtual bool | isValid () const |

| Checks if the entry is valid. | |

| bool | isSecure () const |

| Check if this block holds data from the secure memory space. | |

| virtual Addr | getTag () const |

| Get tag associated to this block. | |

| bool | match (const KeyType &key) const |

| Checks if the given tag information corresponds to this entry's. | |

| std::string | print () const override |

| Prints relevant information about this entry. | |

| Public Member Functions inherited from gem5::ReplaceableEntry | |

| ReplaceableEntry () | |

| virtual | ~ReplaceableEntry ()=default |

| virtual void | setPosition (const uint32_t set, const uint32_t way) |

| Set both the set and way. | |

| uint32_t | getSet () const |

| Get set number. | |

| uint32_t | getWay () const |

| Get way number. | |

Public Attributes | |

| uint8_t * | data = nullptr |

| Contains a copy of the data in this block for easy access. | |

| Tick | whenReady = 0 |

| Which curTick() will this block be accessible. | |

| Public Attributes inherited from gem5::ReplaceableEntry | |

| std::shared_ptr< replacement_policy::ReplacementData > | replacementData |

| Replacement data associated to this entry. | |

Protected Member Functions | |

| void | setTaskId (const uint32_t task_id) |

| Set the task id value. | |

| void | setSrcRequestorId (const uint32_t id) |

| Set the source requestor id. | |

| void | setPartitionId (const uint64_t partitionId) |

| Setter for _partitionId. | |

| void | setRefCount (const unsigned count) |

| Set the number of references to this block since insertion. | |

| void | setTickInserted () |

| Set the current tick as this block's insertion tick. | |

| Protected Member Functions inherited from gem5::TaggedEntry | |

| virtual void | setTag (Addr tag) |

| Set tag associated to this block. | |

| virtual void | setSecure () |

| Set secure bit. | |

| void | clearSecure () |

| Clear secure bit. | |

| virtual void | setValid () |

| Set valid bit. | |

Protected Attributes | |

| std::list< Lock > | lockList |

| List of thread contexts that have performed a load-locked (LL) on the block since the last store. | |

| unsigned | coherence = 0 |

| The current coherence status of this block. | |

| Protected Attributes inherited from gem5::TaggedEntry | |

| TagExtractor | extractTag |

| Callback used to extract the tag from the entry. | |

| Protected Attributes inherited from gem5::ReplaceableEntry | |

| uint32_t | _set |

| Set to which this entry belongs. | |

| uint32_t | _way |

| Way (relative position within the set) to which this entry belongs. | |

Private Attributes | |

| uint32_t | _taskId = 0 |

| Task Id associated with this block. | |

| int | _srcRequestorId = 0 |

| holds the source requestor ID for this block. | |

| uint64_t | _partitionId |

| Partition ID of the activity that allocated this block. | |

| unsigned | _refCount = 0 |

| Number of references to this block since it was brought in. | |

| Tick | _tickInserted = 0 |

| Tick on which the block was inserted in the cache. | |

| bool | _prefetched = 0 |

| Whether this block is an unaccessed hardware prefetch. | |

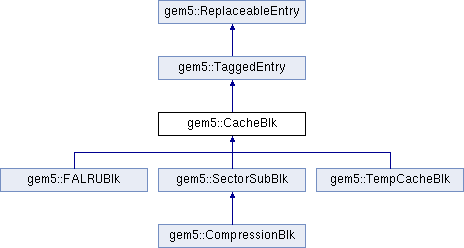

Detailed Description

A Basic Cache block.

Contains information regarding its coherence, prefetching status, as well as a pointer to its data.

Definition at line 71 of file cache_blk.hh.

Member Enumeration Documentation

◆ CoherenceBits

| enum gem5::CacheBlk::CoherenceBits : unsigned |

Cache block's enum listing the supported coherence bits.

The valid bit is not defined here because it is part of a TaggedEntry.

Definition at line 78 of file cache_blk.hh.

Constructor & Destructor Documentation

◆ CacheBlk() [1/3]

|

inline |

Definition at line 156 of file cache_blk.hh.

References invalidate(), and gem5::TaggedEntry::TaggedEntry().

Referenced by CacheBlk(), CacheBlk(), gem5::FALRUBlk::FALRUBlk(), operator=(), operator=(), gem5::SectorSubBlk::SectorSubBlk(), and gem5::TempCacheBlk::TempCacheBlk().

◆ CacheBlk() [2/3]

|

delete |

References CacheBlk().

◆ CacheBlk() [3/3]

|

delete |

References CacheBlk().

◆ ~CacheBlk()

|

inlinevirtual |

Definition at line 197 of file cache_blk.hh.

Member Function Documentation

◆ checkWrite()

|

inline |

Handle interaction of load-locked operations and stores.

- Returns

- True if write should proceed, false otherwise. Returns false only in the case of a failed store conditional.

Definition at line 420 of file cache_blk.hh.

References clearLoadLocks(), gem5::Packet::isLLSC(), gem5::Packet::isWrite(), gem5::MipsISA::l, lockList, and gem5::Packet::req.

Referenced by gem5::BaseCache::satisfyRequest().

◆ clearCoherenceBits()

|

inline |

Clear the corresponding coherence bits.

- Parameters

-

bits The coherence bits to be cleared.

Definition at line 234 of file cache_blk.hh.

References gem5::bits(), and coherence.

Referenced by gem5::Cache::handleSnoop(), gem5::BaseCache::handleTimingReqHit(), gem5::BaseCache::handleTimingReqMiss(), invalidate(), gem5::BaseCache::recvTimingResp(), gem5::BaseCache::satisfyRequest(), gem5::Cache::satisfyRequest(), gem5::Cache::serviceMSHRTargets(), gem5::BaseCache::writebackBlk(), gem5::BaseCache::writebackVisitor(), and gem5::BaseCache::writecleanBlk().

◆ clearLoadLocks()

|

inline |

Clear the any load lock that intersect the request, and is from a different context.

Definition at line 353 of file cache_blk.hh.

References gem5::MipsISA::l, and lockList.

Referenced by checkWrite().

◆ clearPrefetched()

|

inline |

Clear the prefetching bit.

Either because it was recently used, or due to the block being invalidated.

Definition at line 258 of file cache_blk.hh.

References _prefetched.

Referenced by invalidate(), and gem5::BaseCache::recvTimingReq().

◆ getAge()

|

inline |

Get the block's age, that is, the number of ticks since its insertion.

- Returns

- The block's age.

Definition at line 308 of file cache_blk.hh.

References _tickInserted, and gem5::curTick().

Referenced by gem5::BaseTags::computeStatsVisitor().

◆ getPartitionId()

|

inline |

Getter for _partitionId.

Definition at line 294 of file cache_blk.hh.

References _partitionId.

Referenced by gem5::BaseSetAssoc::invalidate(), and gem5::BaseCache::updateCompressionData().

◆ getRefCount()

|

inline |

Get the number of references to this block since insertion.

Definition at line 297 of file cache_blk.hh.

References _refCount.

Referenced by gem5::BaseTags::cleanupRefsVisitor(), and gem5::BaseTags::invalidate().

◆ getSrcRequestorId()

|

inline |

Get the requestor id associated to this block.

Definition at line 291 of file cache_blk.hh.

References _srcRequestorId.

Referenced by gem5::BaseCache::cmpAndSwap(), gem5::BaseCache::hasBeenPrefetched(), gem5::BaseTags::invalidate(), gem5::BaseCache::satisfyRequest(), and gem5::BaseCache::updateBlockData().

◆ getTaskId()

|

inline |

Get the task id associated to this block.

Definition at line 288 of file cache_blk.hh.

References _taskId.

Referenced by gem5::Cache::cleanEvictBlk(), gem5::BaseTags::computeStatsVisitor(), gem5::BaseCache::writebackBlk(), gem5::BaseCache::writebackVisitor(), and gem5::BaseCache::writecleanBlk().

◆ getWhenReady()

|

inline |

Get tick at which block's data will be available for access.

- Returns

- Data ready tick.

Definition at line 268 of file cache_blk.hh.

References gem5::MaxTick, and whenReady.

Referenced by gem5::BaseCache::calculateAccessLatency().

◆ increaseRefCount()

|

inline |

Get the number of references to this block since insertion.

Definition at line 300 of file cache_blk.hh.

References _refCount.

Referenced by gem5::BaseSetAssoc::accessBlock(), gem5::SectorTags::accessBlock(), and insert().

◆ insert() [1/2]

|

inlinevirtual |

Insert the block by assigning it a tag and marking it valid.

Touches block if it hadn't been touched previously.

- Parameters

-

tag The tag value.

Reimplemented from gem5::TaggedEntry.

Reimplemented in gem5::SectorSubBlk, and gem5::TempCacheBlk.

Definition at line 170 of file tagged_entry.hh.

◆ insert() [2/2]

| void gem5::CacheBlk::insert | ( | const KeyType & | tag, |

| const int | src_requestor_ID, | ||

| const uint32_t | task_ID, | ||

| const uint64_t | partition_id ) |

Set member variables when a block insertion occurs.

Resets reference count to 1 (the insertion counts as a reference), and touch block if it hadn't been touched previously. Sets the insertion tick to the current tick. Marks the block valid.

- Parameters

-

tag Block address tag. is_secure Whether the block is in secure space or not. src_requestor_ID The source requestor ID. task_ID The new task ID. partition_id The source partition ID.

Definition at line 50 of file cache_blk.cc.

References increaseRefCount(), insert(), gem5::TaggedEntry::isValid(), setPartitionId(), setSrcRequestorId(), setTaskId(), and setTickInserted().

Referenced by insert(), gem5::SectorSubBlk::insert(), gem5::TempCacheBlk::insert(), gem5::BaseTags::insertBlock(), and operator=().

◆ invalidate()

|

inlineoverridevirtual |

Invalidate the block and clear all state.

Reimplemented from gem5::TaggedEntry.

Reimplemented in gem5::CompressionBlk, gem5::SectorSubBlk, and gem5::TempCacheBlk.

Definition at line 202 of file cache_blk.hh.

References AllBits, clearCoherenceBits(), clearPrefetched(), gem5::TaggedEntry::invalidate(), gem5::Request::invldRequestorId, lockList, gem5::MaxTick, setPartitionId(), setRefCount(), setSrcRequestorId(), setTaskId(), setWhenReady(), and gem5::context_switch_task_id::Unknown.

Referenced by CacheBlk(), gem5::BaseTags::invalidate(), gem5::SectorSubBlk::invalidate(), and gem5::TempCacheBlk::invalidate().

◆ isSet()

|

inline |

Checks the given coherence bits are set.

- Returns

- True if the block is readable.

Definition at line 242 of file cache_blk.hh.

References gem5::bits(), coherence, and gem5::TaggedEntry::isValid().

Referenced by gem5::BaseCache::access(), gem5::Cache::cleanEvictBlk(), gem5::Cache::createMissPacket(), gem5::Cache::evictBlock(), gem5::NoncoherentCache::evictBlock(), gem5::BaseCache::functionalAccess(), gem5::Cache::handleSnoop(), gem5::BaseCache::handleTimingReqMiss(), gem5::BaseCache::invalidateVisitor(), gem5::BaseCache::isDirty(), gem5::BaseCache::maintainClusivity(), print(), gem5::BaseCache::recvAtomic(), gem5::BaseCache::recvTimingReq(), gem5::BaseCache::recvTimingResp(), gem5::BaseCache::satisfyRequest(), gem5::Cache::satisfyRequest(), gem5::BaseCache::sendMSHRQueuePacket(), gem5::Cache::serviceMSHRTargets(), gem5::BaseCache::writebackBlk(), gem5::BaseCache::writebackVisitor(), and gem5::BaseCache::writecleanBlk().

◆ operator=() [1/2]

Move assignment operator.

This should only be used to move an existing valid entry into an invalid one, not to create a new entry. In the end the valid entry will become invalid, and the invalid, valid. All location related variables will remain the same, that is, an entry cannot move its data, just its metadata contents.

Reimplemented in gem5::CompressionBlk, gem5::FALRUBlk, gem5::SectorSubBlk, and gem5::TempCacheBlk.

Definition at line 173 of file cache_blk.hh.

References CacheBlk(), gem5::curTick(), insert(), gem5::TaggedEntry::isValid(), lockList, setCoherenceBits(), setPartitionId(), setPrefetched(), setRefCount(), setSrcRequestorId(), setTaskId(), and setWhenReady().

◆ operator=() [2/2]

References CacheBlk().

Referenced by gem5::CompressionBlk::operator=().

◆ print()

|

inlineoverridevirtual |

Pretty-print tag, set and way, and interpret state bits to readable form including mapping to a MOESI state.

- Returns

- string with basic state information

state M O E S I writable 1 0 1 0 0 dirty 1 1 0 0 0 valid 1 1 1 1 0

state writable dirty valid M 1 1 1 O 0 1 1 E 1 0 1 S 0 0 1 I 0 0 0

Note that only one cache ever has a block in Modified or Owned state, i.e., only one cache owns the block, or equivalently has the DirtyBit bit set. However, multiple caches on the same path to memory can have a block in the Exclusive state (despite the name). Exclusive means this cache has the only copy at this level of the hierarchy, i.e., there may be copies in caches above this cache (in various states), but there are no peers that have copies on this branch of the hierarchy, and no caches at or above this level on any other branch have copies either.

Reimplemented from gem5::ReplaceableEntry.

Reimplemented in gem5::CompressionBlk, gem5::FALRUBlk, and gem5::SectorSubBlk.

Definition at line 372 of file cache_blk.hh.

References coherence, gem5::csprintf(), DirtyBit, isSet(), gem5::TaggedEntry::isValid(), gem5::TaggedEntry::print(), ReadableBit, gem5::ArmISA::s, wasPrefetched(), and WritableBit.

Referenced by gem5::BaseCache::access(), gem5::BaseCache::allocateBlock(), gem5::Cache::handleAtomicReqMiss(), gem5::BaseCache::handleFill(), gem5::Cache::handleSnoop(), gem5::FALRUBlk::print(), gem5::SectorSubBlk::print(), gem5::BaseCache::recvAtomic(), gem5::BaseCache::sendMSHRQueuePacket(), and gem5::BaseCache::updateCompressionData().

◆ setCoherenceBits()

|

inline |

Sets the corresponding coherence bits.

- Parameters

-

bits The coherence bits to be set.

Definition at line 223 of file cache_blk.hh.

References gem5::bits(), coherence, and gem5::TaggedEntry::isValid().

Referenced by gem5::BaseCache::access(), gem5::NoncoherentCache::access(), gem5::BaseCache::cmpAndSwap(), gem5::BaseCache::handleFill(), operator=(), gem5::BaseCache::recvTimingReq(), gem5::BaseCache::recvTimingResp(), gem5::BaseCache::satisfyRequest(), and gem5::Cache::serviceMSHRTargets().

◆ setPartitionId()

|

inlineprotected |

Setter for _partitionId.

Definition at line 479 of file cache_blk.hh.

References _partitionId.

Referenced by insert(), invalidate(), and operator=().

◆ setPrefetched()

|

inline |

Marks this blocks as a recently prefetched block.

Definition at line 261 of file cache_blk.hh.

References _prefetched.

Referenced by operator=(), gem5::Cache::serviceMSHRTargets(), and gem5::NoncoherentCache::serviceMSHRTargets().

◆ setRefCount()

|

inlineprotected |

Set the number of references to this block since insertion.

Definition at line 482 of file cache_blk.hh.

References _refCount, and gem5::X86ISA::count.

Referenced by invalidate(), and operator=().

◆ setSrcRequestorId()

|

inlineprotected |

Set the source requestor id.

Definition at line 475 of file cache_blk.hh.

References _srcRequestorId, and gem5::ArmISA::id.

Referenced by insert(), invalidate(), and operator=().

◆ setTaskId()

|

inlineprotected |

Set the task id value.

Definition at line 472 of file cache_blk.hh.

References _taskId.

Referenced by insert(), invalidate(), and operator=().

◆ setTickInserted()

|

inlineprotected |

Set the current tick as this block's insertion tick.

Definition at line 485 of file cache_blk.hh.

References _tickInserted, and gem5::curTick().

Referenced by insert().

◆ setWhenReady()

|

inline |

Set tick at which block's data will be available for access.

The new tick must be chronologically sequential with respect to previous accesses.

- Parameters

-

tick New data ready tick.

Definition at line 281 of file cache_blk.hh.

References _tickInserted, and whenReady.

Referenced by gem5::BaseCache::access(), gem5::BaseCache::handleFill(), invalidate(), and operator=().

◆ trackLoadLocked()

|

inline |

Track the fact that a local locked was issued to the block.

Invalidate any previous LL to the same address.

Definition at line 335 of file cache_blk.hh.

References gem5::Packet::isLLSC(), gem5::MipsISA::l, lockList, and gem5::Packet::req.

Referenced by gem5::BaseCache::satisfyRequest().

◆ wasPrefetched()

|

inline |

Check if this block was the result of a hardware prefetch, yet to be touched.

- Returns

- True if the block was a hardware prefetch, unaccesed.

Definition at line 252 of file cache_blk.hh.

References _prefetched.

Referenced by gem5::BaseCache::hasBeenPrefetched(), gem5::BaseCache::hasBeenPrefetched(), gem5::BaseCache::invalidateBlock(), print(), gem5::BaseCache::recvTimingReq(), gem5::BaseCache::satisfyRequest(), and gem5::BaseCache::updateBlockData().

Member Data Documentation

◆ _partitionId

|

private |

Partition ID of the activity that allocated this block.

Definition at line 496 of file cache_blk.hh.

Referenced by getPartitionId(), and setPartitionId().

◆ _prefetched

|

private |

Whether this block is an unaccessed hardware prefetch.

Definition at line 508 of file cache_blk.hh.

Referenced by clearPrefetched(), setPrefetched(), and wasPrefetched().

◆ _refCount

|

private |

Number of references to this block since it was brought in.

Definition at line 499 of file cache_blk.hh.

Referenced by getRefCount(), increaseRefCount(), and setRefCount().

◆ _srcRequestorId

|

private |

holds the source requestor ID for this block.

Definition at line 492 of file cache_blk.hh.

Referenced by getSrcRequestorId(), and setSrcRequestorId().

◆ _taskId

|

private |

Task Id associated with this block.

Definition at line 489 of file cache_blk.hh.

Referenced by getTaskId(), and setTaskId().

◆ _tickInserted

|

private |

Tick on which the block was inserted in the cache.

Its value is only meaningful if the block is valid.

Definition at line 505 of file cache_blk.hh.

Referenced by getAge(), setTickInserted(), and setWhenReady().

◆ coherence

|

protected |

The current coherence status of this block.

- See also

- CoherenceBits

Definition at line 464 of file cache_blk.hh.

Referenced by clearCoherenceBits(), isSet(), print(), and setCoherenceBits().

◆ data

| uint8_t* gem5::CacheBlk::data = nullptr |

Contains a copy of the data in this block for easy access.

This is used for efficient execution when the data could be actually stored in another format (COW, compressed, sub-blocked, etc). In all cases the data stored here should be kept consistant with the actual data referenced by this block.

Definition at line 104 of file cache_blk.hh.

Referenced by gem5::BaseCache::cmpAndSwap(), gem5::BaseCache::functionalAccess(), gem5::Cache::handleSnoop(), gem5::BaseCache::satisfyRequest(), gem5::BaseSetAssoc::tagsInit(), gem5::CompressedTags::tagsInit(), gem5::SectorTags::tagsInit(), gem5::TempCacheBlk::TempCacheBlk(), gem5::BaseCache::updateBlockData(), gem5::BaseCache::writebackBlk(), gem5::BaseCache::writebackVisitor(), gem5::BaseCache::writecleanBlk(), and gem5::TempCacheBlk::~TempCacheBlk().

◆ lockList

List of thread contexts that have performed a load-locked (LL) on the block since the last store.

Definition at line 153 of file cache_blk.hh.

Referenced by checkWrite(), clearLoadLocks(), invalidate(), operator=(), and trackLoadLocked().

◆ whenReady

| Tick gem5::CacheBlk::whenReady = 0 |

Which curTick() will this block be accessible.

Its value is only meaningful if the block is valid.

Definition at line 110 of file cache_blk.hh.

Referenced by getWhenReady(), and setWhenReady().

The documentation for this class was generated from the following files:

- mem/cache/cache_blk.hh

- mem/cache/cache_blk.cc

Generated on Sat Oct 18 2025 08:06:49 for gem5 by doxygen 1.14.0