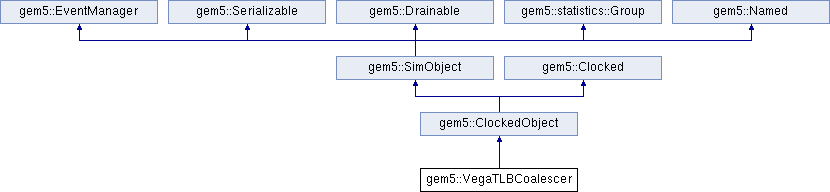

The VegaTLBCoalescer is a ClockedObject sitting on the front side (CPUSide) of each TLB. More...

#include <tlb_coalescer.hh>

Classes | |

| class | CpuSidePort |

| class | MemSidePort |

Public Types | |

| typedef std::vector< PacketPtr > | coalescedReq |

| typedef std::map< Tick, std::vector< coalescedReq > > | CoalescingFIFO |

| typedef std::unordered_map< Addr, coalescedReq > | CoalescingTable |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| VegaTLBCoalescer (const VegaTLBCoalescerParams &p) | |

| ~VegaTLBCoalescer () | |

| bool | canCoalesce (PacketPtr pkt1, PacketPtr pkt2) |

| void | updatePhysAddresses (PacketPtr pkt) |

| void | regStats () override |

| Callback to set stat parameters. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| void | processProbeTLBEvent () |

| void | processCleanupEvent () |

| unsigned int | availDownstreamSlots () |

| void | insertStalledPortIfNotMapped (CpuSidePort *) |

| bool | mustStallCUPort (CpuSidePort *) |

| bool | stalledPorts () |

| void | decrementNumDownstream () |

| void | incrementNumDownstream () |

| void | unstallPorts () |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Public Attributes | |

| int | TLBProbesPerCycle |

| int | coalescingWindow |

| bool | disableCoalescing |

| CoalescingFIFO | coalescerFIFO |

| CoalescingTable | issuedTranslationsTable |

| statistics::Scalar | uncoalescedAccesses |

| statistics::Scalar | coalescedAccesses |

| statistics::Scalar | queuingCycles |

| statistics::Scalar | localqueuingCycles |

| statistics::Scalar | localCycles |

| statistics::Formula | localLatency |

| statistics::Formula | latency |

| std::vector< CpuSidePort * > | cpuSidePort |

| std::vector< MemSidePort * > | memSidePort |

| EventFunctionWrapper | probeTLBEvent |

| This event issues the TLB probes. | |

| EventFunctionWrapper | cleanupEvent |

| The cleanupEvent is scheduled after a TLBEvent triggers in order to free memory and do the required clean-up. | |

| int | tlb_level |

| int | maxDownstream |

| unsigned int | numDownstream |

| CpuSidePort * | stalledPort |

| std::queue< CpuSidePort * > | stalledPortsQueue |

| std::map< CpuSidePort *, CpuSidePort * > | stalledPortsMap |

| std::queue< Addr > | cleanupQueue |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Detailed Description

The VegaTLBCoalescer is a ClockedObject sitting on the front side (CPUSide) of each TLB.

It receives packets and issues coalesced requests to the TLB below it. It controls how requests are coalesced (the rules) and the permitted number of TLB probes per cycle (i.e., how many coalesced requests it feeds the TLB per cycle).

Definition at line 60 of file tlb_coalescer.hh.

Member Typedef Documentation

◆ coalescedReq

Definition at line 75 of file tlb_coalescer.hh.

◆ CoalescingFIFO

| typedef std::map<Tick, std::vector<coalescedReq> > gem5::VegaTLBCoalescer::CoalescingFIFO |

Definition at line 94 of file tlb_coalescer.hh.

◆ CoalescingTable

| typedef std::unordered_map<Addr, coalescedReq> gem5::VegaTLBCoalescer::CoalescingTable |

Definition at line 107 of file tlb_coalescer.hh.

Constructor & Destructor Documentation

◆ VegaTLBCoalescer()

| gem5::VegaTLBCoalescer::VegaTLBCoalescer | ( | const VegaTLBCoalescerParams & | p | ) |

Definition at line 46 of file tlb_coalescer.cc.

References gem5::ClockedObject::ClockedObject(), coalescingWindow, disableCoalescing, gem5::MipsISA::p, probeTLBEvent, processProbeTLBEvent(), and TLBProbesPerCycle.

Referenced by gem5::VegaTLBCoalescer::CpuSidePort::CpuSidePort(), and gem5::VegaTLBCoalescer::MemSidePort::MemSidePort().

◆ ~VegaTLBCoalescer()

|

inline |

Definition at line 64 of file tlb_coalescer.hh.

Member Function Documentation

◆ availDownstreamSlots()

|

inline |

Definition at line 215 of file tlb_coalescer.hh.

References maxDownstream, numDownstream, and tlb_level.

Referenced by mustStallCUPort(), processProbeTLBEvent(), and unstallPorts().

◆ canCoalesce()

Definition at line 101 of file tlb_coalescer.cc.

References disableCoalescing, gem5::GpuTranslationState::isPrefetch, gem5::VegaISA::PageBytes, gem5::Packet::req, gem5::GpuTranslationState::reqCnt, gem5::roundDown(), gem5::safe_cast(), gem5::Packet::senderState, and gem5::GpuTranslationState::tlbMode.

◆ decrementNumDownstream()

|

inline |

Definition at line 228 of file tlb_coalescer.hh.

References numDownstream, and tlb_level.

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

gem5 has a request and response port interface. All memory objects are connected together via ports. These ports provide a rigid interface between these memory objects. These ports implement three different memory system modes: timing, atomic, and functional. The most important mode is the timing mode and here timing mode is used for conducting cycle-level timing experiments. The other modes are only used in special circumstances and should not be used to conduct cycle-level timing experiments. The other modes are only used in special circumstances. These ports allow SimObjects to communicate with each other.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from gem5::SimObject.

Definition at line 75 of file tlb_coalescer.cc.

References cpuSidePort, memSidePort, and panic.

◆ incrementNumDownstream()

|

inline |

Definition at line 234 of file tlb_coalescer.hh.

References maxDownstream, numDownstream, and tlb_level.

Referenced by processProbeTLBEvent().

◆ insertStalledPortIfNotMapped()

| void gem5::VegaTLBCoalescer::insertStalledPortIfNotMapped | ( | CpuSidePort * | port | ) |

Definition at line 621 of file tlb_coalescer.cc.

References DPRINTF, stalledPortsMap, stalledPortsQueue, and tlb_level.

Referenced by mustStallCUPort().

◆ mustStallCUPort()

| bool gem5::VegaTLBCoalescer::mustStallCUPort | ( | CpuSidePort * | port | ) |

Definition at line 635 of file tlb_coalescer.cc.

References availDownstreamSlots(), DPRINTF, insertStalledPortIfNotMapped(), maxDownstream, numDownstream, tlb_level, and warn.

◆ processCleanupEvent()

| void gem5::VegaTLBCoalescer::processCleanupEvent | ( | ) |

Definition at line 564 of file tlb_coalescer.cc.

References cleanupQueue, DPRINTF, and issuedTranslationsTable.

◆ processProbeTLBEvent()

| void gem5::VegaTLBCoalescer::processProbeTLBEvent | ( | ) |

Definition at line 428 of file tlb_coalescer.cc.

References availDownstreamSlots(), coalescerFIFO, gem5::Clocked::curCycle(), gem5::Clocked::cyclesToTicks(), DPRINTF, gem5::ArmISA::i, incrementNumDownstream(), gem5::GpuTranslationState::isPrefetch, issuedTranslationsTable, localqueuingCycles, memSidePort, gem5::Named::name(), gem5::VegaISA::PageBytes, probeTLBEvent, queuingCycles, gem5::Packet::req, gem5::GpuTranslationState::reqCnt, gem5::roundDown(), gem5::safe_cast(), gem5::EventManager::schedule(), gem5::Packet::senderState, tlb_level, and TLBProbesPerCycle.

Referenced by VegaTLBCoalescer().

◆ regStats()

|

overridevirtual |

Callback to set stat parameters.

This callback is typically used for complex stats (e.g., distributions) that need parameters in addition to a name and a description. Stat names and descriptions should typically be set from the constructor usingo from the constructor using the ADD_STAT macro.

Reimplemented from gem5::statistics::Group.

Definition at line 577 of file tlb_coalescer.cc.

References coalescedAccesses, latency, localCycles, localLatency, localqueuingCycles, gem5::Named::name(), queuingCycles, gem5::statistics::Group::regStats(), and uncoalescedAccesses.

◆ stalledPorts()

|

inline |

Definition at line 223 of file tlb_coalescer.hh.

References stalledPortsQueue, and tlb_level.

Referenced by unstallPorts().

◆ unstallPorts()

| void gem5::VegaTLBCoalescer::unstallPorts | ( | ) |

Definition at line 652 of file tlb_coalescer.cc.

References availDownstreamSlots(), DPRINTF, stalledPorts(), stalledPortsMap, stalledPortsQueue, and tlb_level.

◆ updatePhysAddresses()

| void gem5::VegaTLBCoalescer::updatePhysAddresses | ( | PacketPtr | pkt | ) |

Definition at line 146 of file tlb_coalescer.cc.

References cleanupEvent, cleanupQueue, gem5::Clocked::curCycle(), gem5::curTick(), DPRINTF, gem5::GpuTranslationState::hitLevel, gem5::ArmISA::i, gem5::GpuTranslationState::isPrefetch, gem5::Packet::isRequest(), issuedTranslationsTable, localCycles, gem5::Packet::makeTimingResponse(), gem5::VegaISA::PageBytes, gem5::GpuTranslationState::ports, gem5::Packet::req, gem5::GpuTranslationState::reqCnt, gem5::roundDown(), gem5::safe_cast(), gem5::EventManager::schedule(), gem5::Packet::senderState, gem5::ResponsePort::sendTimingResp(), gem5::GpuTranslationState::tlbEntry, and gem5::Request::UNCACHEABLE.

Member Data Documentation

◆ cleanupEvent

| EventFunctionWrapper gem5::VegaTLBCoalescer::cleanupEvent |

The cleanupEvent is scheduled after a TLBEvent triggers in order to free memory and do the required clean-up.

Definition at line 205 of file tlb_coalescer.hh.

Referenced by updatePhysAddresses().

◆ cleanupQueue

| std::queue<Addr> gem5::VegaTLBCoalescer::cleanupQueue |

Definition at line 245 of file tlb_coalescer.hh.

Referenced by processCleanupEvent(), and updatePhysAddresses().

◆ coalescedAccesses

| statistics::Scalar gem5::VegaTLBCoalescer::coalescedAccesses |

Definition at line 114 of file tlb_coalescer.hh.

Referenced by regStats().

◆ coalescerFIFO

| CoalescingFIFO gem5::VegaTLBCoalescer::coalescerFIFO |

Definition at line 96 of file tlb_coalescer.hh.

Referenced by processProbeTLBEvent().

◆ coalescingWindow

| int gem5::VegaTLBCoalescer::coalescingWindow |

Definition at line 71 of file tlb_coalescer.hh.

Referenced by VegaTLBCoalescer().

◆ cpuSidePort

| std::vector<CpuSidePort*> gem5::VegaTLBCoalescer::cpuSidePort |

Definition at line 191 of file tlb_coalescer.hh.

Referenced by getPort().

◆ disableCoalescing

| bool gem5::VegaTLBCoalescer::disableCoalescing |

Definition at line 78 of file tlb_coalescer.hh.

Referenced by canCoalesce(), and VegaTLBCoalescer().

◆ issuedTranslationsTable

| CoalescingTable gem5::VegaTLBCoalescer::issuedTranslationsTable |

Definition at line 109 of file tlb_coalescer.hh.

Referenced by processCleanupEvent(), processProbeTLBEvent(), and updatePhysAddresses().

◆ latency

| statistics::Formula gem5::VegaTLBCoalescer::latency |

Definition at line 129 of file tlb_coalescer.hh.

Referenced by regStats().

◆ localCycles

| statistics::Scalar gem5::VegaTLBCoalescer::localCycles |

Definition at line 125 of file tlb_coalescer.hh.

Referenced by regStats(), and updatePhysAddresses().

◆ localLatency

| statistics::Formula gem5::VegaTLBCoalescer::localLatency |

Definition at line 127 of file tlb_coalescer.hh.

Referenced by regStats().

◆ localqueuingCycles

| statistics::Scalar gem5::VegaTLBCoalescer::localqueuingCycles |

Definition at line 124 of file tlb_coalescer.hh.

Referenced by processProbeTLBEvent(), and regStats().

◆ maxDownstream

| int gem5::VegaTLBCoalescer::maxDownstream |

Definition at line 208 of file tlb_coalescer.hh.

Referenced by availDownstreamSlots(), incrementNumDownstream(), and mustStallCUPort().

◆ memSidePort

| std::vector<MemSidePort*> gem5::VegaTLBCoalescer::memSidePort |

Definition at line 193 of file tlb_coalescer.hh.

Referenced by getPort(), and processProbeTLBEvent().

◆ numDownstream

| unsigned int gem5::VegaTLBCoalescer::numDownstream |

Definition at line 209 of file tlb_coalescer.hh.

Referenced by availDownstreamSlots(), decrementNumDownstream(), incrementNumDownstream(), and mustStallCUPort().

◆ probeTLBEvent

| EventFunctionWrapper gem5::VegaTLBCoalescer::probeTLBEvent |

This event issues the TLB probes.

Definition at line 200 of file tlb_coalescer.hh.

Referenced by processProbeTLBEvent(), and VegaTLBCoalescer().

◆ queuingCycles

| statistics::Scalar gem5::VegaTLBCoalescer::queuingCycles |

Definition at line 119 of file tlb_coalescer.hh.

Referenced by processProbeTLBEvent(), and regStats().

◆ stalledPort

| CpuSidePort* gem5::VegaTLBCoalescer::stalledPort |

Definition at line 210 of file tlb_coalescer.hh.

◆ stalledPortsMap

| std::map<CpuSidePort *, CpuSidePort *> gem5::VegaTLBCoalescer::stalledPortsMap |

Definition at line 213 of file tlb_coalescer.hh.

Referenced by insertStalledPortIfNotMapped(), and unstallPorts().

◆ stalledPortsQueue

| std::queue<CpuSidePort *> gem5::VegaTLBCoalescer::stalledPortsQueue |

Definition at line 211 of file tlb_coalescer.hh.

Referenced by insertStalledPortIfNotMapped(), stalledPorts(), and unstallPorts().

◆ tlb_level

| int gem5::VegaTLBCoalescer::tlb_level |

Definition at line 207 of file tlb_coalescer.hh.

Referenced by availDownstreamSlots(), decrementNumDownstream(), incrementNumDownstream(), insertStalledPortIfNotMapped(), mustStallCUPort(), processProbeTLBEvent(), stalledPorts(), and unstallPorts().

◆ TLBProbesPerCycle

| int gem5::VegaTLBCoalescer::TLBProbesPerCycle |

Definition at line 67 of file tlb_coalescer.hh.

Referenced by processProbeTLBEvent(), and VegaTLBCoalescer().

◆ uncoalescedAccesses

| statistics::Scalar gem5::VegaTLBCoalescer::uncoalescedAccesses |

Definition at line 112 of file tlb_coalescer.hh.

Referenced by regStats().

The documentation for this class was generated from the following files:

- arch/amdgpu/vega/tlb_coalescer.hh

- arch/amdgpu/vega/tlb_coalescer.cc

Generated on Sat Oct 18 2025 08:06:55 for gem5 by doxygen 1.14.0