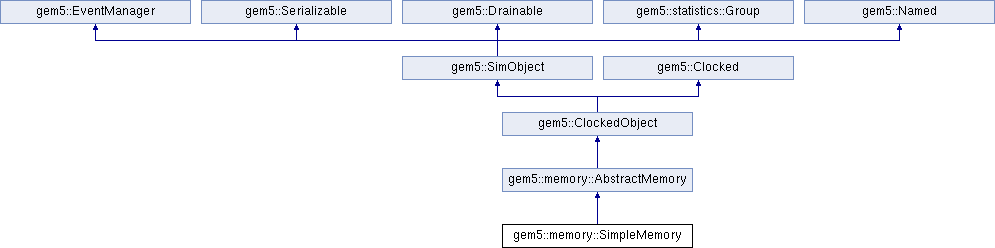

The simple memory is a basic single-ported memory controller with a configurable throughput and latency. More...

#include <simple_mem.hh>

Classes | |

| class | DeferredPacket |

| A deferred packet stores a packet along with its scheduled transmission time. More... | |

| class | MemoryPort |

Public Member Functions | |

| SimpleMemory (const SimpleMemoryParams &p) | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Public Member Functions inherited from gem5::memory::AbstractMemory | |

| PARAMS (AbstractMemory) | |

| AbstractMemory (const Params &p) | |

| virtual | ~AbstractMemory () |

| void | initState () override |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| bool | isNull () const |

| See if this is a null memory that should never store data and always return zero. | |

| void | setBackingStore (uint8_t *pmem_addr) |

| Set the host memory backing store to be used by this memory controller. | |

| void | getBackdoor (MemBackdoorPtr &bd_ptr) |

| const std::list< LockedAddr > & | getLockedAddrList () const |

| Get the list of locked addresses to allow checkpointing. | |

| void | addLockedAddr (LockedAddr addr) |

| Add a locked address to allow for checkpointing. | |

| System * | system () const |

| read the system pointer Implemented for completeness with the setter | |

| void | system (System *sys) |

| Set the system pointer on this memory This can't be done via a python parameter because the system needs pointers to all the memories and the reverse would create a cycle in the object graph. | |

| AddrRange | getAddrRange () const |

| Get the address range. | |

| uint8_t * | toHostAddr (Addr addr) const |

| Transform a gem5 address space address into its physical counterpart in the host address space. | |

| uint64_t | size () const |

| Get the memory size. | |

| Addr | start () const |

| Get the start address. | |

| bool | isConfReported () const |

| Should this memory be passed to the kernel and part of the OS physical memory layout. | |

| bool | isInAddrMap () const |

| Some memories are used as shadow memories or should for other reasons not be part of the global address map. | |

| bool | isKvmMap () const |

| When shadow memories are in use, KVM may want to make one or the other, but cannot map both into the guest address space. | |

| void | access (PacketPtr pkt) |

| Perform an untimed memory access and update all the state (e.g. | |

| void | functionalAccess (PacketPtr pkt) |

| Perform an untimed memory read or write without changing anything but the memory itself. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| Tick | recvAtomic (PacketPtr pkt) |

| Tick | recvAtomicBackdoor (PacketPtr pkt, MemBackdoorPtr &_backdoor) |

| void | recvFunctional (PacketPtr pkt) |

| void | recvMemBackdoorReq (const MemBackdoorReq &req, MemBackdoorPtr &backdoor) |

| bool | recvTimingReq (PacketPtr pkt) |

| void | recvRespRetry () |

| Protected Member Functions inherited from gem5::memory::AbstractMemory | |

| bool | checkLockedAddrList (PacketPtr pkt) |

| void | trackLoadLocked (PacketPtr pkt) |

| bool | writeOK (PacketPtr pkt) |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Private Member Functions | |

| void | release () |

| Release the memory after being busy and send a retry if a request was rejected in the meanwhile. | |

| void | dequeue () |

| Dequeue a packet from our internal packet queue and move it to the port where it will be sent as soon as possible. | |

| Tick | getLatency () const |

| Detemine the latency. | |

Private Attributes | |

| MemoryPort | port |

| const Tick | latency |

| Latency from that a request is accepted until the response is ready to be sent. | |

| const Tick | latency_var |

| Fudge factor added to the latency. | |

| std::list< DeferredPacket > | packetQueue |

| Internal (unbounded) storage to mimic the delay caused by the actual memory access. | |

| const double | bandwidth |

| Bandwidth in ticks per byte. | |

| bool | isBusy |

| Track the state of the memory as either idle or busy, no need for an enum with only two states. | |

| bool | retryReq |

| Remember if we have to retry an outstanding request that arrived while we were busy. | |

| bool | retryResp |

| Remember if we failed to send a response and are awaiting a retry. | |

| Random::RandomPtr | rng = Random::genRandom() |

| EventFunctionWrapper | releaseEvent |

| EventFunctionWrapper | dequeueEvent |

| std::unique_ptr< Packet > | pendingDelete |

| Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call. | |

Additional Inherited Members | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| Protected Attributes inherited from gem5::memory::AbstractMemory | |

| AddrRange | range |

| uint8_t * | pmemAddr |

| MemBackdoor | backdoor |

| const bool | confTableReported |

| const bool | inAddrMap |

| const bool | kvmMap |

| const bool | writeable |

| const bool | collectStats |

| std::list< LockedAddr > | lockedAddrList |

| System * | _system |

| Pointer to the System object. | |

| gem5::memory::AbstractMemory::MemStats | stats |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Detailed Description

The simple memory is a basic single-ported memory controller with a configurable throughput and latency.

- See also

- gem5 Memory System

Definition at line 68 of file simple_mem.hh.

Constructor & Destructor Documentation

◆ SimpleMemory()

| gem5::memory::SimpleMemory::SimpleMemory | ( | const SimpleMemoryParams & | p | ) |

Definition at line 53 of file simple_mem.cc.

References gem5::memory::AbstractMemory::AbstractMemory(), bandwidth, isBusy, latency, latency_var, gem5::Named::name(), gem5::MipsISA::p, port, release(), releaseEvent, retryReq, and retryResp.

Referenced by gem5::memory::SimpleMemory::MemoryPort::MemoryPort().

Member Function Documentation

◆ dequeue()

|

private |

Dequeue a packet from our internal packet queue and move it to the port where it will be sent as soon as possible.

Definition at line 212 of file simple_mem.cc.

References gem5::curTick(), dequeueEvent, DPRINTF, gem5::Draining, gem5::Drainable::drainState(), packetQueue, gem5::memory::SimpleMemory::DeferredPacket::pkt, port, gem5::EventManager::reschedule(), retryResp, and gem5::Drainable::signalDrainDone().

Referenced by recvRespRetry().

◆ drain()

|

overridevirtual |

Provide a default implementation of the drain interface for objects that don't need draining.

Reimplemented from gem5::SimObject.

Definition at line 262 of file simple_mem.cc.

References DPRINTF, gem5::Drained, gem5::Draining, and packetQueue.

◆ getLatency()

|

private |

Detemine the latency.

- Returns

- the latency seen by the current packet

Definition at line 237 of file simple_mem.cc.

References latency, latency_var, and rng.

Referenced by recvAtomic(), and recvTimingReq().

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

gem5 has a request and response port interface. All memory objects are connected together via ports. These ports provide a rigid interface between these memory objects. These ports implement three different memory system modes: timing, atomic, and functional. The most important mode is the timing mode and here timing mode is used for conducting cycle-level timing experiments. The other modes are only used in special circumstances and should not be used to conduct cycle-level timing experiments. The other modes are only used in special circumstances. These ports allow SimObjects to communicate with each other.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from gem5::SimObject.

Definition at line 252 of file simple_mem.cc.

References gem5::SimObject::getPort(), and port.

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Definition at line 64 of file simple_mem.cc.

References gem5::SimObject::init(), and port.

◆ recvAtomic()

Definition at line 76 of file simple_mem.cc.

References gem5::memory::AbstractMemory::access(), gem5::Packet::cacheResponding(), getLatency(), and panic_if.

Referenced by recvAtomicBackdoor(), and recvTimingReq().

◆ recvAtomicBackdoor()

|

protected |

Definition at line 86 of file simple_mem.cc.

References gem5::memory::AbstractMemory::getBackdoor(), latency, and recvAtomic().

◆ recvFunctional()

|

protected |

Definition at line 94 of file simple_mem.cc.

References gem5::memory::AbstractMemory::functionalAccess(), gem5::Named::name(), gem5::MipsISA::p, packetQueue, gem5::Packet::popLabel(), gem5::Packet::pushLabel(), and gem5::Packet::trySatisfyFunctional().

◆ recvMemBackdoorReq()

|

protected |

Definition at line 112 of file simple_mem.cc.

References gem5::memory::AbstractMemory::getBackdoor().

◆ recvRespRetry()

|

protected |

Definition at line 244 of file simple_mem.cc.

◆ recvTimingReq()

|

protected |

Definition at line 119 of file simple_mem.cc.

References bandwidth, gem5::Packet::cacheResponding(), gem5::Packet::cmdString(), gem5::curTick(), dequeueEvent, gem5::Packet::getAddr(), getLatency(), gem5::Packet::getSize(), gem5::Packet::headerDelay, gem5::ArmISA::i, isBusy, gem5::Packet::isRead(), gem5::Packet::isResponse(), gem5::Packet::isWrite(), gem5::Packet::needsResponse(), packetQueue, panic_if, gem5::Packet::payloadDelay, pendingDelete, recvAtomic(), releaseEvent, retryReq, retryResp, gem5::EventManager::schedule(), and gem5::Clocked::tick.

◆ release()

|

private |

Release the memory after being busy and send a retry if a request was rejected in the meanwhile.

Definition at line 201 of file simple_mem.cc.

References isBusy, port, and retryReq.

Referenced by SimpleMemory().

Member Data Documentation

◆ bandwidth

|

private |

Bandwidth in ticks per byte.

The regulation affects the acceptance rate of requests and the queueing takes place after the regulation.

Definition at line 134 of file simple_mem.hh.

Referenced by recvTimingReq(), and SimpleMemory().

◆ dequeueEvent

|

private |

Definition at line 170 of file simple_mem.hh.

Referenced by dequeue(), and recvTimingReq().

◆ isBusy

|

private |

Track the state of the memory as either idle or busy, no need for an enum with only two states.

Definition at line 140 of file simple_mem.hh.

Referenced by recvTimingReq(), release(), and SimpleMemory().

◆ latency

|

private |

Latency from that a request is accepted until the response is ready to be sent.

Definition at line 115 of file simple_mem.hh.

Referenced by getLatency(), recvAtomicBackdoor(), and SimpleMemory().

◆ latency_var

|

private |

Fudge factor added to the latency.

Definition at line 120 of file simple_mem.hh.

Referenced by getLatency(), and SimpleMemory().

◆ packetQueue

|

private |

Internal (unbounded) storage to mimic the delay caused by the actual memory access.

Note that this is where the packet spends the memory latency.

Definition at line 127 of file simple_mem.hh.

Referenced by dequeue(), drain(), recvFunctional(), and recvTimingReq().

◆ pendingDelete

|

private |

Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call.

Definition at line 183 of file simple_mem.hh.

Referenced by recvTimingReq().

◆ port

|

private |

Definition at line 109 of file simple_mem.hh.

Referenced by dequeue(), getPort(), init(), release(), and SimpleMemory().

◆ releaseEvent

|

private |

Definition at line 162 of file simple_mem.hh.

Referenced by recvTimingReq(), and SimpleMemory().

◆ retryReq

|

private |

Remember if we have to retry an outstanding request that arrived while we were busy.

Definition at line 146 of file simple_mem.hh.

Referenced by recvTimingReq(), release(), and SimpleMemory().

◆ retryResp

|

private |

Remember if we failed to send a response and are awaiting a retry.

This is only used as a check.

Definition at line 152 of file simple_mem.hh.

Referenced by dequeue(), recvRespRetry(), recvTimingReq(), and SimpleMemory().

◆ rng

|

mutableprivate |

Definition at line 154 of file simple_mem.hh.

Referenced by getLatency().

The documentation for this class was generated from the following files:

- mem/simple_mem.hh

- mem/simple_mem.cc

Generated on Sat Oct 18 2025 08:06:59 for gem5 by doxygen 1.14.0