gem5::Iris::CPU< TC > Class Template Reference

#include <cpu.hh>

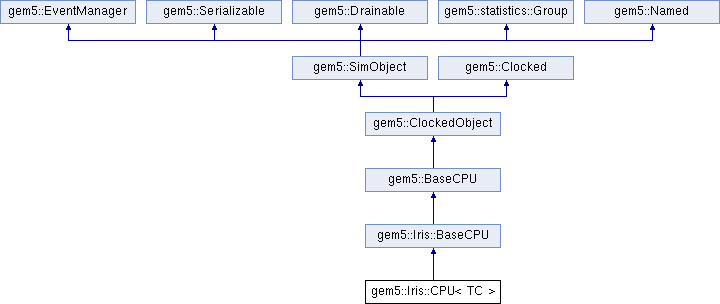

Inheritance diagram for gem5::Iris::CPU< TC >:

Public Member Functions | |

| CPU (const IrisBaseCPUParams ¶ms, iris::IrisConnectionInterface *iris_if) | |

| Public Member Functions inherited from gem5::Iris::BaseCPU | |

| BaseCPU (const BaseCPUParams ¶ms, sc_core::sc_module *_evs) | |

| virtual | ~BaseCPU () |

| Port & | getDataPort () override |

| Purely virtual method that returns a reference to the data port. | |

| Port & | getInstPort () override |

| Purely virtual method that returns a reference to the instruction port. | |

| void | wakeup (ThreadID tid) override |

| Counter | totalInsts () const override |

| Counter | totalOps () const override |

| virtual void | setResetAddr (Addr addr, bool secure=false) |

| Public Member Functions inherited from gem5::BaseCPU | |

| int | cpuId () const |

| Reads this CPU's ID. | |

| uint32_t | socketId () const |

| Reads this CPU's Socket ID. | |

| RequestorID | dataRequestorId () const |

| Reads this CPU's unique data requestor ID. | |

| RequestorID | instRequestorId () const |

| Reads this CPU's unique instruction requestor ID. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. | |

| uint32_t | taskId () const |

| Get cpu task id. | |

| void | taskId (uint32_t id) |

| Set cpu task id. | |

| uint32_t | getPid () const |

| void | setPid (uint32_t pid) |

| void | workItemBegin () |

| void | workItemEnd () |

| Tick | instCount () |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupts (ThreadID tid) |

| bool | checkInterrupts (ThreadID tid) const |

| trace::InstTracer * | getTracer () |

| Provide access to the tracer pointer. | |

| virtual void | activateContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now active. | |

| virtual void | suspendContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now suspended. | |

| virtual void | haltContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now halted. | |

| int | findContext (ThreadContext *tc) |

| Given a Thread Context pointer return the thread num. | |

| virtual ThreadContext * | getContext (int tn) |

| Given a thread num get tho thread context for it. | |

| unsigned | numContexts () |

| Get the number of thread contexts available. | |

| ThreadID | contextToThread (ContextID cid) |

| Convert ContextID to threadID. | |

| PARAMS (BaseCPU) | |

| BaseCPU (const Params ¶ms, bool is_checker=false) | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| void | startup () override |

| startup() is the final initialization call before simulation. | |

| void | regStats () override |

| Callback to set stat parameters. | |

| void | regProbePoints () override |

| Register probe points for this object. | |

| void | registerThreadContexts () |

| void | deschedulePowerGatingEvent () |

| void | schedulePowerGatingEvent () |

| virtual void | switchOut () |

| Prepare for another CPU to take over execution. | |

| virtual void | takeOverFrom (BaseCPU *cpu) |

| Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in. | |

| virtual void | setReset (bool state) |

| Set the reset of the CPU to be either asserted or deasserted. | |

| void | flushTLBs () |

| Flush all TLBs in the CPU. | |

| bool | switchedOut () const |

| Determine if the CPU is switched out. | |

| virtual void | verifyMemoryMode () const |

| Verify that the system is in a memory mode supported by the CPU. | |

| Addr | cacheLineSize () const |

| Get the cache line size of the system. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. | |

| virtual void | unserializeThread (CheckpointIn &cp, ThreadID tid) |

| Unserialize one thread. | |

| void | scheduleInstStop (ThreadID tid, Counter insts, std::string cause) |

| Schedule an event that exits the simulation loops after a predefined number of instructions. | |

| void | scheduleSimpointsInstStop (std::vector< Counter > inst_starts) |

| Schedule simpoint events using the scheduleInstStop function. | |

| void | scheduleInstStopAnyThread (Counter max_insts) |

| Schedule an exit event when any threads in the core reach the max_insts instructions using the scheduleInstStop function. | |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| Get the number of instructions executed by the specified thread on this CPU. | |

| void | traceFunctions (Addr pc) |

| void | armMonitor (ThreadID tid, Addr address) |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseMMU *mmu) |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| virtual void | htmSendAbortSignal (ThreadID tid, uint64_t htm_uid, HtmFailureFaultCause cause) |

| This function is used to instruct the memory subsystem that a transaction should be aborted and the speculative state should be thrown away. | |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| Helper method to trigger PMU probes for a committed instruction. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Additional Inherited Members | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::BaseCPU | |

| static int | numSimulatedCPUs () |

| static Counter | totalNumSimulatedInsts () |

| static Counter | totalNumSimulatedOps () |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::BaseCPU | |

| ThreadID | numThreads |

| Number of threads we're actually simulating (<= SMT_MAX_THREADS). | |

| System * | system |

| gem5::BaseCPU::BaseCPUStats | baseStats |

| Cycles | syscallRetryLatency |

| std::vector< std::unique_ptr< FetchCPUStats > > | fetchStats |

| std::vector< std::unique_ptr< ExecuteCPUStats > > | executeStats |

| std::vector< std::unique_ptr< CommitCPUStats > > | commitStats |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| Static Public Attributes inherited from gem5::BaseCPU | |

| static const uint32_t | invldPid = std::numeric_limits<uint32_t>::max() |

| Invalid or unknown Pid. | |

| Protected Types inherited from gem5::BaseCPU | |

| enum | CPUState { CPU_STATE_ON , CPU_STATE_SLEEP , CPU_STATE_WAKEUP } |

| Protected Member Functions inherited from gem5::Iris::BaseCPU | |

| void | clockPeriodUpdated () override |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

| void | serializeThread (CheckpointOut &cp, ThreadID tid) const override |

| Serialize a single thread. | |

| Protected Member Functions inherited from gem5::BaseCPU | |

| void | updateCycleCounters (CPUState state) |

| base method keeping track of cycle progression | |

| void | enterPwrGating () |

| probing::PMUUPtr | pmuProbePoint (const char *name) |

| Helper method to instantiate probe points belonging to this object. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| Protected Attributes inherited from gem5::Iris::BaseCPU | |

| sc_core::sc_module * | evs |

| Iris::BaseCpuEvs * | evs_base_cpu |

| friend | ThreadContext |

| Protected Attributes inherited from gem5::BaseCPU | |

| Tick | instCnt |

| Instruction count used for SPARC misc register. | |

| int | _cpuId |

| const uint32_t | _socketId |

| Each cpu will have a socket ID that corresponds to its physical location in the system. | |

| RequestorID | _instRequestorId |

| instruction side request id that must be placed in all requests | |

| RequestorID | _dataRequestorId |

| data side request id that must be placed in all requests | |

| uint32_t | _taskId |

| An intrenal representation of a task identifier within gem5. | |

| uint32_t | _pid |

| The current OS process ID that is executing on this processor. | |

| bool | _switchedOut |

| Is the CPU switched out or active? | |

| const Addr | _cacheLineSize |

| Cache the cache line size that we get from the system. | |

| SignalSinkPort< bool > | modelResetPort |

| std::vector< BaseInterrupts * > | interrupts |

| std::vector< ThreadContext * > | threadContexts |

| std::vector< std::unique_ptr< IntSourcePin< BaseCPU > > > | cpuIdlePins |

| trace::InstTracer * | tracer |

| Cycles | previousCycle |

| CPUState | previousState |

| const Cycles | pwrGatingLatency |

| const bool | powerGatingOnIdle |

| EventFunctionWrapper | enterPwrGatingEvent |

| probing::PMUUPtr | ppRetiredInsts |

| Instruction commit probe point. | |

| probing::PMUUPtr | ppRetiredInstsPC |

| probing::PMUUPtr | ppRetiredLoads |

| Retired load instructions. | |

| probing::PMUUPtr | ppRetiredStores |

| Retired store instructions. | |

| probing::PMUUPtr | ppRetiredBranches |

| Retired branches (any type) | |

| probing::PMUUPtr | ppAllCycles |

| CPU cycle counter even if any thread Context is suspended. | |

| probing::PMUUPtr | ppActiveCycles |

| CPU cycle counter, only counts if any thread contexts is active. | |

| ProbePointArg< bool > * | ppSleeping |

| ProbePoint that signals transitions of threadContexts sets. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

| Static Protected Attributes inherited from gem5::BaseCPU | |

| static std::unique_ptr< GlobalStats > | globalStats |

| Pointer to the global stat structure. | |

Detailed Description

Constructor & Destructor Documentation

◆ CPU()

template<class TC>

|

inline |

The documentation for this class was generated from the following file:

- arch/arm/fastmodel/iris/cpu.hh

Generated on Sat Oct 18 2025 08:06:59 for gem5 by doxygen 1.14.0