#include <vector.hh>

Public Member Functions | |

| VsSegIntrlvMicroInst (ExtMachInst extMachInst, uint32_t _micro_vl, uint32_t _dstReg, uint32_t _numSrcs, uint32_t _microIdx, uint32_t _numMicroops, uint32_t _field, uint32_t _elen, uint32_t _vlen, uint32_t _sizeOfElement) | |

| Fault | execute (ExecContext *, trace::InstRecord *) const override |

| std::string | generateDisassembly (Addr, const loader::SymbolTable *) const override |

| Internal function to generate disassembly string. | |

| Public Member Functions inherited from gem5::RiscvISA::RiscvStaticInst | |

| void | advancePC (PCStateBase &pc) const override |

| void | advancePC (ThreadContext *tc) const override |

| uint64_t | getEMI () const override |

| std::unique_ptr< PCStateBase > | buildRetPC (const PCStateBase &cur_pc, const PCStateBase &call_pc) const override |

| size_t | asBytes (void *buf, size_t size) override |

| Instruction classes can override this function to return a a representation of themselves as a blob of bytes, generally assumed to be that instructions ExtMachInst. | |

| Public Member Functions inherited from gem5::StaticInst | |

| uint8_t | numSrcRegs () const |

| Number of source registers. | |

| uint8_t | numDestRegs () const |

| Number of destination registers. | |

| uint8_t | numDestRegs (RegClassType type) const |

| Number of destination registers of a particular type. | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isMatrix () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isFullMemBarrier () const |

| bool | isReadBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isUnverifiable () const |

| bool | isPseudo () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isInvalid () const |

| bool | isHtmCmd () const |

| void | setFirstMicroop () |

| void | setLastMicroop () |

| void | setDelayedCommit () |

| void | setFlag (Flags f) |

| OpClass | opClass () const |

| Operation class. Used to select appropriate function unit in issue. | |

| const RegId & | destRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th destination reg. | |

| void | setDestRegIdx (int i, const RegId &val) |

| const RegId & | srcRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th source reg. | |

| void | setSrcRegIdx (int i, const RegId &val) |

| virtual | ~StaticInst () |

| virtual Fault | initiateAcc (ExecContext *xc, trace::InstRecord *traceData) const |

| virtual Fault | completeAcc (Packet *pkt, ExecContext *xc, trace::InstRecord *trace_data) const |

| size_t | size () const |

| virtual void | size (size_t newSize) |

| virtual StaticInstPtr | fetchMicroop (MicroPC upc) const |

| Return the microop that goes with a particular micropc. | |

| virtual std::unique_ptr< PCStateBase > | branchTarget (const PCStateBase &pc) const |

| Return the target address for a PC-relative branch. | |

| virtual std::unique_ptr< PCStateBase > | branchTarget (ThreadContext *tc) const |

| Return the target address for an indirect branch (jump). | |

| virtual const std::string & | disassemble (Addr pc, const loader::SymbolTable *symtab=nullptr) const |

| Return string representation of disassembled instruction. | |

| void | printFlags (std::ostream &outs, const std::string &separator) const |

| Print a separator separated list of this instruction's set flag names on the given stream. | |

| std::string | getName () |

| Return name of machine instruction. | |

| Public Member Functions inherited from gem5::RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. | |

| void | incref () const |

| Increment the reference count. | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. | |

Private Attributes | |

| RegId | srcRegIdxArr [NumVecInternalRegs] |

| RegId | destRegIdxArr [1] |

| uint32_t | numSrcs |

| uint32_t | numMicroops |

| uint32_t | field |

| uint32_t | sizeOfElement |

| uint32_t | micro_vl |

Additional Inherited Members | |

| Public Types inherited from gem5::StaticInst | |

| using | RegIdArrayPtr = RegId (StaticInst:: *)[] |

| Public Attributes inherited from gem5::RiscvISA::RiscvStaticInst | |

| ExtMachInst | machInst |

| static StaticInstPtr | nullStaticInstPtr |

| Pointer to a statically allocated "null" instruction object. | |

| Protected Member Functions inherited from gem5::RiscvISA::VectorArithMicroInst | |

| VectorArithMicroInst (const char *mnem, ExtMachInst _machInst, OpClass __opClass, uint32_t _microVl, uint32_t _microIdx, uint32_t _elen, uint32_t _vlen) | |

| Protected Member Functions inherited from gem5::RiscvISA::VectorMicroInst | |

| VectorMicroInst (const char *mnem, ExtMachInst _machInst, OpClass __opClass, uint32_t _microVl, uint32_t _microIdx, uint32_t _elen, uint32_t _vlen) | |

| Protected Member Functions inherited from gem5::RiscvISA::RiscvMicroInst | |

| RiscvMicroInst (const char *mnem, ExtMachInst _machInst, OpClass __opClass) | |

| void | advancePC (PCStateBase &pcState) const override |

| void | advancePC (ThreadContext *tc) const override |

| Protected Member Functions inherited from gem5::RiscvISA::RiscvStaticInst | |

| RiscvStaticInst (const char *_mnemonic, ExtMachInst _machInst, OpClass __opClass) | |

| template<typename T> | |

| T | rvSelect (T v32, T v64) const |

| template<typename T32, typename T64> | |

| T64 | rvExt (T64 x) const |

| uint64_t | rvZext (uint64_t x) const |

| int64_t | rvSext (int64_t x) const |

| void | setRegIdxArrays (RegIdArrayPtr src, RegIdArrayPtr dest) |

| Set the pointers which point to the arrays of source and destination register indices. | |

| StaticInst (const char *_mnemonic, OpClass op_class) | |

| Constructor. | |

| template<typename T> | |

| size_t | simpleAsBytes (void *buf, size_t max_size, const T &t) |

| Protected Attributes inherited from gem5::RiscvISA::VectorMicroInst | |

| uint32_t | microVl |

| uint32_t | microIdx |

| uint8_t | vtype |

| uint32_t | elen |

| uint32_t | vlen |

| int | oldDstIdx = -1 |

| int | vmsrcIdx = -1 |

| const uint8_t | vsew |

| const int8_t | vlmul |

| const uint32_t | sew |

| const float | vflmul |

| Protected Attributes inherited from gem5::StaticInst | |

| std::bitset< Num_Flags > | flags |

| Flag values for this instruction. | |

| OpClass | _opClass |

| See opClass(). | |

| uint8_t | _numSrcRegs = 0 |

| See numSrcRegs(). | |

| uint8_t | _numDestRegs = 0 |

| See numDestRegs(). | |

| std::array< uint8_t, MiscRegClass+1 > | _numTypedDestRegs = {} |

| size_t | _size = 0 |

| Instruction size in bytes. | |

| const char * | mnemonic |

| Base mnemonic (e.g., "add"). | |

| std::unique_ptr< std::string > | cachedDisassembly |

| String representation of disassembly (lazily evaluated via disassemble()). | |

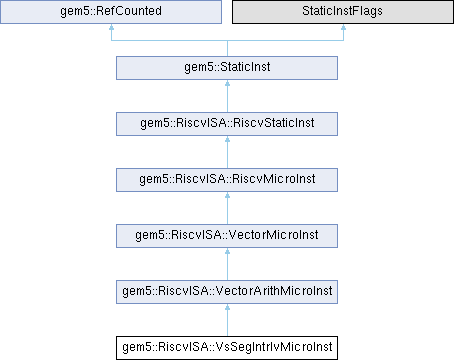

Detailed Description

Constructor & Destructor Documentation

◆ VsSegIntrlvMicroInst()

| gem5::RiscvISA::VsSegIntrlvMicroInst::VsSegIntrlvMicroInst | ( | ExtMachInst | extMachInst, |

| uint32_t | _micro_vl, | ||

| uint32_t | _dstReg, | ||

| uint32_t | _numSrcs, | ||

| uint32_t | _microIdx, | ||

| uint32_t | _numMicroops, | ||

| uint32_t | _field, | ||

| uint32_t | _elen, | ||

| uint32_t | _vlen, | ||

| uint32_t | _sizeOfElement ) |

Definition at line 757 of file vector.cc.

References gem5::StaticInst::_numDestRegs, gem5::StaticInst::_numSrcRegs, gem5::StaticInst::_numTypedDestRegs, destRegIdxArr, field, gem5::RiscvISA::i, micro_vl, gem5::RiscvISA::VectorMicroInst::microIdx, numMicroops, numSrcs, gem5::StaticInst::setDestRegIdx(), gem5::StaticInst::setRegIdxArrays(), gem5::StaticInst::setSrcRegIdx(), gem5::SimdAddOp, sizeOfElement, srcRegIdxArr, gem5::RiscvISA::VecMemInternalReg0, gem5::VecRegClass, gem5::RiscvISA::vecRegClass, and gem5::RiscvISA::VectorArithMicroInst::VectorArithMicroInst().

Member Function Documentation

◆ execute()

|

overridevirtual |

Implements gem5::StaticInst.

Definition at line 791 of file vector.cc.

References gem5::VecRegContainer< SIZE >::as(), field, gem5::ExecContext::getRegOperand(), gem5::ExecContext::getWritableRegOperand(), micro_vl, gem5::NoFault, numSrcs, gem5::RiscvISA::s, gem5::trace::InstRecord::setData(), sizeOfElement, and gem5::RiscvISA::vecRegClass.

◆ generateDisassembly()

|

overridevirtual |

Internal function to generate disassembly string.

Reimplemented from gem5::RiscvISA::VectorArithMicroInst.

Definition at line 830 of file vector.cc.

References gem5::StaticInst::_numSrcRegs, gem5::StaticInst::destRegIdx(), field, gem5::RiscvISA::i, gem5::StaticInst::mnemonic, gem5::RiscvISA::pc, gem5::RiscvISA::registerName(), gem5::StaticInst::srcRegIdx(), and gem5::RiscvISA::ss.

Member Data Documentation

◆ destRegIdxArr

|

private |

Definition at line 774 of file vector.hh.

Referenced by VsSegIntrlvMicroInst().

◆ field

|

private |

Definition at line 777 of file vector.hh.

Referenced by execute(), generateDisassembly(), and VsSegIntrlvMicroInst().

◆ micro_vl

|

private |

Definition at line 779 of file vector.hh.

Referenced by execute(), and VsSegIntrlvMicroInst().

◆ numMicroops

|

private |

Definition at line 776 of file vector.hh.

Referenced by VsSegIntrlvMicroInst().

◆ numSrcs

|

private |

Definition at line 775 of file vector.hh.

Referenced by execute(), and VsSegIntrlvMicroInst().

◆ sizeOfElement

|

private |

Definition at line 778 of file vector.hh.

Referenced by execute(), and VsSegIntrlvMicroInst().

◆ srcRegIdxArr

|

private |

Definition at line 773 of file vector.hh.

Referenced by VsSegIntrlvMicroInst().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:07:02 for gem5 by doxygen 1.14.0