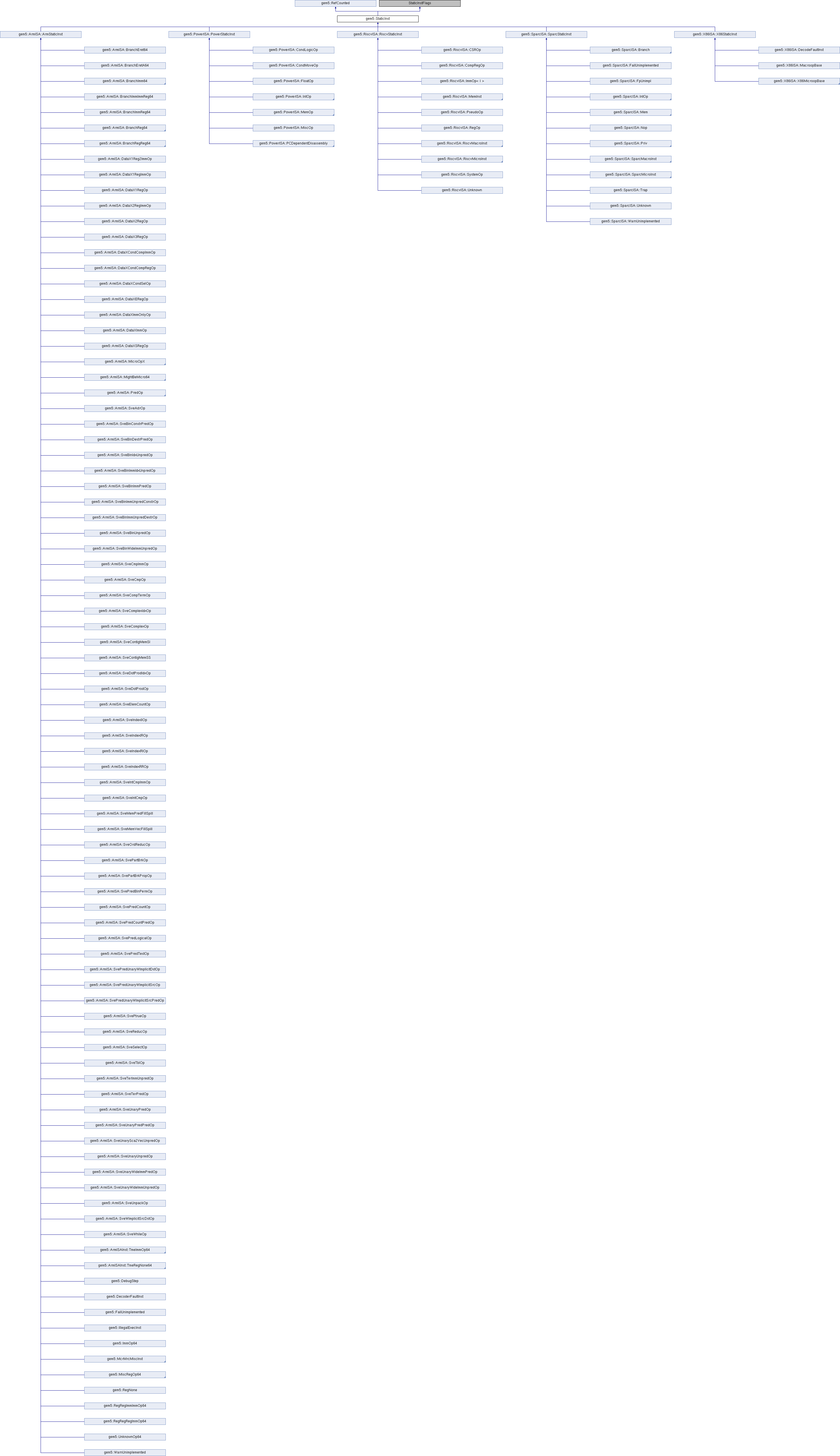

Base, ISA-independent static instruction class. More...

#include <static_inst.hh>

Public Types | |

| using | RegIdArrayPtr = RegId (StaticInst:: *)[] |

Public Member Functions | |

Register information. | |

The sum of the different numDestRegs([type])-s equals numDestRegs(). The per-type function is used to track physical register usage. | |

| uint8_t | numSrcRegs () const |

| Number of source registers. | |

| uint8_t | numDestRegs () const |

| Number of destination registers. | |

| uint8_t | numDestRegs (RegClassType type) const |

| Number of destination registers of a particular type. | |

| Public Member Functions inherited from gem5::RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. | |

| void | incref () const |

| Increment the reference count. | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. | |

Protected Attributes | |

| std::bitset< Num_Flags > | flags |

| Flag values for this instruction. | |

| OpClass | _opClass |

| See opClass(). | |

| uint8_t | _numSrcRegs = 0 |

| See numSrcRegs(). | |

| uint8_t | _numDestRegs = 0 |

| See numDestRegs(). | |

| std::array< uint8_t, MiscRegClass+1 > | _numTypedDestRegs = {} |

Private Attributes | |

| RegIdArrayPtr | _srcRegIdxPtr = nullptr |

| See srcRegIdx(). | |

| RegIdArrayPtr | _destRegIdxPtr = nullptr |

| See destRegIdx(). | |

Flag accessors. | |

These functions are used to access the values of the various instruction property flags. See StaticInst::Flags for descriptions of the individual flags. | |

| size_t | _size = 0 |

| Instruction size in bytes. | |

| const char * | mnemonic |

| Base mnemonic (e.g., "add"). | |

| std::unique_ptr< std::string > | cachedDisassembly |

| String representation of disassembly (lazily evaluated via disassemble()). | |

| static StaticInstPtr | nullStaticInstPtr |

| Pointer to a statically allocated "null" instruction object. | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isMatrix () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isFullMemBarrier () const |

| bool | isReadBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isUnverifiable () const |

| bool | isPseudo () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isInvalid () const |

| bool | isHtmCmd () const |

| void | setFirstMicroop () |

| void | setLastMicroop () |

| void | setDelayedCommit () |

| void | setFlag (Flags f) |

| OpClass | opClass () const |

| Operation class. Used to select appropriate function unit in issue. | |

| const RegId & | destRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th destination reg. | |

| void | setDestRegIdx (int i, const RegId &val) |

| const RegId & | srcRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th source reg. | |

| void | setSrcRegIdx (int i, const RegId &val) |

| virtual uint64_t | getEMI () const |

| virtual | ~StaticInst () |

| virtual Fault | execute (ExecContext *xc, trace::InstRecord *traceData) const =0 |

| virtual Fault | initiateAcc (ExecContext *xc, trace::InstRecord *traceData) const |

| virtual Fault | completeAcc (Packet *pkt, ExecContext *xc, trace::InstRecord *trace_data) const |

| virtual void | advancePC (PCStateBase &pc_state) const =0 |

| virtual void | advancePC (ThreadContext *tc) const |

| virtual std::unique_ptr< PCStateBase > | buildRetPC (const PCStateBase &cur_pc, const PCStateBase &call_pc) const |

| size_t | size () const |

| virtual void | size (size_t newSize) |

| virtual StaticInstPtr | fetchMicroop (MicroPC upc) const |

| Return the microop that goes with a particular micropc. | |

| virtual std::unique_ptr< PCStateBase > | branchTarget (const PCStateBase &pc) const |

| Return the target address for a PC-relative branch. | |

| virtual std::unique_ptr< PCStateBase > | branchTarget (ThreadContext *tc) const |

| Return the target address for an indirect branch (jump). | |

| virtual const std::string & | disassemble (Addr pc, const loader::SymbolTable *symtab=nullptr) const |

| Return string representation of disassembled instruction. | |

| void | printFlags (std::ostream &outs, const std::string &separator) const |

| Print a separator separated list of this instruction's set flag names on the given stream. | |

| std::string | getName () |

| Return name of machine instruction. | |

| virtual size_t | asBytes (void *buf, size_t max_size) |

| Instruction classes can override this function to return a a representation of themselves as a blob of bytes, generally assumed to be that instructions ExtMachInst. | |

| void | setRegIdxArrays (RegIdArrayPtr src, RegIdArrayPtr dest) |

| Set the pointers which point to the arrays of source and destination register indices. | |

| virtual std::string | generateDisassembly (Addr pc, const loader::SymbolTable *symtab) const =0 |

| Internal function to generate disassembly string. | |

| StaticInst (const char *_mnemonic, OpClass op_class) | |

| Constructor. | |

| template<typename T> | |

| size_t | simpleAsBytes (void *buf, size_t max_size, const T &t) |

Detailed Description

Base, ISA-independent static instruction class.

The main component of this class is the vector of flags and the associated methods for reading them. Any object that can rely solely on these flags can process instructions without being recompiled for multiple ISAs.

Definition at line 88 of file static_inst.hh.

Member Typedef Documentation

◆ RegIdArrayPtr

| using gem5::StaticInst::RegIdArrayPtr = RegId (StaticInst:: *)[] |

Definition at line 91 of file static_inst.hh.

Constructor & Destructor Documentation

◆ StaticInst()

|

inlineprotected |

Constructor.

It's important to initialize everything here to a sane default, since the decoder generally only overrides the fields that are meaningful for the particular instruction.

Definition at line 287 of file static_inst.hh.

References _opClass, and mnemonic.

Referenced by gem5::ArmISA::ArmStaticInst::ArmStaticInst(), gem5::PowerISA::PowerStaticInst::PowerStaticInst(), gem5::RiscvISA::RiscvStaticInst::RiscvStaticInst(), gem5::SparcISA::SparcStaticInst::SparcStaticInst(), and gem5::X86ISA::X86StaticInst::X86StaticInst().

◆ ~StaticInst()

|

inlinevirtual |

Definition at line 292 of file static_inst.hh.

Member Function Documentation

◆ advancePC() [1/2]

|

pure virtual |

Implemented in gem5::ArmISA::ArmStaticInst, gem5::ArmISA::FpOp, gem5::ArmISA::MicroOp, gem5::ArmISA::MicroOpX, gem5::ArmISA::MightBeMicro64, gem5::ArmISA::MightBeMicro, gem5::ArmISA::PredMicroop, gem5::PowerISA::PowerStaticInst, gem5::RiscvISA::RiscvMicroInst, gem5::RiscvISA::RiscvStaticInst, gem5::SparcISA::SparcMicroInst, gem5::SparcISA::SparcStaticInst, gem5::X86ISA::X86MicroopBase, and gem5::X86ISA::X86StaticInst.

Referenced by gem5::GenericISA::M5DebugFault::advancePC(), advancePC(), gem5::minor::Decode::evaluate(), gem5::minor::Fetch2::evaluate(), gem5::ArmISA::SupervisorCall::invoke(), gem5::SESyscallFault::invoke(), gem5::RiscvISA::SyscallFault::invokeSE(), and gem5::branch_prediction::BPredUnit::predict().

◆ advancePC() [2/2]

|

virtual |

Reimplemented in gem5::ArmISA::ArmStaticInst, gem5::ArmISA::FpOp, gem5::ArmISA::MicroOp, gem5::ArmISA::MicroOpX, gem5::ArmISA::MightBeMicro64, gem5::ArmISA::MightBeMicro, gem5::ArmISA::PredMicroop, gem5::PowerISA::PowerStaticInst, gem5::RiscvISA::RiscvMicroInst, gem5::RiscvISA::RiscvStaticInst, gem5::SparcISA::SparcMicroInst, gem5::SparcISA::SparcStaticInst, gem5::X86ISA::X86MicroopBase, and gem5::X86ISA::X86StaticInst.

Definition at line 88 of file static_inst.cc.

References advancePC(), gem5::PCStateBase::clone(), gem5::MipsISA::pc, and gem5::ThreadContext::pcState().

◆ asBytes()

|

inlinevirtual |

Instruction classes can override this function to return a a representation of themselves as a blob of bytes, generally assumed to be that instructions ExtMachInst.

buf is a buffer to hold the bytes. max_size is the size allocated for that buffer by the caller. The return value is how much data was actually put into the buffer, zero if no data was put in the buffer, or the necessary size of the buffer if there wasn't enough space.

Reimplemented in gem5::ArmISA::ArmStaticInst, gem5::PowerISA::PowerStaticInst, gem5::RiscvISA::RiscvStaticInst, and gem5::SparcISA::SparcStaticInst.

Definition at line 396 of file static_inst.hh.

◆ branchTarget() [1/2]

|

virtual |

Return the target address for a PC-relative branch.

Invalid if not a PC-relative branch (i.e. isDirectCtrl() should be true).

Reimplemented in gem5::ArmISA::BranchImm64, gem5::ArmISA::BranchImmImmReg64, gem5::ArmISA::BranchImmReg64, gem5::PowerISA::BranchDispCondOp, gem5::PowerISA::BranchOp, gem5::PowerISA::BranchRegCondOp, gem5::RiscvISA::ZcmtSecondFetchInst, and gem5::X86ISA::X86MicroopBase.

Definition at line 46 of file static_inst.cc.

References panic, and gem5::MipsISA::pc.

◆ branchTarget() [2/2]

|

virtual |

Return the target address for an indirect branch (jump).

The register value is read from the supplied thread context, so the result is valid only if the thread context is about to execute the branch in question. Invalid if not an indirect branch (i.e. isIndirectCtrl() should be true).

Reimplemented in gem5::ArmISA::BranchImm64, gem5::ArmISA::BranchImmImmReg64, gem5::ArmISA::BranchImmReg64, gem5::PowerISA::BranchDispCondOp, gem5::PowerISA::BranchOp, gem5::PowerISA::BranchRegCondOp, gem5::RiscvISA::VlFFTrimVlMicroOp, gem5::RiscvISA::ZcmtSecondFetchInst, and gem5::X86ISA::X86MicroopBase.

Definition at line 53 of file static_inst.cc.

References panic.

◆ buildRetPC()

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ArmStaticInst, gem5::PowerISA::PowerStaticInst, gem5::RiscvISA::RiscvStaticInst, gem5::SparcISA::SparcStaticInst, and gem5::X86ISA::X86StaticInst.

Definition at line 314 of file static_inst.hh.

References panic.

Referenced by gem5::branch_prediction::BPredUnit::predict(), and gem5::branch_prediction::BPredUnit::squash().

◆ completeAcc()

|

inlinevirtual |

Definition at line 304 of file static_inst.hh.

References panic.

◆ destRegIdx()

|

inline |

Return logical index (architectural reg num) of i'th destination reg.

Only the entries from 0 through numDestRegs()-1 are valid.

Definition at line 219 of file static_inst.hh.

References gem5::ArmISA::i.

Referenced by gem5::PowerISA::FloatOp::generateDisassembly(), gem5::PowerISA::IntArithOp::generateDisassembly(), gem5::PowerISA::IntConcatRotateOp::generateDisassembly(), gem5::PowerISA::IntConcatShiftOp::generateDisassembly(), gem5::PowerISA::IntDispArithOp::generateDisassembly(), gem5::PowerISA::IntImmArithOp::generateDisassembly(), gem5::PowerISA::IntImmLogicOp::generateDisassembly(), gem5::PowerISA::IntImmOp::generateDisassembly(), gem5::PowerISA::IntLogicOp::generateDisassembly(), gem5::PowerISA::IntOp::generateDisassembly(), gem5::PowerISA::IntRotateOp::generateDisassembly(), gem5::PowerISA::IntShiftOp::generateDisassembly(), gem5::PowerISA::MemDispOp::generateDisassembly(), gem5::PowerISA::MemDispShiftOp::generateDisassembly(), gem5::PowerISA::MemIndexOp::generateDisassembly(), gem5::PowerISA::MiscOp::generateDisassembly(), gem5::RiscvISA::AtomicMemOpMicro::generateDisassembly(), gem5::RiscvISA::BSOp::generateDisassembly(), gem5::RiscvISA::CompRegOp::generateDisassembly(), gem5::RiscvISA::CSROp::generateDisassembly(), gem5::RiscvISA::Load::generateDisassembly(), gem5::RiscvISA::LoadReservedMicro::generateDisassembly(), gem5::RiscvISA::RegOp::generateDisassembly(), gem5::RiscvISA::StoreCondMicro::generateDisassembly(), gem5::RiscvISA::VConfOp::generateDisassembly(), gem5::RiscvISA::VCpyVsMicroInst::generateDisassembly(), gem5::RiscvISA::VectorArithMacroInst::generateDisassembly(), gem5::RiscvISA::VectorArithMicroInst::generateDisassembly(), gem5::RiscvISA::VectorNonSplitInst::generateDisassembly(), gem5::RiscvISA::VectorSlideMacroInst::generateDisassembly(), gem5::RiscvISA::VectorSlideMicroInst::generateDisassembly(), gem5::RiscvISA::VectorVMUNARY0MacroInst::generateDisassembly(), gem5::RiscvISA::VectorVMUNARY0MicroInst::generateDisassembly(), gem5::RiscvISA::VlElementMacroInst::generateDisassembly(), gem5::RiscvISA::VlElementMicroInst::generateDisassembly(), gem5::RiscvISA::VleMacroInst::generateDisassembly(), gem5::RiscvISA::VleMicroInst::generateDisassembly(), gem5::RiscvISA::VlIndexMacroInst::generateDisassembly(), gem5::RiscvISA::VlIndexMicroInst::generateDisassembly(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::generateDisassembly(), gem5::RiscvISA::VlSegMacroInst::generateDisassembly(), gem5::RiscvISA::VlSegMicroInst::generateDisassembly(), gem5::RiscvISA::VlWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VlWholeMicroInst::generateDisassembly(), gem5::RiscvISA::VMaskMergeMicroInst::generateDisassembly(), gem5::RiscvISA::VMvWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VMvWholeMicroInst::generateDisassembly(), gem5::RiscvISA::VPinVdMicroInst::generateDisassembly(), gem5::RiscvISA::VsSegIntrlvMicroInst::generateDisassembly(), gem5::RiscvISA::VsSegMacroInst::generateDisassembly(), gem5::RiscvISA::VsSegMicroInst::generateDisassembly(), gem5::SparcISA::BlockMemImmMicro::generateDisassembly(), gem5::SparcISA::BlockMemMicro::generateDisassembly(), gem5::SparcISA::Mem::generateDisassembly(), gem5::SparcISA::MemImm::generateDisassembly(), gem5::SparcISA::SparcStaticInst::generateDisassembly(), gem5::minor::Scoreboard::markupInstDests(), gem5::SparcISA::SparcStaticInst::printDestReg(), gem5::MsrBase::printMsrBase(), and gem5::RiscvISA::VPinVdMicroInst::VPinVdMicroInst().

◆ disassemble()

|

virtual |

Return string representation of disassembled instruction.

The default version of this function will call the internal virtual generateDisassembly() function to get the string, then cache it in cachedDisassembly. If the disassembly should not be cached, this function should be overridden directly.

Reimplemented in gem5::PowerISA::PCDependentDisassembly.

Definition at line 60 of file static_inst.cc.

References cachedDisassembly, generateDisassembly(), and gem5::MipsISA::pc.

Referenced by gem5::minor::Scoreboard::canInstIssue(), gem5::trace::InstDisassembler::disassemble(), gem5::minor::FUPipeline::findTiming(), and gem5::X86ISA::PageFault::invoke().

◆ execute()

|

pure virtual |

Implemented in gem5::ArmISA::PredMacroOp, gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >, gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >, gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >, gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >, gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >, gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >, gem5::ArmISAInst::MicroTcommit64, gem5::ArmISAInst::MicroTfence64, gem5::ArmISAInst::Tcancel64, gem5::ArmISAInst::Tstart64, gem5::ArmISAInst::Ttest64, gem5::DebugStep, gem5::DecoderFaultInst, gem5::FailUnimplemented, gem5::IllegalExecInst, gem5::McrMrcImplDefined, gem5::McrMrcMiscInst, gem5::MiscRegImplDefined64, gem5::RiscvISA::MemFenceMicro, gem5::RiscvISA::RiscvMacroInst, gem5::RiscvISA::Unknown, gem5::RiscvISA::VCpyVsMicroInst, gem5::RiscvISA::VectorNopMicroInst, gem5::RiscvISA::VlFFTrimVlMicroOp, gem5::RiscvISA::VlSegDeIntrlvMicroInst, gem5::RiscvISA::VMaskMergeMicroInst, gem5::RiscvISA::VPinVdMicroInst, gem5::RiscvISA::VsSegIntrlvMicroInst, gem5::RiscvISA::VxsatMicroInst, gem5::RiscvISA::ZcmtSecondFetchInst, gem5::SparcISA::FailUnimplemented, gem5::SparcISA::Nop, gem5::SparcISA::SparcMacroInst, gem5::SparcISA::Unknown, gem5::SparcISA::WarnUnimplemented, gem5::WarnUnimplemented, gem5::X86ISA::DecodeFaultInst, gem5::X86ISA::MicroDebug, and gem5::X86ISA::MicroHalt.

◆ fetchMicroop()

|

virtual |

Return the microop that goes with a particular micropc.

This should only be defined/used in macroops which will contain microops

Reimplemented in gem5::ArmISA::Memory64, gem5::ArmISA::Memory, gem5::ArmISA::PredMacroOp, gem5::ArmISA::RfeOp, gem5::ArmISA::SrsOp, gem5::RiscvISA::RiscvMacroInst, gem5::SparcISA::SparcMacroInst, and gem5::X86ISA::MacroopBase.

Definition at line 39 of file static_inst.cc.

References panic.

Referenced by gem5::minor::Decode::evaluate(), gem5::o3::Fetch::fetch(), and gem5::Checker< DynInstPtr >::verify().

◆ generateDisassembly()

|

protectedpure virtual |

Internal function to generate disassembly string.

Implemented in gem5::ArmISA::ArmStaticInst, gem5::ArmISA::BranchEret64, gem5::ArmISA::BranchEretA64, gem5::ArmISA::BranchImm64, gem5::ArmISA::BranchImm, gem5::ArmISA::BranchImmCond64, gem5::ArmISA::BranchImmImmReg64, gem5::ArmISA::BranchImmReg64, gem5::ArmISA::BranchReg64, gem5::ArmISA::BranchReg, gem5::ArmISA::BranchRegReg64, gem5::ArmISA::BranchRegReg, gem5::ArmISA::BranchRet64, gem5::ArmISA::BranchRetA64, gem5::ArmISA::DataImmOp, gem5::ArmISA::DataRegOp, gem5::ArmISA::DataRegRegOp, gem5::ArmISA::DataX1Reg2ImmOp, gem5::ArmISA::DataX1RegImmOp, gem5::ArmISA::DataX1RegOp, gem5::ArmISA::DataX2RegImmOp, gem5::ArmISA::DataX2RegOp, gem5::ArmISA::DataX3RegOp, gem5::ArmISA::DataXCondCompImmOp, gem5::ArmISA::DataXCondCompRegOp, gem5::ArmISA::DataXCondSelOp, gem5::ArmISA::DataXERegOp, gem5::ArmISA::DataXImmOnlyOp, gem5::ArmISA::DataXImmOp, gem5::ArmISA::DataXSRegOp, gem5::ArmISA::FpCondCompRegOp, gem5::ArmISA::FpCondSelOp, gem5::ArmISA::FpRegImmOp, gem5::ArmISA::FpRegRegImmOp, gem5::ArmISA::FpRegRegOp, gem5::ArmISA::FpRegRegRegCondOp, gem5::ArmISA::FpRegRegRegImmOp, gem5::ArmISA::FpRegRegRegOp, gem5::ArmISA::FpRegRegRegRegOp, gem5::ArmISA::MemoryAtomicPair64, gem5::ArmISA::MemoryDImm64, gem5::ArmISA::MemoryDImmEx64, gem5::ArmISA::MemoryEx64, gem5::ArmISA::MemoryImm64, gem5::ArmISA::MemoryLiteral64, gem5::ArmISA::MemoryPostIndex64, gem5::ArmISA::MemoryPreIndex64, gem5::ArmISA::MemoryRaw64, gem5::ArmISA::MemoryReg64, gem5::ArmISA::MicroIntImmOp, gem5::ArmISA::MicroIntImmXOp, gem5::ArmISA::MicroIntMov, gem5::ArmISA::MicroIntOp, gem5::ArmISA::MicroIntRegXOp, gem5::ArmISA::MicroMemOp, gem5::ArmISA::MicroMemPairOp, gem5::ArmISA::MicroSetPCCPSR, gem5::ArmISA::PredImmOp, gem5::ArmISA::PredIntOp, gem5::ArmISA::PredMacroOp, gem5::ArmISA::RfeOp, gem5::ArmISA::SmeAddOp, gem5::ArmISA::SmeAddVlOp, gem5::ArmISA::SmeLd1xSt1xOp, gem5::ArmISA::SmeLdrStrOp, gem5::ArmISA::SmeMovExtractOp, gem5::ArmISA::SmeMovInsertOp, gem5::ArmISA::SmeOPOp, gem5::ArmISA::SmeRdsvlOp, gem5::ArmISA::SmeZeroOp, gem5::ArmISA::SrsOp, gem5::ArmISA::SveAdrOp, gem5::ArmISA::SveBinConstrPredOp, gem5::ArmISA::SveBinDestrPredOp, gem5::ArmISA::SveBinIdxUnpredOp, gem5::ArmISA::SveBinImmIdxUnpredOp, gem5::ArmISA::SveBinImmPredOp, gem5::ArmISA::SveBinImmUnpredConstrOp, gem5::ArmISA::SveBinImmUnpredDestrOp, gem5::ArmISA::SveBinUnpredOp, gem5::ArmISA::SveBinWideImmUnpredOp, gem5::ArmISA::SveClampOp, gem5::ArmISA::SveCmpImmOp, gem5::ArmISA::SveCmpOp, gem5::ArmISA::SveComplexIdxOp, gem5::ArmISA::SveComplexOp, gem5::ArmISA::SveCompTermOp, gem5::ArmISA::SveContigMemSI, gem5::ArmISA::SveContigMemSS, gem5::ArmISA::SveDotProdIdxOp, gem5::ArmISA::SveDotProdOp, gem5::ArmISA::SveElemCountOp, gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >, gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >, gem5::ArmISA::SveIndexIIOp, gem5::ArmISA::SveIndexIROp, gem5::ArmISA::SveIndexRIOp, gem5::ArmISA::SveIndexRROp, gem5::ArmISA::SveIntCmpImmOp, gem5::ArmISA::SveIntCmpOp, gem5::ArmISA::SveLdStructSI< Element, MicroopLdMemType, MicroopDeIntrlvType >, gem5::ArmISA::SveLdStructSS< Element, MicroopLdMemType, MicroopDeIntrlvType >, gem5::ArmISA::SveMemPredFillSpill, gem5::ArmISA::SveMemVecFillSpill, gem5::ArmISA::SveOrdReducOp, gem5::ArmISA::SvePartBrkOp, gem5::ArmISA::SvePartBrkPropOp, gem5::ArmISA::SvePredBinPermOp, gem5::ArmISA::SvePredCountOp, gem5::ArmISA::SvePredCountPredOp, gem5::ArmISA::SvePredLogicalOp, gem5::ArmISA::SvePredTestOp, gem5::ArmISA::SvePredUnaryWImplicitDstOp, gem5::ArmISA::SvePredUnaryWImplicitSrcOp, gem5::ArmISA::SvePredUnaryWImplicitSrcPredOp, gem5::ArmISA::SvePselOp, gem5::ArmISA::SvePtrueOp, gem5::ArmISA::SveReducOp, gem5::ArmISA::SveSelectOp, gem5::ArmISA::SveStStructSI< Element, MicroopStMemType, MicroopIntrlvType >, gem5::ArmISA::SveStStructSS< Element, MicroopStMemType, MicroopIntrlvType >, gem5::ArmISA::SveTblOp, gem5::ArmISA::SveTerImmUnpredOp, gem5::ArmISA::SveTerPredOp, gem5::ArmISA::SveTerUnpredOp, gem5::ArmISA::SveUnaryPredOp, gem5::ArmISA::SveUnaryPredPredOp, gem5::ArmISA::SveUnarySca2VecUnpredOp, gem5::ArmISA::SveUnaryUnpredOp, gem5::ArmISA::SveUnaryWideImmPredOp, gem5::ArmISA::SveUnaryWideImmUnpredOp, gem5::ArmISA::SveUnpackOp, gem5::ArmISA::SveWhileOp, gem5::ArmISA::SveWImplicitSrcDstOp, gem5::ArmISA::SysDC64, gem5::ArmISAInst::MicroTmeBasic64, gem5::ArmISAInst::TmeImmOp64, gem5::ArmISAInst::TmeRegNone64, gem5::DecoderFaultInst, gem5::FailUnimplemented, gem5::ImmOp64, gem5::ImmOp, gem5::McrMrcImplDefined, gem5::McrMrcMiscInst, gem5::McrrOp, gem5::MiscRegImmOp64, gem5::MiscRegImplDefined64, gem5::MiscRegRegImmOp64, gem5::MiscRegRegImmOp, gem5::MrrcOp, gem5::MrsOp, gem5::MsrImmOp, gem5::MsrRegOp, gem5::PowerISA::BranchDispCondOp, gem5::PowerISA::BranchOp, gem5::PowerISA::BranchRegCondOp, gem5::PowerISA::CondLogicOp, gem5::PowerISA::CondMoveOp, gem5::PowerISA::FloatOp, gem5::PowerISA::IntArithOp, gem5::PowerISA::IntCompOp, gem5::PowerISA::IntConcatRotateOp, gem5::PowerISA::IntConcatShiftOp, gem5::PowerISA::IntDispArithOp, gem5::PowerISA::IntImmArithOp, gem5::PowerISA::IntImmCompLogicOp, gem5::PowerISA::IntImmCompOp, gem5::PowerISA::IntImmLogicOp, gem5::PowerISA::IntImmOp, gem5::PowerISA::IntImmTrapOp, gem5::PowerISA::IntLogicOp, gem5::PowerISA::IntOp, gem5::PowerISA::IntRotateOp, gem5::PowerISA::IntShiftOp, gem5::PowerISA::IntTrapOp, gem5::PowerISA::MemDispOp, gem5::PowerISA::MemDispShiftOp, gem5::PowerISA::MemIndexOp, gem5::PowerISA::MemOp, gem5::PowerISA::MiscOp, gem5::PowerISA::PowerStaticInst, gem5::RegImmImmOp64, gem5::RegImmImmOp, gem5::RegImmOp, gem5::RegImmRegOp, gem5::RegImmRegShiftOp, gem5::RegMiscRegImmOp64, gem5::RegMiscRegImmOp, gem5::RegNone, gem5::RegOp64, gem5::RegOp, gem5::RegRegImmImmOp64, gem5::RegRegImmImmOp, gem5::RegRegImmOp, gem5::RegRegOp, gem5::RegRegRegImmOp64, gem5::RegRegRegImmOp, gem5::RegRegRegOp, gem5::RegRegRegRegOp, gem5::RiscvISA::AtomicMemOp, gem5::RiscvISA::AtomicMemOpMicro, gem5::RiscvISA::BSOp, gem5::RiscvISA::CompRegOp, gem5::RiscvISA::CSROp, gem5::RiscvISA::Load, gem5::RiscvISA::LoadReserved, gem5::RiscvISA::LoadReservedMicro, gem5::RiscvISA::MemFenceMicro, gem5::RiscvISA::PseudoOp, gem5::RiscvISA::RegOp, gem5::RiscvISA::Store, gem5::RiscvISA::StoreCond, gem5::RiscvISA::StoreCondMicro, gem5::RiscvISA::SystemOp, gem5::RiscvISA::Unknown, gem5::RiscvISA::VConfOp, gem5::RiscvISA::VCpyVsMicroInst, gem5::RiscvISA::VectorArithMacroInst, gem5::RiscvISA::VectorArithMicroInst, gem5::RiscvISA::VectorNonSplitInst, gem5::RiscvISA::VectorNopMicroInst, gem5::RiscvISA::VectorSlideMacroInst, gem5::RiscvISA::VectorSlideMicroInst, gem5::RiscvISA::VectorVMUNARY0MacroInst, gem5::RiscvISA::VectorVMUNARY0MicroInst, gem5::RiscvISA::VlElementMacroInst, gem5::RiscvISA::VlElementMicroInst, gem5::RiscvISA::VleMacroInst, gem5::RiscvISA::VleMicroInst, gem5::RiscvISA::VlFFTrimVlMicroOp, gem5::RiscvISA::VlIndexMacroInst, gem5::RiscvISA::VlIndexMicroInst, gem5::RiscvISA::VlSegDeIntrlvMicroInst, gem5::RiscvISA::VlSegMacroInst, gem5::RiscvISA::VlSegMicroInst, gem5::RiscvISA::VlWholeMacroInst, gem5::RiscvISA::VlWholeMicroInst, gem5::RiscvISA::VMaskMergeMicroInst, gem5::RiscvISA::VMvWholeMacroInst, gem5::RiscvISA::VMvWholeMicroInst, gem5::RiscvISA::VPinVdMicroInst, gem5::RiscvISA::VsElementMacroInst, gem5::RiscvISA::VsElementMicroInst, gem5::RiscvISA::VseMacroInst, gem5::RiscvISA::VseMicroInst, gem5::RiscvISA::VsIndexMacroInst, gem5::RiscvISA::VsIndexMicroInst, gem5::RiscvISA::VsSegIntrlvMicroInst, gem5::RiscvISA::VsSegMacroInst, gem5::RiscvISA::VsSegMicroInst, gem5::RiscvISA::VsWholeMacroInst, gem5::RiscvISA::VsWholeMicroInst, gem5::RiscvISA::VxsatMicroInst, gem5::RiscvISA::ZcmtSecondFetchInst, gem5::SparcISA::BlockMemImmMicro, gem5::SparcISA::BlockMemMicro, gem5::SparcISA::Branch, gem5::SparcISA::BranchDisp, gem5::SparcISA::BranchImm13, gem5::SparcISA::FailUnimplemented, gem5::SparcISA::FpUnimpl, gem5::SparcISA::IntOp, gem5::SparcISA::IntOpImm, gem5::SparcISA::Mem, gem5::SparcISA::MemImm, gem5::SparcISA::Nop, gem5::SparcISA::Priv, gem5::SparcISA::RdPriv, gem5::SparcISA::SetHi, gem5::SparcISA::SparcMacroInst, gem5::SparcISA::SparcStaticInst, gem5::SparcISA::Trap, gem5::SparcISA::Unknown, gem5::SparcISA::WarnUnimplemented, gem5::SparcISA::WrPriv, gem5::SparcISA::WrPrivImm, gem5::UnknownOp64, gem5::UnknownOp, gem5::WarnUnimplemented, gem5::X86ISA::InstOperands< MemOp, AddrOp >, gem5::X86ISA::InstOperands< MemOp, FloatDataOp, AddrOp >, gem5::X86ISA::InstOperands< MemOp, FoldedDataLowOp, FoldedDataHiOp, AddrOp >, gem5::X86ISA::InstOperands< MemOp, FoldedDataOp, AddrOp >, gem5::X86ISA::InstOperands< RegOpBase, Operands... >, gem5::X86ISA::InstOperands< X86MicroopBase >, gem5::X86ISA::MacroopBase, gem5::X86ISA::MicroDebug, gem5::X86ISA::X86MicroopBase, and gem5::X86ISA::X86StaticInst.

References gem5::MipsISA::pc.

Referenced by disassemble().

◆ getEMI()

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ArmStaticInst, and gem5::RiscvISA::RiscvStaticInst.

Definition at line 240 of file static_inst.hh.

Referenced by gem5::trace::CapstoneDisassembler::disassemble(), and gem5::minor::FUPipeline::findTiming().

◆ getName()

|

inline |

Return name of machine instruction.

Definition at line 371 of file static_inst.hh.

References mnemonic.

Referenced by gem5::minor::operator<<().

◆ initiateAcc()

|

inlinevirtual |

Reimplemented in gem5::ArmISAInst::MicroTcommit64, gem5::ArmISAInst::MicroTfence64, gem5::ArmISAInst::Tcancel64, gem5::ArmISAInst::Tstart64, gem5::RiscvISA::RiscvMacroInst, and gem5::SparcISA::SparcMacroInst.

Definition at line 298 of file static_inst.hh.

References panic.

◆ isAtomic()

|

inline |

Definition at line 149 of file static_inst.hh.

References flags.

Referenced by gem5::minor::Fetch2::evaluate(), and gem5::BaseCPU::probeInstCommit().

◆ isCall()

|

inline |

Definition at line 162 of file static_inst.hh.

References flags.

Referenced by gem5::branch_prediction::getBranchType(), gem5::branch_prediction::BPredUnit::predict(), gem5::branch_prediction::MPP_StatisticalCorrector_64KB::scHistoryUpdate(), gem5::branch_prediction::MPP_StatisticalCorrector_8KB::scHistoryUpdate(), gem5::BaseStackTrace::trace(), gem5::branch_prediction::MultiperspectivePerceptronTAGE::update(), and gem5::BaseCPU::CommitCPUStats::updateComCtrlStats().

◆ isCondCtrl()

|

inline |

Definition at line 166 of file static_inst.hh.

References flags.

Referenced by gem5::branch_prediction::getBranchType(), gem5::branch_prediction::MultiperspectivePerceptronTAGE::update(), and gem5::BaseCPU::CommitCPUStats::updateComCtrlStats().

◆ isControl()

|

inline |

Definition at line 161 of file static_inst.hh.

References flags.

Referenced by gem5::LooppointAnalysis::checkPc(), gem5::BaseCPU::probeInstCommit(), gem5::SimPoint::profile(), and gem5::BaseCPU::CommitCPUStats::updateComCtrlStats().

◆ isDataPrefetch()

|

inline |

Definition at line 152 of file static_inst.hh.

References flags.

Referenced by isPrefetch(), and gem5::ArmISA::Memory64::startDisassembly().

◆ isDelayedCommit()

|

inline |

Definition at line 189 of file static_inst.hh.

References flags.

◆ isDirectCtrl()

|

inline |

Definition at line 164 of file static_inst.hh.

References flags.

Referenced by gem5::branch_prediction::TAGE_SC_L_TAGE::branchTypeExtra(), gem5::LooppointAnalysis::checkPc(), gem5::branch_prediction::getBranchType(), gem5::branch_prediction::MPP_StatisticalCorrector_64KB::scHistoryUpdate(), gem5::branch_prediction::MPP_StatisticalCorrector_8KB::scHistoryUpdate(), gem5::branch_prediction::StatisticalCorrector::scHistoryUpdate(), gem5::branch_prediction::TAGE_SC_L_64KB_StatisticalCorrector::scHistoryUpdate(), gem5::branch_prediction::TAGE_SC_L_8KB_StatisticalCorrector::scHistoryUpdate(), gem5::branch_prediction::BPredUnit::squash(), gem5::branch_prediction::MultiperspectivePerceptronTAGE::update(), gem5::BaseCPU::CommitCPUStats::updateComCtrlStats(), and gem5::branch_prediction::MPP_TAGE::updateHistories().

◆ isFirstMicroop()

|

inline |

Definition at line 191 of file static_inst.hh.

References flags.

◆ isFloating()

|

inline |

Definition at line 157 of file static_inst.hh.

References flags.

Referenced by gem5::minor::Fetch2::evaluate(), and gem5::ArmISA::MicroMemOp::generateDisassembly().

◆ isFullMemBarrier()

|

inline |

Definition at line 176 of file static_inst.hh.

References flags.

◆ isHtmCancel()

|

inline |

◆ isHtmCmd()

|

inline |

Definition at line 202 of file static_inst.hh.

References isHtmCancel(), isHtmStart(), and isHtmStop().

◆ isHtmStart()

|

inline |

◆ isHtmStop()

|

inline |

◆ isIndirectCtrl()

|

inline |

Definition at line 165 of file static_inst.hh.

References flags.

Referenced by gem5::branch_prediction::getBranchType(), gem5::branch_prediction::BPredUnit::predict(), and gem5::BaseCPU::CommitCPUStats::updateComCtrlStats().

◆ isInstPrefetch()

|

inline |

Definition at line 151 of file static_inst.hh.

References flags.

Referenced by isPrefetch(), and gem5::ArmISA::Memory64::startDisassembly().

◆ isInteger()

|

inline |

Definition at line 156 of file static_inst.hh.

References flags.

Referenced by gem5::minor::Fetch2::evaluate().

◆ isInvalid()

|

inline |

Definition at line 199 of file static_inst.hh.

References flags.

◆ isLastMicroop()

|

inline |

Definition at line 190 of file static_inst.hh.

References flags.

Referenced by gem5::LooppointAnalysis::checkPc(), gem5::minor::Decode::evaluate(), gem5::o3::Fetch::fetch(), gem5::BaseCPU::probeInstCommit(), and gem5::SimPoint::profile().

◆ isLoad()

|

inline |

Definition at line 147 of file static_inst.hh.

References flags.

Referenced by gem5::minor::Fetch2::evaluate(), gem5::BaseCPU::probeInstCommit(), gem5::ArmISA::SveIndexedMemSV< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::SveIndexedMemSV(), and gem5::ArmISA::SveIndexedMemVI< RegElemType, MemElemType, MicroopType, FirstFaultWritebackMicroopType >::SveIndexedMemVI().

◆ isMacroop()

|

inline |

Definition at line 187 of file static_inst.hh.

References flags.

Referenced by gem5::minor::Decode::evaluate(), gem5::o3::Fetch::fetch(), gem5::BaseSimpleCPU::preExecute(), and gem5::Checker< DynInstPtr >::verify().

◆ isMatrix()

|

inline |

Definition at line 159 of file static_inst.hh.

References flags.

◆ isMemRef()

|

inline |

Definition at line 143 of file static_inst.hh.

References flags.

◆ isMicroop()

|

inline |

Definition at line 188 of file static_inst.hh.

References flags.

Referenced by gem5::trace::ArmNativeTrace::check(), gem5::LooppointAnalysis::checkPc(), gem5::trace::CapstoneDisassembler::disassemble(), gem5::BaseCPU::probeInstCommit(), gem5::SimPoint::profile(), and gem5::trace::ExeTracerRecord::traceInst().

◆ isNonSpeculative()

|

inline |

Definition at line 182 of file static_inst.hh.

References flags.

◆ isNop()

|

inline |

Definition at line 140 of file static_inst.hh.

References flags.

◆ isPrefetch()

|

inline |

Definition at line 153 of file static_inst.hh.

References isDataPrefetch(), and isInstPrefetch().

◆ isPseudo()

|

inline |

Definition at line 185 of file static_inst.hh.

References flags.

Referenced by gem5::trace::CapstoneDisassembler::disassemble().

◆ isQuiesce()

|

inline |

Definition at line 183 of file static_inst.hh.

References flags.

◆ isReadBarrier()

|

inline |

Definition at line 180 of file static_inst.hh.

References flags.

◆ isReturn()

|

inline |

Definition at line 163 of file static_inst.hh.

References flags.

Referenced by gem5::branch_prediction::getBranchType(), gem5::branch_prediction::BPredUnit::predict(), gem5::branch_prediction::MPP_StatisticalCorrector_64KB::scHistoryUpdate(), gem5::branch_prediction::MPP_StatisticalCorrector_8KB::scHistoryUpdate(), gem5::branch_prediction::BPredUnit::squash(), gem5::BaseStackTrace::trace(), gem5::branch_prediction::MultiperspectivePerceptronTAGE::update(), and gem5::BaseCPU::CommitCPUStats::updateComCtrlStats().

◆ isSerializeAfter()

|

inline |

Definition at line 173 of file static_inst.hh.

References flags.

◆ isSerializeBefore()

|

inline |

Definition at line 172 of file static_inst.hh.

References flags.

◆ isSerializing()

|

inline |

Definition at line 169 of file static_inst.hh.

References flags.

◆ isSquashAfter()

|

inline |

Definition at line 174 of file static_inst.hh.

References flags.

◆ isStore()

|

inline |

Definition at line 148 of file static_inst.hh.

References flags.

Referenced by gem5::minor::Fetch2::evaluate(), and gem5::BaseCPU::probeInstCommit().

◆ isStoreConditional()

|

inline |

Definition at line 150 of file static_inst.hh.

References flags.

◆ isSyscall()

|

inline |

Definition at line 186 of file static_inst.hh.

References flags.

Referenced by gem5::trace::X86NativeTrace::check().

◆ isUncondCtrl()

|

inline |

Definition at line 167 of file static_inst.hh.

References flags.

Referenced by gem5::branch_prediction::TAGE_SC_L_TAGE::branchTypeExtra(), gem5::branch_prediction::BPredUnit::predict(), gem5::branch_prediction::MPP_StatisticalCorrector_64KB::scHistoryUpdate(), gem5::branch_prediction::MPP_StatisticalCorrector_8KB::scHistoryUpdate(), gem5::branch_prediction::StatisticalCorrector::scHistoryUpdate(), gem5::branch_prediction::TAGE_SC_L_64KB_StatisticalCorrector::scHistoryUpdate(), gem5::branch_prediction::TAGE_SC_L_8KB_StatisticalCorrector::scHistoryUpdate(), gem5::BaseCPU::CommitCPUStats::updateComCtrlStats(), and gem5::branch_prediction::MPP_TAGE::updateHistories().

◆ isUnverifiable()

|

inline |

Definition at line 184 of file static_inst.hh.

References flags.

◆ isVector()

|

inline |

Definition at line 158 of file static_inst.hh.

References flags.

Referenced by gem5::minor::Fetch2::evaluate(), and gem5::trace::ExeTracerRecord::traceInst().

◆ isWriteBarrier()

|

inline |

Definition at line 181 of file static_inst.hh.

References flags.

◆ numDestRegs() [1/2]

|

inline |

Number of destination registers.

Definition at line 125 of file static_inst.hh.

References _numDestRegs.

Referenced by gem5::o3::Fetch::buildInst(), gem5::minor::Scoreboard::clearInstDests(), gem5::minor::Scoreboard::markupInstDests(), and gem5::MsrBase::printMsrBase().

◆ numDestRegs() [2/2]

|

inline |

Number of destination registers of a particular type.

Definition at line 128 of file static_inst.hh.

References _numTypedDestRegs.

◆ numSrcRegs()

|

inline |

Number of source registers.

Definition at line 123 of file static_inst.hh.

References _numSrcRegs.

Referenced by gem5::o3::Fetch::buildInst(), gem5::minor::Scoreboard::canInstIssue(), gem5::minor::Scoreboard::execSeqNumToWaitFor(), and gem5::MrsOp::generateDisassembly().

◆ opClass()

|

inline |

Operation class. Used to select appropriate function unit in issue.

Definition at line 214 of file static_inst.hh.

References _opClass.

Referenced by gem5::RiscvISA::CmMacroInst::CmMacroInst(), gem5::minor::FUPipeline::findTiming(), and gem5::trace::ExeTracerRecord::traceInst().

◆ printFlags()

| void gem5::StaticInst::printFlags | ( | std::ostream & | outs, |

| const std::string & | separator ) const |

Print a separator separated list of this instruction's set flag names on the given stream.

Definition at line 71 of file static_inst.cc.

References flags.

Referenced by gem5::trace::ExeTracerRecord::traceInst().

◆ setDelayedCommit()

|

inline |

Definition at line 210 of file static_inst.hh.

References flags.

Referenced by gem5::ArmISA::MacroVFPMemOp::MacroVFPMemOp(), gem5::ArmISA::VldMultOp::VldMultOp(), gem5::ArmISA::VldSingleOp::VldSingleOp(), gem5::ArmISA::VstMultOp::VstMultOp(), and gem5::ArmISA::VstSingleOp::VstSingleOp().

◆ setDestRegIdx()

|

inline |

Definition at line 222 of file static_inst.hh.

References gem5::ArmISA::i, and gem5::X86ISA::val.

Referenced by gem5::ArmISAInst::Tstart64::Tstart64(), gem5::ArmISAInst::Ttest64::Ttest64(), gem5::RiscvISA::VCpyVsMicroInst::VCpyVsMicroInst(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::VlSegDeIntrlvMicroInst(), gem5::RiscvISA::VMaskMergeMicroInst::VMaskMergeMicroInst(), gem5::RiscvISA::VPinVdMicroInst::VPinVdMicroInst(), and gem5::RiscvISA::VsSegIntrlvMicroInst::VsSegIntrlvMicroInst().

◆ setFirstMicroop()

|

inline |

Definition at line 208 of file static_inst.hh.

References flags.

◆ setFlag()

|

inline |

Definition at line 211 of file static_inst.hh.

References gem5::ArmISA::f, and flags.

Referenced by gem5::ArmISA::MacroMemOp::MacroMemOp().

◆ setLastMicroop()

|

inline |

Definition at line 209 of file static_inst.hh.

References flags.

Referenced by gem5::ArmISA::MacroMemOp::MacroMemOp(), and gem5::ArmISA::PairMemOp::PairMemOp().

◆ setRegIdxArrays()

|

inlineprotected |

Set the pointers which point to the arrays of source and destination register indices.

These will be defined in derived classes which know what size they need to be, and installed here so they can be accessed with the base class accessors.

Definition at line 251 of file static_inst.hh.

References _destRegIdxPtr, and _srcRegIdxPtr.

Referenced by gem5::ArmISAInst::Tstart64::Tstart64(), gem5::ArmISAInst::Ttest64::Ttest64(), gem5::RiscvISA::VCpyVsMicroInst::VCpyVsMicroInst(), gem5::RiscvISA::VlFFTrimVlMicroOp::VlFFTrimVlMicroOp(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::VlSegDeIntrlvMicroInst(), gem5::RiscvISA::VMaskMergeMicroInst::VMaskMergeMicroInst(), gem5::RiscvISA::VPinVdMicroInst::VPinVdMicroInst(), gem5::RiscvISA::VsSegIntrlvMicroInst::VsSegIntrlvMicroInst(), and gem5::RiscvISA::ZcmtSecondFetchInst::ZcmtSecondFetchInst().

◆ setSrcRegIdx()

|

inline |

Definition at line 232 of file static_inst.hh.

References gem5::ArmISA::i, and gem5::X86ISA::val.

Referenced by gem5::RiscvISA::VCpyVsMicroInst::VCpyVsMicroInst(), gem5::RiscvISA::VlFFTrimVlMicroOp::VlFFTrimVlMicroOp(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::VlSegDeIntrlvMicroInst(), gem5::RiscvISA::VMaskMergeMicroInst::VMaskMergeMicroInst(), gem5::RiscvISA::VPinVdMicroInst::VPinVdMicroInst(), and gem5::RiscvISA::VsSegIntrlvMicroInst::VsSegIntrlvMicroInst().

◆ simpleAsBytes()

|

inlineprotected |

Definition at line 376 of file static_inst.hh.

References gem5::htole(), size(), and gem5::ArmISA::t.

Referenced by gem5::ArmISA::ArmStaticInst::asBytes(), gem5::PowerISA::PowerStaticInst::asBytes(), gem5::RiscvISA::RiscvStaticInst::asBytes(), and gem5::SparcISA::SparcStaticInst::asBytes().

◆ size() [1/2]

|

inline |

Definition at line 319 of file static_inst.hh.

Referenced by gem5::RiscvISA::RiscvStaticInst::asBytes(), gem5::SparcISA::SparcStaticInst::asBytes(), gem5::trace::CapstoneDisassembler::disassemble(), gem5::X86ISA::X86StaticInst::merge(), gem5::X86ISA::MediaOpBase::numItems(), gem5::X86ISA::X86StaticInst::pick(), gem5::X86ISA::X86StaticInst::printReg(), gem5::X86ISA::X86StaticInst::signedPick(), simpleAsBytes(), and gem5::branch_prediction::BPredUnit::squash().

◆ size() [2/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::PredMacroOp, gem5::RiscvISA::RiscvMacroInst, and gem5::X86ISA::MacroopBase.

Definition at line 328 of file static_inst.hh.

References _size.

◆ srcRegIdx()

|

inline |

Return logical index (architectural reg num) of i'th source reg.

Only the entries from 0 through numSrcRegs()-1 are valid.

Definition at line 229 of file static_inst.hh.

References gem5::ArmISA::i.

Referenced by gem5::PowerISA::BranchRegCondOp::branchTarget(), gem5::minor::Scoreboard::canInstIssue(), gem5::TimingExprSrcReg::eval(), gem5::minor::Scoreboard::execSeqNumToWaitFor(), gem5::MrsOp::generateDisassembly(), gem5::PowerISA::FloatOp::generateDisassembly(), gem5::PowerISA::IntArithOp::generateDisassembly(), gem5::PowerISA::IntCompOp::generateDisassembly(), gem5::PowerISA::IntConcatRotateOp::generateDisassembly(), gem5::PowerISA::IntConcatShiftOp::generateDisassembly(), gem5::PowerISA::IntDispArithOp::generateDisassembly(), gem5::PowerISA::IntImmArithOp::generateDisassembly(), gem5::PowerISA::IntImmCompLogicOp::generateDisassembly(), gem5::PowerISA::IntImmCompOp::generateDisassembly(), gem5::PowerISA::IntImmLogicOp::generateDisassembly(), gem5::PowerISA::IntImmOp::generateDisassembly(), gem5::PowerISA::IntImmTrapOp::generateDisassembly(), gem5::PowerISA::IntLogicOp::generateDisassembly(), gem5::PowerISA::IntOp::generateDisassembly(), gem5::PowerISA::IntRotateOp::generateDisassembly(), gem5::PowerISA::IntShiftOp::generateDisassembly(), gem5::PowerISA::IntTrapOp::generateDisassembly(), gem5::PowerISA::MemDispOp::generateDisassembly(), gem5::PowerISA::MemDispShiftOp::generateDisassembly(), gem5::PowerISA::MemIndexOp::generateDisassembly(), gem5::PowerISA::MiscOp::generateDisassembly(), gem5::RiscvISA::AtomicMemOpMicro::generateDisassembly(), gem5::RiscvISA::BSOp::generateDisassembly(), gem5::RiscvISA::CompRegOp::generateDisassembly(), gem5::RiscvISA::CSROp::generateDisassembly(), gem5::RiscvISA::Load::generateDisassembly(), gem5::RiscvISA::LoadReservedMicro::generateDisassembly(), gem5::RiscvISA::RegOp::generateDisassembly(), gem5::RiscvISA::Store::generateDisassembly(), gem5::RiscvISA::StoreCondMicro::generateDisassembly(), gem5::RiscvISA::SystemOp::generateDisassembly(), gem5::RiscvISA::VConfOp::generateDisassembly(), gem5::RiscvISA::VCpyVsMicroInst::generateDisassembly(), gem5::RiscvISA::VectorArithMacroInst::generateDisassembly(), gem5::RiscvISA::VectorArithMicroInst::generateDisassembly(), gem5::RiscvISA::VectorNonSplitInst::generateDisassembly(), gem5::RiscvISA::VectorSlideMacroInst::generateDisassembly(), gem5::RiscvISA::VectorSlideMicroInst::generateDisassembly(), gem5::RiscvISA::VlElementMacroInst::generateDisassembly(), gem5::RiscvISA::VlElementMicroInst::generateDisassembly(), gem5::RiscvISA::VleMacroInst::generateDisassembly(), gem5::RiscvISA::VleMicroInst::generateDisassembly(), gem5::RiscvISA::VlIndexMacroInst::generateDisassembly(), gem5::RiscvISA::VlIndexMicroInst::generateDisassembly(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::generateDisassembly(), gem5::RiscvISA::VlSegMacroInst::generateDisassembly(), gem5::RiscvISA::VlSegMicroInst::generateDisassembly(), gem5::RiscvISA::VlWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VlWholeMicroInst::generateDisassembly(), gem5::RiscvISA::VMaskMergeMicroInst::generateDisassembly(), gem5::RiscvISA::VMvWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VMvWholeMicroInst::generateDisassembly(), gem5::RiscvISA::VPinVdMicroInst::generateDisassembly(), gem5::RiscvISA::VsElementMacroInst::generateDisassembly(), gem5::RiscvISA::VsElementMicroInst::generateDisassembly(), gem5::RiscvISA::VseMacroInst::generateDisassembly(), gem5::RiscvISA::VseMicroInst::generateDisassembly(), gem5::RiscvISA::VsIndexMacroInst::generateDisassembly(), gem5::RiscvISA::VsIndexMicroInst::generateDisassembly(), gem5::RiscvISA::VsSegIntrlvMicroInst::generateDisassembly(), gem5::RiscvISA::VsSegMacroInst::generateDisassembly(), gem5::RiscvISA::VsSegMicroInst::generateDisassembly(), gem5::RiscvISA::VsWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VsWholeMicroInst::generateDisassembly(), gem5::SparcISA::BlockMemImmMicro::generateDisassembly(), gem5::SparcISA::BlockMemMicro::generateDisassembly(), gem5::SparcISA::Branch::generateDisassembly(), gem5::SparcISA::BranchImm13::generateDisassembly(), gem5::SparcISA::IntOp::generateDisassembly(), gem5::SparcISA::IntOpImm::generateDisassembly(), gem5::SparcISA::Mem::generateDisassembly(), gem5::SparcISA::MemImm::generateDisassembly(), gem5::SparcISA::SparcStaticInst::generateDisassembly(), gem5::SparcISA::Trap::generateDisassembly(), gem5::SparcISA::WrPriv::generateDisassembly(), gem5::SparcISA::WrPrivImm::generateDisassembly(), gem5::SparcISA::IntOp::printPseudoOps(), gem5::SparcISA::IntOpImm::printPseudoOps(), and gem5::SparcISA::SparcStaticInst::printSrcReg().

Member Data Documentation

◆ _destRegIdxPtr

|

private |

◆ _numDestRegs

|

protected |

See numDestRegs().

Definition at line 112 of file static_inst.hh.

Referenced by gem5::PowerISA::FloatOp::generateDisassembly(), gem5::PowerISA::IntArithOp::generateDisassembly(), gem5::PowerISA::IntConcatRotateOp::generateDisassembly(), gem5::PowerISA::IntConcatShiftOp::generateDisassembly(), gem5::PowerISA::IntDispArithOp::generateDisassembly(), gem5::PowerISA::IntImmArithOp::generateDisassembly(), gem5::PowerISA::IntImmLogicOp::generateDisassembly(), gem5::PowerISA::IntImmOp::generateDisassembly(), gem5::PowerISA::IntLogicOp::generateDisassembly(), gem5::PowerISA::IntOp::generateDisassembly(), gem5::PowerISA::IntRotateOp::generateDisassembly(), gem5::PowerISA::IntShiftOp::generateDisassembly(), gem5::PowerISA::MemDispOp::generateDisassembly(), gem5::PowerISA::MemDispShiftOp::generateDisassembly(), gem5::PowerISA::MemIndexOp::generateDisassembly(), gem5::PowerISA::MiscOp::generateDisassembly(), gem5::SparcISA::Branch::generateDisassembly(), gem5::SparcISA::BranchImm13::generateDisassembly(), gem5::SparcISA::IntOp::generateDisassembly(), gem5::SparcISA::IntOpImm::generateDisassembly(), gem5::SparcISA::SparcStaticInst::generateDisassembly(), gem5::ArmISAInst::MacroTmeOp::MacroTmeOp(), gem5::ArmISAInst::MicroTcommit64::MicroTcommit64(), gem5::ArmISAInst::MicroTfence64::MicroTfence64(), numDestRegs(), gem5::SparcISA::SparcStaticInst::printDestReg(), gem5::ArmISAInst::Tcancel64::Tcancel64(), gem5::ArmISAInst::Tstart64::Tstart64(), gem5::ArmISAInst::Ttest64::Ttest64(), gem5::RiscvISA::VCpyVsMicroInst::VCpyVsMicroInst(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::VlSegDeIntrlvMicroInst(), gem5::RiscvISA::VMaskMergeMicroInst::VMaskMergeMicroInst(), gem5::RiscvISA::VPinVdMicroInst::VPinVdMicroInst(), and gem5::RiscvISA::VsSegIntrlvMicroInst::VsSegIntrlvMicroInst().

◆ _numSrcRegs

|

protected |

See numSrcRegs().

Definition at line 109 of file static_inst.hh.

Referenced by gem5::PowerISA::BranchRegCondOp::branchTarget(), gem5::RiscvISA::VMaskMergeMicroInst::execute(), gem5::PowerISA::FloatOp::generateDisassembly(), gem5::PowerISA::IntArithOp::generateDisassembly(), gem5::PowerISA::IntCompOp::generateDisassembly(), gem5::PowerISA::IntConcatRotateOp::generateDisassembly(), gem5::PowerISA::IntConcatShiftOp::generateDisassembly(), gem5::PowerISA::IntDispArithOp::generateDisassembly(), gem5::PowerISA::IntImmArithOp::generateDisassembly(), gem5::PowerISA::IntImmCompLogicOp::generateDisassembly(), gem5::PowerISA::IntImmCompOp::generateDisassembly(), gem5::PowerISA::IntImmLogicOp::generateDisassembly(), gem5::PowerISA::IntImmOp::generateDisassembly(), gem5::PowerISA::IntImmTrapOp::generateDisassembly(), gem5::PowerISA::IntLogicOp::generateDisassembly(), gem5::PowerISA::IntOp::generateDisassembly(), gem5::PowerISA::IntRotateOp::generateDisassembly(), gem5::PowerISA::IntShiftOp::generateDisassembly(), gem5::PowerISA::IntTrapOp::generateDisassembly(), gem5::PowerISA::MemDispOp::generateDisassembly(), gem5::PowerISA::MemDispShiftOp::generateDisassembly(), gem5::PowerISA::MemIndexOp::generateDisassembly(), gem5::PowerISA::MiscOp::generateDisassembly(), gem5::RiscvISA::CSROp::generateDisassembly(), gem5::RiscvISA::RegOp::generateDisassembly(), gem5::RiscvISA::Store::generateDisassembly(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::generateDisassembly(), gem5::RiscvISA::VMaskMergeMicroInst::generateDisassembly(), gem5::RiscvISA::VsSegIntrlvMicroInst::generateDisassembly(), gem5::SparcISA::Branch::generateDisassembly(), gem5::SparcISA::BranchImm13::generateDisassembly(), gem5::SparcISA::IntOp::generateDisassembly(), gem5::SparcISA::IntOpImm::generateDisassembly(), gem5::SparcISA::SparcStaticInst::generateDisassembly(), gem5::ArmISAInst::MacroTmeOp::MacroTmeOp(), gem5::ArmISAInst::MicroTcommit64::MicroTcommit64(), gem5::ArmISAInst::MicroTfence64::MicroTfence64(), numSrcRegs(), gem5::SparcISA::IntOpImm::printPseudoOps(), gem5::SparcISA::SparcStaticInst::printSrcReg(), gem5::ArmISAInst::Tcancel64::Tcancel64(), gem5::ArmISAInst::Tstart64::Tstart64(), gem5::ArmISAInst::Ttest64::Ttest64(), gem5::RiscvISA::VCpyVsMicroInst::VCpyVsMicroInst(), gem5::RiscvISA::VlFFTrimVlMicroOp::VlFFTrimVlMicroOp(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::VlSegDeIntrlvMicroInst(), gem5::RiscvISA::VMaskMergeMicroInst::VMaskMergeMicroInst(), gem5::RiscvISA::VPinVdMicroInst::VPinVdMicroInst(), and gem5::RiscvISA::VsSegIntrlvMicroInst::VsSegIntrlvMicroInst().

◆ _numTypedDestRegs

|

protected |

Definition at line 114 of file static_inst.hh.

Referenced by numDestRegs(), gem5::ArmISAInst::Tstart64::Tstart64(), gem5::ArmISAInst::Ttest64::Ttest64(), gem5::RiscvISA::VCpyVsMicroInst::VCpyVsMicroInst(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::VlSegDeIntrlvMicroInst(), gem5::RiscvISA::VMaskMergeMicroInst::VMaskMergeMicroInst(), gem5::RiscvISA::VPinVdMicroInst::VPinVdMicroInst(), and gem5::RiscvISA::VsSegIntrlvMicroInst::VsSegIntrlvMicroInst().

◆ _opClass

|

protected |

See opClass().

Definition at line 106 of file static_inst.hh.

Referenced by opClass(), and StaticInst().

◆ _size

|

protected |

Instruction size in bytes.

Necessary for dynamic instruction sizes

Definition at line 260 of file static_inst.hh.

Referenced by gem5::ArmISA::PredMacroOp::size(), gem5::RiscvISA::RiscvMacroInst::size(), size(), size(), and gem5::X86ISA::MacroopBase::size().

◆ _srcRegIdxPtr

|

private |

◆ cachedDisassembly

|

mutableprotected |

String representation of disassembly (lazily evaluated via disassemble()).

Definition at line 274 of file static_inst.hh.

Referenced by gem5::PowerISA::PCDependentDisassembly::disassemble(), and disassemble().

◆ flags

|

protected |

Flag values for this instruction.

Definition at line 103 of file static_inst.hh.

Referenced by gem5::AtOp64::addressTranslation64(), gem5::ArmISA::FpOp::advancePC(), gem5::ArmISA::FpOp::advancePC(), gem5::ArmISA::MicroOp::advancePC(), gem5::ArmISA::MicroOp::advancePC(), gem5::ArmISA::MicroOpX::advancePC(), gem5::ArmISA::MicroOpX::advancePC(), gem5::ArmISA::MightBeMicro64::advancePC(), gem5::ArmISA::MightBeMicro64::advancePC(), gem5::ArmISA::MightBeMicro::advancePC(), gem5::ArmISA::MightBeMicro::advancePC(), gem5::ArmISA::PredMicroop::advancePC(), gem5::ArmISA::PredMicroop::advancePC(), gem5::RiscvISA::RiscvMicroInst::advancePC(), gem5::RiscvISA::RiscvMicroInst::advancePC(), gem5::SparcISA::SparcMicroInst::advancePC(), gem5::SparcISA::SparcMicroInst::advancePC(), gem5::X86ISA::X86MicroopBase::advancePC(), gem5::X86ISA::X86MicroopBase::advancePC(), gem5::X86ISA::X86MicroopBase::checkCondition(), gem5::RiscvISA::CSROp::CSROp(), gem5::DecoderFaultInst::DecoderFaultInst(), gem5::SparcISA::FailUnimplemented::FailUnimplemented(), gem5::ArmISA::FpRegImmOp::FpRegImmOp(), gem5::ArmISA::FpRegRegImmOp::FpRegRegImmOp(), gem5::ArmISA::FpRegRegOp::FpRegRegOp(), gem5::ArmISA::FpRegRegRegCondOp::FpRegRegRegCondOp(), gem5::ArmISA::FpRegRegRegImmOp::FpRegRegRegImmOp(), gem5::ArmISA::FpRegRegRegOp::FpRegRegRegOp(), gem5::ArmISA::FpRegRegRegRegOp::FpRegRegRegRegOp(), gem5::PowerISA::MemDispOp::generateDisassembly(), gem5::PowerISA::MemDispShiftOp::generateDisassembly(), gem5::PowerISA::MemIndexOp::generateDisassembly(), gem5::SparcISA::BlockMemImmMicro::generateDisassembly(), gem5::SparcISA::BlockMemMicro::generateDisassembly(), gem5::SparcISA::Mem::generateDisassembly(), gem5::SparcISA::MemImm::generateDisassembly(), gem5::X86ISA::RegOpBase::genFlags(), isAtomic(), isCall(), isCondCtrl(), isControl(), isDataPrefetch(), isDelayedCommit(), isDirectCtrl(), isFirstMicroop(), isFloating(), isFullMemBarrier(), isHtmCancel(), isHtmStart(), isHtmStop(), isIndirectCtrl(), isInstPrefetch(), isInteger(), isInvalid(), isLastMicroop(), isLoad(), isMacroop(), isMatrix(), isMemRef(), isMicroop(), isNonSpeculative(), isNop(), isPseudo(), isQuiesce(), isReadBarrier(), isReturn(), isSerializeAfter(), isSerializeBefore(), isSerializing(), isSquashAfter(), isStore(), isStoreConditional(), isSyscall(), isUncondCtrl(), isUnverifiable(), isVector(), isWriteBarrier(), gem5::X86ISA::MacroopBase::MacroopBase(), gem5::McrMrcMiscInst::McrMrcMiscInst(), gem5::ArmISAInst::MicroTcommit64::MicroTcommit64(), gem5::ArmISAInst::MicroTfence64::MicroTfence64(), gem5::SparcISA::Nop::Nop(), gem5::ArmISA::PredMacroOp::PredMacroOp(), gem5::ArmISA::PredMicroop::PredMicroop(), printFlags(), gem5::RiscvISA::RiscvMacroInst::RiscvMacroInst(), gem5::RiscvISA::RiscvMicroInst::RiscvMicroInst(), setDelayedCommit(), gem5::ArmISA::Memory64::setExcAcRel(), setFirstMicroop(), setFlag(), setLastMicroop(), gem5::SparcISA::SparcDelayedMicroInst::SparcDelayedMicroInst(), gem5::SparcISA::SparcMacroInst::SparcMacroInst(), gem5::SparcISA::SparcMicroInst::SparcMicroInst(), gem5::ArmISAInst::Tcancel64::Tcancel64(), gem5::ArmISAInst::Tstart64::Tstart64(), gem5::ArmISAInst::Ttest64::Ttest64(), gem5::RiscvISA::Unknown::Unknown(), gem5::SparcISA::Unknown::Unknown(), gem5::RiscvISA::VConfOp::VConfOp(), gem5::RiscvISA::VectorArithMacroInst::VectorArithMacroInst(), gem5::RiscvISA::VectorMacroInst::VectorMacroInst(), gem5::RiscvISA::VectorMicroInst::VectorMicroInst(), gem5::RiscvISA::VectorNonSplitInst::VectorNonSplitInst(), gem5::RiscvISA::VectorSlideMacroInst::VectorSlideMacroInst(), gem5::RiscvISA::VectorVMUNARY0MacroInst::VectorVMUNARY0MacroInst(), gem5::RiscvISA::VleMicroInst::VleMicroInst(), gem5::RiscvISA::VlFFTrimVlMicroOp::VlFFTrimVlMicroOp(), gem5::RiscvISA::VlSegMicroInst::VlSegMicroInst(), gem5::RiscvISA::VseMicroInst::VseMicroInst(), gem5::RiscvISA::VsSegMicroInst::VsSegMicroInst(), gem5::X86ISA::X86MicroopBase::X86MicroopBase(), and gem5::RiscvISA::ZcmtSecondFetchInst::ZcmtSecondFetchInst().

◆ mnemonic

|

protected |

Base mnemonic (e.g., "add").

Used by generateDisassembly() methods. Also useful to readily identify instructions from within the debugger when cachedDisassembly has not been initialized.

Definition at line 268 of file static_inst.hh.

Referenced by gem5::ArmISA::ArmStaticInst::checkAdvSIMDOrFPEnabled32(), gem5::ArmISA::ArmStaticInst::checkForWFxTrap32(), gem5::ArmISAInst::MicroTcommit64::completeAcc(), gem5::ArmISAInst::Tcancel64::completeAcc(), gem5::ArmISAInst::Tstart64::completeAcc(), gem5::ArmISAInst::Ttest64::execute(), gem5::FailUnimplemented::execute(), gem5::McrMrcImplDefined::execute(), gem5::SparcISA::FailUnimplemented::execute(), gem5::SparcISA::WarnUnimplemented::execute(), gem5::WarnUnimplemented::execute(), gem5::ArmISA::PredMacroOp::generateDisassembly(), gem5::ArmISA::SveElemCountOp::generateDisassembly(), gem5::FailUnimplemented::generateDisassembly(), gem5::McrMrcImplDefined::generateDisassembly(), gem5::McrMrcMiscInst::generateDisassembly(), gem5::PowerISA::BranchDispCondOp::generateDisassembly(), gem5::PowerISA::BranchOp::generateDisassembly(), gem5::PowerISA::BranchRegCondOp::generateDisassembly(), gem5::PowerISA::CondLogicOp::generateDisassembly(), gem5::PowerISA::CondMoveOp::generateDisassembly(), gem5::PowerISA::FloatOp::generateDisassembly(), gem5::PowerISA::IntArithOp::generateDisassembly(), gem5::PowerISA::IntCompOp::generateDisassembly(), gem5::PowerISA::IntConcatRotateOp::generateDisassembly(), gem5::PowerISA::IntConcatShiftOp::generateDisassembly(), gem5::PowerISA::IntDispArithOp::generateDisassembly(), gem5::PowerISA::IntImmArithOp::generateDisassembly(), gem5::PowerISA::IntImmCompLogicOp::generateDisassembly(), gem5::PowerISA::IntImmCompOp::generateDisassembly(), gem5::PowerISA::IntImmLogicOp::generateDisassembly(), gem5::PowerISA::IntImmOp::generateDisassembly(), gem5::PowerISA::IntImmTrapOp::generateDisassembly(), gem5::PowerISA::IntLogicOp::generateDisassembly(), gem5::PowerISA::IntOp::generateDisassembly(), gem5::PowerISA::IntRotateOp::generateDisassembly(), gem5::PowerISA::IntShiftOp::generateDisassembly(), gem5::PowerISA::IntTrapOp::generateDisassembly(), gem5::PowerISA::MemDispOp::generateDisassembly(), gem5::PowerISA::MemDispShiftOp::generateDisassembly(), gem5::PowerISA::MemIndexOp::generateDisassembly(), gem5::PowerISA::MemOp::generateDisassembly(), gem5::PowerISA::MiscOp::generateDisassembly(), gem5::PowerISA::PowerStaticInst::generateDisassembly(), gem5::RiscvISA::AtomicMemOp::generateDisassembly(), gem5::RiscvISA::AtomicMemOpMicro::generateDisassembly(), gem5::RiscvISA::BSOp::generateDisassembly(), gem5::RiscvISA::CompRegOp::generateDisassembly(), gem5::RiscvISA::CSROp::generateDisassembly(), gem5::RiscvISA::Load::generateDisassembly(), gem5::RiscvISA::LoadReserved::generateDisassembly(), gem5::RiscvISA::LoadReservedMicro::generateDisassembly(), gem5::RiscvISA::MemFenceMicro::generateDisassembly(), gem5::RiscvISA::PseudoOp::generateDisassembly(), gem5::RiscvISA::RegOp::generateDisassembly(), gem5::RiscvISA::Store::generateDisassembly(), gem5::RiscvISA::StoreCond::generateDisassembly(), gem5::RiscvISA::StoreCondMicro::generateDisassembly(), gem5::RiscvISA::SystemOp::generateDisassembly(), gem5::RiscvISA::VConfOp::generateDisassembly(), gem5::RiscvISA::VCpyVsMicroInst::generateDisassembly(), gem5::RiscvISA::VectorArithMacroInst::generateDisassembly(), gem5::RiscvISA::VectorArithMicroInst::generateDisassembly(), gem5::RiscvISA::VectorNonSplitInst::generateDisassembly(), gem5::RiscvISA::VectorNopMicroInst::generateDisassembly(), gem5::RiscvISA::VectorSlideMacroInst::generateDisassembly(), gem5::RiscvISA::VectorSlideMicroInst::generateDisassembly(), gem5::RiscvISA::VectorVMUNARY0MacroInst::generateDisassembly(), gem5::RiscvISA::VectorVMUNARY0MicroInst::generateDisassembly(), gem5::RiscvISA::VlElementMacroInst::generateDisassembly(), gem5::RiscvISA::VlElementMicroInst::generateDisassembly(), gem5::RiscvISA::VleMacroInst::generateDisassembly(), gem5::RiscvISA::VleMicroInst::generateDisassembly(), gem5::RiscvISA::VlFFTrimVlMicroOp::generateDisassembly(), gem5::RiscvISA::VlIndexMacroInst::generateDisassembly(), gem5::RiscvISA::VlIndexMicroInst::generateDisassembly(), gem5::RiscvISA::VlSegDeIntrlvMicroInst::generateDisassembly(), gem5::RiscvISA::VlSegMacroInst::generateDisassembly(), gem5::RiscvISA::VlSegMicroInst::generateDisassembly(), gem5::RiscvISA::VlWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VlWholeMicroInst::generateDisassembly(), gem5::RiscvISA::VMaskMergeMicroInst::generateDisassembly(), gem5::RiscvISA::VMvWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VMvWholeMicroInst::generateDisassembly(), gem5::RiscvISA::VPinVdMicroInst::generateDisassembly(), gem5::RiscvISA::VsElementMacroInst::generateDisassembly(), gem5::RiscvISA::VsElementMicroInst::generateDisassembly(), gem5::RiscvISA::VseMacroInst::generateDisassembly(), gem5::RiscvISA::VseMicroInst::generateDisassembly(), gem5::RiscvISA::VsIndexMacroInst::generateDisassembly(), gem5::RiscvISA::VsIndexMicroInst::generateDisassembly(), gem5::RiscvISA::VsSegIntrlvMicroInst::generateDisassembly(), gem5::RiscvISA::VsSegMacroInst::generateDisassembly(), gem5::RiscvISA::VsSegMicroInst::generateDisassembly(), gem5::RiscvISA::VsWholeMacroInst::generateDisassembly(), gem5::RiscvISA::VsWholeMicroInst::generateDisassembly(), gem5::RiscvISA::VxsatMicroInst::generateDisassembly(), gem5::RiscvISA::ZcmtSecondFetchInst::generateDisassembly(), gem5::SparcISA::BlockMemImmMicro::generateDisassembly(), gem5::SparcISA::BlockMemMicro::generateDisassembly(), gem5::SparcISA::Branch::generateDisassembly(), gem5::SparcISA::BranchDisp::generateDisassembly(), gem5::SparcISA::BranchImm13::generateDisassembly(), gem5::SparcISA::FailUnimplemented::generateDisassembly(), gem5::SparcISA::FpUnimpl::generateDisassembly(), gem5::SparcISA::IntOp::generateDisassembly(), gem5::SparcISA::IntOpImm::generateDisassembly(), gem5::SparcISA::Mem::generateDisassembly(), gem5::SparcISA::MemImm::generateDisassembly(), gem5::SparcISA::Nop::generateDisassembly(), gem5::SparcISA::Priv::generateDisassembly(), gem5::SparcISA::RdPriv::generateDisassembly(), gem5::SparcISA::SetHi::generateDisassembly(), gem5::SparcISA::SparcMacroInst::generateDisassembly(), gem5::SparcISA::SparcStaticInst::generateDisassembly(), gem5::SparcISA::Trap::generateDisassembly(), gem5::SparcISA::WarnUnimplemented::generateDisassembly(), gem5::SparcISA::WrPriv::generateDisassembly(), gem5::SparcISA::WrPrivImm::generateDisassembly(), gem5::WarnUnimplemented::generateDisassembly(), gem5::X86ISA::InstOperands< RegOpBase, Operands... >::generateDisassembly(), gem5::X86ISA::MacroopBase::generateDisassembly(), gem5::X86ISA::MicroDebug::generateDisassembly(), gem5::X86ISA::X86MicroopBase::generateDisassembly(), gem5::X86ISA::X86StaticInst::generateDisassembly(), getName(), gem5::ArmISAInst::MicroTcommit64::initiateAcc(), gem5::ArmISAInst::Tcancel64::initiateAcc(), gem5::ArmISAInst::Tstart64::initiateAcc(), gem5::ArmISA::ArmStaticInst::printMnemonic(), gem5::SparcISA::SparcStaticInst::printMnemonic(), gem5::X86ISA::X86StaticInst::printMnemonic(), gem5::X86ISA::X86StaticInst::printMnemonic(), gem5::SparcISA::IntOp::printPseudoOps(), gem5::SparcISA::IntOpImm::printPseudoOps(), StaticInst(), gem5::ArmISA::ArmStaticInst::undefined(), and gem5::ArmISA::ArmStaticInst::undefinedFault32().

◆ nullStaticInstPtr

|

static |

Pointer to a statically allocated "null" instruction object.

Definition at line 238 of file static_inst.hh.

The documentation for this class was generated from the following files:

- cpu/static_inst.hh

- cpu/static_inst.cc

Generated on Sat Oct 18 2025 08:06:54 for gem5 by doxygen 1.14.0