The trace cpu replays traces generated using the elastic trace probe attached to the O3 CPU model. More...

#include <trace_cpu.hh>

Classes | |

| class | DcachePort |

| DcachePort class that interfaces with L1 Data Cache. More... | |

| class | ElasticDataGen |

| The elastic data memory request generator to read protobuf trace containing execution trace annotated with data and ordering dependencies. More... | |

| class | FixedRetryGen |

| Generator to read protobuf trace containing memory requests at fixed timestamps, perform flow control and issue memory requests. More... | |

| class | IcachePort |

| IcachePort class that interfaces with L1 Instruction Cache. More... | |

| struct | TraceStats |

Public Member Functions | |

| TraceCPU (const TraceCPUParams ¶ms) | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Counter | totalOps () const |

| Return totalOps as the number of committed micro-ops plus the speculatively issued loads that are modelled in the TraceCPU replay. | |

| void | updateNumOps (uint64_t rob_num) |

| void | icacheRetryRecvd () |

| When instruction cache port receives a retry, schedule event icacheNextEvent. | |

| void | dcacheRetryRecvd () |

| When data cache port receives a retry, schedule event dcacheNextEvent. | |

| void | dcacheRecvTimingResp (PacketPtr pkt) |

| When data cache port receives a response, this calls the dcache generator method handle to complete the load writeback. | |

| void | schedDcacheNextEvent (Tick when) |

| Schedule event dcacheNextEvent at the given tick. | |

| Port & | getInstPort () |

| Used to get a reference to the icache port. | |

| Port & | getDataPort () |

| Used to get a reference to the dcache port. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. | |

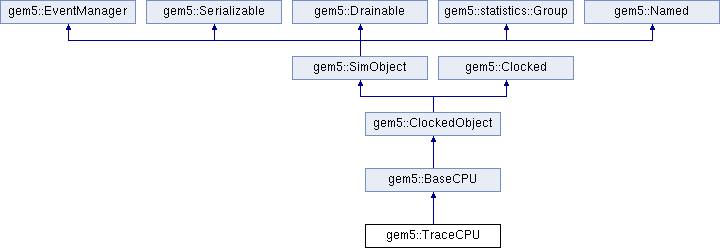

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| void | schedIcacheNext () |

| This is the control flow that uses the functionality of the icacheGen to replay the trace. | |

| void | schedDcacheNext () |

| This is the control flow that uses the functionality of the dcacheGen to replay the trace. | |

| void | checkAndSchedExitEvent () |

| This is called when either generator finishes executing from the trace. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| const Addr | cacheLineSize |

| Cache the cache line size that we get from the system. | |

| IcachePort | icachePort |

| Port to connect to L1 instruction cache. | |

| DcachePort | dcachePort |

| Port to connect to L1 data cache. | |

| const RequestorID | instRequestorID |

| Requestor id for instruction read requests. | |

| const RequestorID | dataRequestorID |

| Requestor id for data read and write requests. | |

| std::string | instTraceFile |

| File names for input instruction and data traces. | |

| std::string | dataTraceFile |

| FixedRetryGen | icacheGen |

| Instance of FixedRetryGen to replay instruction read requests. | |

| ElasticDataGen | dcacheGen |

| Instance of ElasticDataGen to replay data read and write requests. | |

| EventFunctionWrapper | icacheNextEvent |

| Event for the control flow method schedIcacheNext() | |

| EventFunctionWrapper | dcacheNextEvent |

| Event for the control flow method schedDcacheNext() | |

| bool | oneTraceComplete |

| Set to true when one of the generators finishes replaying its trace. | |

| Tick | traceOffset |

| This stores the time offset in the trace, which is taken away from the ready times of requests. | |

| CountedExitEvent * | execCompleteEvent |

| A CountedExitEvent which when serviced decrements the counter. | |

| const bool | enableEarlyExit |

| Exit when any one Trace CPU completes its execution. | |

| const uint64_t | progressMsgInterval |

| Interval of committed instructions specified by the user at which a progress info message is printed. | |

| uint64_t | progressMsgThreshold |

| gem5::TraceCPU::TraceStats | traceStats |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Static Protected Attributes | |

| static int | numTraceCPUs = 0 |

| Number of Trace CPUs in the system used as a shared variable and passed to the CountedExitEvent event used for counting down exit events. | |

Additional Inherited Members | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Detailed Description

The trace cpu replays traces generated using the elastic trace probe attached to the O3 CPU model.

The elastic trace is an execution trace with register data dependencies and ordering dependencies annotated to it. The trace cpu also replays a fixed timestamp fetch trace that is also generated by the elastic trace probe. This trace cpu model aims at achieving faster simulation compared to the detailed cpu model and good correlation when the same trace is used for playback on different memory sub-systems.

The TraceCPU has two port subclasses inherited from RequestPort for instruction and data ports. It issues the memory requests deducing the timing from the trace and without performing real execution of micro-ops. As soon as the last dependency for an instruction is complete, its computational delay, also provided in the input trace is added. The dependency-free nodes are maintained in a list, called 'ReadyList', ordered by ready time. Instructions which depend on load stall until the responses for read requests are received thus achieving elastic replay. If the dependency is not found when adding a new node, it is assumed complete. Thus, if this node is found to be completely dependency-free its issue time is calculated and it is added to the ready list immediately. This is encapsulated in the subclass ElasticDataGen.

If ready nodes are issued in an unconstrained way there can be more nodes outstanding which results in divergence in timing compared to the O3CPU. Therefore, the Trace CPU also models hardware resources. A sub-class to model hardware resources contains the maximum sizes of load buffer, store buffer and ROB. If resources are not available, the node is not issued. Such nodes that are pending issue are held in the 'depFreeQueue' structure.

Modeling the ROB size in the Trace CPU as a resource limitation is arguably the most important parameter of all resources. The ROB occupancy is estimated using the newly added field 'robNum'. We need to use ROB number as sequence number is at times much higher due to squashing and trace replay is focused on correct path modeling.

A map called 'inFlightNodes' is added to track nodes that are not only in the readyList but also load nodes that are executed (and thus removed from readyList) but are not complete. ReadyList handles what and when to execute next node while the inFlightNodes is used for resource modelling. The oldest ROB number is updated when any node occupies the ROB or when an entry in the ROB is released. The ROB occupancy is equal to the difference in the ROB number of the newly dependency-free node and the oldest ROB number in flight.

If no node depends on a non load/store node then there is no reason to track it in the dependency graph. We filter out such nodes but count them and add a weight field to the subsequent node that we do include in the trace. The weight field is used to model ROB occupancy during replay.

The depFreeQueue is chosen to be FIFO so that child nodes which are in program order get pushed into it in that order and thus issued in program order, like in the O3CPU. This is also why the dependents is made a sequential container, std::set to std::vector. We only check head of the depFreeQueue as nodes are issued in order and blocking on head models that better than looping the entire queue. An alternative choice would be to inspect top N pending nodes where N is the issue-width. This is left for future as the timing correlation looks good as it is.

At the start of an execution event, first we attempt to issue such pending nodes by checking if appropriate resources have become available. If yes, we compute the execute tick with respect to the time then. Then we proceed to complete nodes from the readyList.

When a read response is received, sometimes a dependency on it that was supposed to be released when it was issued is still not released. This occurs because the dependent gets added to the graph after the read was sent. So the check is made less strict and the dependency is marked complete on read response instead of insisting that it should have been removed on read sent.

There is a check for requests spanning two cache lines as this condition triggers an assert fail in the L1 cache. If it does then truncate the size to access only until the end of that line and ignore the remainder. Strictly-ordered requests are skipped and the dependencies on such requests are handled by simply marking them complete immediately.

A CountedExitEvent that contains a static int belonging to the Trace CPU class as a down counter is used to implement multi Trace CPU simulation exit.

Definition at line 144 of file trace_cpu.hh.

Constructor & Destructor Documentation

◆ TraceCPU()

| gem5::TraceCPU::TraceCPU | ( | const TraceCPUParams & | params | ) |

Definition at line 50 of file trace_cpu.cc.

References cacheLineSize, gem5::ClockedObject::ClockedObject(), dataRequestorID, dataTraceFile, dcacheGen, dcachePort, icacheGen, icacheNextEvent, icachePort, instRequestorID, instTraceFile, gem5::SimObject::params(), schedIcacheNext(), and gem5::X86ISA::system.

Referenced by gem5::TraceCPU::DcachePort::DcachePort(), gem5::TraceCPU::ElasticDataGen::ElasticDataGen(), gem5::TraceCPU::FixedRetryGen::FixedRetryGen(), gem5::TraceCPU::IcachePort::IcachePort(), and gem5::TraceCPU::TraceStats::TraceStats().

Member Function Documentation

◆ checkAndSchedExitEvent()

|

protected |

This is called when either generator finishes executing from the trace.

Definition at line 182 of file trace_cpu.cc.

References gem5::curTick(), enableEarlyExit, execCompleteEvent, gem5::exitSimLoop(), inform, gem5::Named::name(), oneTraceComplete, and gem5::EventManager::schedule().

Referenced by schedDcacheNext(), and schedIcacheNext().

◆ dcacheRecvTimingResp()

| void gem5::TraceCPU::dcacheRecvTimingResp | ( | PacketPtr | pkt | ) |

When data cache port receives a response, this calls the dcache generator method handle to complete the load writeback.

- Parameters

-

pkt Pointer to packet received

Definition at line 1180 of file trace_cpu.cc.

◆ dcacheRetryRecvd()

| void gem5::TraceCPU::dcacheRetryRecvd | ( | ) |

When data cache port receives a retry, schedule event dcacheNextEvent.

Definition at line 1124 of file trace_cpu.cc.

References gem5::curTick(), dcacheNextEvent, DPRINTF, and gem5::EventManager::schedule().

◆ getDataPort()

|

inline |

Used to get a reference to the dcache port.

Definition at line 1113 of file trace_cpu.hh.

References dcachePort.

Referenced by getPort().

◆ getInstPort()

|

inline |

Used to get a reference to the icache port.

Definition at line 1110 of file trace_cpu.hh.

References icachePort.

Referenced by getPort().

◆ getPort()

|

overridevirtual |

Get a port on this CPU.

All CPUs have a data and instruction port, and this method uses getDataPort and getInstPort of the subclasses to resolve the two ports.

- Parameters

-

if_name the port name idx ignored index

- Returns

- a reference to the port with the given name

Reimplemented from gem5::SimObject.

Definition at line 1150 of file trace_cpu.cc.

References getDataPort(), getInstPort(), and gem5::SimObject::getPort().

◆ icacheRetryRecvd()

| void gem5::TraceCPU::icacheRetryRecvd | ( | ) |

When instruction cache port receives a retry, schedule event icacheNextEvent.

Definition at line 1114 of file trace_cpu.cc.

References gem5::curTick(), DPRINTF, icacheNextEvent, and gem5::EventManager::schedule().

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Definition at line 99 of file trace_cpu.cc.

References dataTraceFile, dcacheGen, dcacheNextEvent, DPRINTF, enableEarlyExit, execCompleteEvent, icacheGen, icacheNextEvent, inform, gem5::SimObject::init(), instTraceFile, gem5::Named::name(), numTraceCPUs, gem5::EventManager::schedule(), and traceOffset.

◆ schedDcacheNext()

|

protected |

This is the control flow that uses the functionality of the dcacheGen to replay the trace.

It calls execute(). It checks if execution is complete and schedules an event to exit simulation accordingly.

Definition at line 168 of file trace_cpu.cc.

References checkAndSchedExitEvent(), gem5::Clocked::clockEdge(), gem5::Clocked::clockPeriod(), dcacheGen, DPRINTF, and traceStats.

◆ schedDcacheNextEvent()

| void gem5::TraceCPU::schedDcacheNextEvent | ( | Tick | when | ) |

Schedule event dcacheNextEvent at the given tick.

- Parameters

-

when Tick at which to schedule event

Definition at line 1134 of file trace_cpu.cc.

References dcacheNextEvent, DPRINTF, gem5::EventManager::reschedule(), gem5::EventManager::schedule(), and traceStats.

◆ schedIcacheNext()

|

protected |

This is the control flow that uses the functionality of the icacheGen to replay the trace.

It calls tryNext(). If it returns true then next event is scheduled at curTick() plus delta. If it returns false then delta is ignored and control is brought back via recvRetry().

Definition at line 142 of file trace_cpu.cc.

References checkAndSchedExitEvent(), gem5::curTick(), DPRINTF, icacheGen, icacheNextEvent, gem5::EventManager::schedule(), and traceStats.

Referenced by TraceCPU().

◆ totalOps()

|

inline |

Return totalOps as the number of committed micro-ops plus the speculatively issued loads that are modelled in the TraceCPU replay.

- Returns

- number of micro-ops i.e. nodes in the elastic data generator

Definition at line 158 of file trace_cpu.hh.

References traceStats.

◆ updateNumOps()

| void gem5::TraceCPU::updateNumOps | ( | uint64_t | rob_num | ) |

Definition at line 88 of file trace_cpu.cc.

References inform, gem5::Named::name(), progressMsgInterval, progressMsgThreshold, and traceStats.

Member Data Documentation

◆ cacheLineSize

|

protected |

Cache the cache line size that we get from the system.

Definition at line 289 of file trace_cpu.hh.

Referenced by TraceCPU().

◆ dataRequestorID

|

protected |

Requestor id for data read and write requests.

Definition at line 301 of file trace_cpu.hh.

Referenced by TraceCPU().

◆ dataTraceFile

|

protected |

Definition at line 304 of file trace_cpu.hh.

Referenced by init(), and TraceCPU().

◆ dcacheGen

|

protected |

Instance of ElasticDataGen to replay data read and write requests.

Definition at line 1019 of file trace_cpu.hh.

Referenced by dcacheRecvTimingResp(), init(), schedDcacheNext(), and TraceCPU().

◆ dcacheNextEvent

|

protected |

Event for the control flow method schedDcacheNext()

Definition at line 1040 of file trace_cpu.hh.

Referenced by dcacheRetryRecvd(), init(), and schedDcacheNextEvent().

◆ dcachePort

|

protected |

Port to connect to L1 data cache.

Definition at line 295 of file trace_cpu.hh.

Referenced by getDataPort(), and TraceCPU().

◆ enableEarlyExit

|

protected |

Exit when any one Trace CPU completes its execution.

If this is configured true then the execCompleteEvent is not scheduled.

Definition at line 1078 of file trace_cpu.hh.

Referenced by checkAndSchedExitEvent(), and init().

◆ execCompleteEvent

|

protected |

A CountedExitEvent which when serviced decrements the counter.

A sim exit event is scheduled when the counter equals zero, that is all instances of Trace CPU have had their execCompleteEvent serviced.

Definition at line 1072 of file trace_cpu.hh.

Referenced by checkAndSchedExitEvent(), and init().

◆ icacheGen

|

protected |

Instance of FixedRetryGen to replay instruction read requests.

Definition at line 1016 of file trace_cpu.hh.

Referenced by init(), schedIcacheNext(), and TraceCPU().

◆ icacheNextEvent

|

protected |

Event for the control flow method schedIcacheNext()

Definition at line 1037 of file trace_cpu.hh.

Referenced by icacheRetryRecvd(), init(), schedIcacheNext(), and TraceCPU().

◆ icachePort

|

protected |

Port to connect to L1 instruction cache.

Definition at line 292 of file trace_cpu.hh.

Referenced by getInstPort(), and TraceCPU().

◆ instRequestorID

|

protected |

Requestor id for instruction read requests.

Definition at line 298 of file trace_cpu.hh.

Referenced by TraceCPU().

◆ instTraceFile

|

protected |

File names for input instruction and data traces.

Definition at line 304 of file trace_cpu.hh.

Referenced by init(), and TraceCPU().

◆ numTraceCPUs

|

staticprotected |

Number of Trace CPUs in the system used as a shared variable and passed to the CountedExitEvent event used for counting down exit events.

It is incremented in the constructor call so that the total is arrived at automatically.

Definition at line 1065 of file trace_cpu.hh.

Referenced by init().

◆ oneTraceComplete

|

protected |

Set to true when one of the generators finishes replaying its trace.

Definition at line 1049 of file trace_cpu.hh.

Referenced by checkAndSchedExitEvent().

◆ progressMsgInterval

|

protected |

Interval of committed instructions specified by the user at which a progress info message is printed.

Definition at line 1084 of file trace_cpu.hh.

Referenced by updateNumOps().

◆ progressMsgThreshold

|

protected |

Definition at line 1091 of file trace_cpu.hh.

Referenced by updateNumOps().

◆ traceOffset

|

protected |

This stores the time offset in the trace, which is taken away from the ready times of requests.

This is specially useful because the time offset can be very large if the traces are generated from the middle of a program.

Definition at line 1057 of file trace_cpu.hh.

Referenced by init().

◆ traceStats

|

protected |

The documentation for this class was generated from the following files:

- cpu/trace/trace_cpu.hh

- cpu/trace/trace_cpu.cc

Generated on Sat Oct 18 2025 08:06:55 for gem5 by doxygen 1.14.0