#include <interrupts.hh>

Public Types | |

| using | Params = X86LocalApicParams |

| Public Types inherited from gem5::BaseInterrupts | |

| using | Params = BaseInterruptsParams |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| int | getInitialApicId () |

| void | setThreadContext (ThreadContext *_tc) override |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Tick | read (PacketPtr pkt) |

| Tick | write (PacketPtr pkt) |

| Tick | recvMessage (PacketPtr pkt) |

| void | completeIPI (PacketPtr pkt) |

| bool | triggerTimerInterrupt () |

| AddrRangeList | getAddrRanges () const |

| AddrRangeList | getIntAddrRange () const |

| void | raiseInterruptPin (int number) |

| void | lowerInterruptPin (int number) |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| uint32_t | readReg (ApicRegIndex miscReg) |

| void | setReg (ApicRegIndex reg, uint32_t val) |

| void | setRegNoEffect (ApicRegIndex reg, uint32_t val) |

| Interrupts (const Params &p) | |

| bool | checkInterrupts () const override |

| bool | checkInterruptsRaw () const |

| Check if there are pending interrupts without ignoring the interrupts disabled flag. | |

| bool | hasPendingUnmaskable () const |

| Check if there are pending unmaskable interrupts. | |

| Fault | getInterrupt () override |

| void | updateIntrInfo () override |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| void | post (int int_num, int index) override |

| void | clear (int int_num, int index) override |

| void | clearAll () override |

| Public Member Functions inherited from gem5::BaseInterrupts | |

| BaseInterrupts (const Params &p) | |

| virtual bool | isWakeUp () const |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Protected Member Functions | |

| BitUnion32 (LVTEntry) Bitfield< 7 | |

| EndBitUnion (LVTEntry) EventFunctionWrapper apicTimerEvent | |

| void | processApicTimerEvent () |

| int | findRegArrayMSB (ApicRegIndex base) |

| void | updateIRRV () |

| void | updateISRV () |

| void | setRegArrayBit (ApicRegIndex base, uint8_t vector) |

| void | clearRegArrayBit (ApicRegIndex base, uint8_t vector) |

| bool | getRegArrayBit (ApicRegIndex base, uint8_t vector) |

| Tick | clockPeriod () const |

| void | requestInterrupt (uint8_t vector, uint8_t deliveryMode, bool level) |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

Protected Attributes | |

| System * | sys = nullptr |

| ClockDomain & | clockDomain |

| uint32_t | regs [NUM_APIC_REGS] = {} |

| vector | |

| Bitfield< 10, 8 > | deliveryMode |

| Bitfield< 12 > | status |

| Bitfield< 13 > | polarity |

| Bitfield< 14 > | remoteIRR |

| Bitfield< 15 > | trigger |

| Bitfield< 16 > | masked |

| Bitfield< 17 > | periodic |

| bool | pendingSmi = false |

| uint8_t | smiVector = 0 |

| bool | pendingNmi = false |

| uint8_t | nmiVector = 0 |

| bool | pendingExtInt = false |

| uint8_t | extIntVector = 0 |

| bool | pendingInit = false |

| uint8_t | initVector = 0 |

| bool | pendingStartup = false |

| uint8_t | startupVector = 0 |

| bool | startedUp = false |

| bool | pendingUnmaskableInt = false |

| int | pendingIPIs = 0 |

| uint8_t | IRRV = 0 |

| uint8_t | ISRV = 0 |

| int | initialApicId = 0 |

| IntResponsePort< Interrupts > | intResponsePort |

| IntRequestPort< Interrupts > | intRequestPort |

| IntSinkPin< Interrupts > | lint0Pin |

| IntSinkPin< Interrupts > | lint1Pin |

| PioPort< Interrupts > | pioPort |

| Tick | pioDelay = 0 |

| Addr | pioAddr = MaxAddr |

| Protected Attributes inherited from gem5::BaseInterrupts | |

| ThreadContext * | tc = nullptr |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

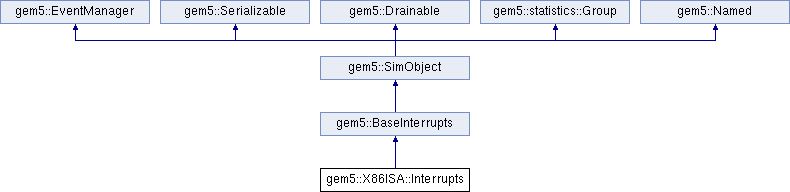

Detailed Description

Definition at line 78 of file interrupts.hh.

Member Typedef Documentation

◆ Params

| using gem5::X86ISA::Interrupts::Params = X86LocalApicParams |

Definition at line 201 of file interrupts.hh.

Constructor & Destructor Documentation

◆ Interrupts()

| gem5::X86ISA::Interrupts::Interrupts | ( | const Params & | p | ) |

Definition at line 635 of file interrupts.cc.

References gem5::BaseInterrupts::BaseInterrupts(), clockDomain, gem5::X86ISA::p, processApicTimerEvent(), sys, and gem5::X86ISA::system.

Member Function Documentation

◆ BitUnion32()

|

protected |

◆ checkInterrupts()

|

overridevirtual |

Implements gem5::BaseInterrupts.

Definition at line 666 of file interrupts.cc.

References gem5::X86ISA::APIC_TASK_PRIORITY, gem5::bits(), DPRINTF, IRRV, ISRV, pendingExtInt, pendingUnmaskableInt, regs, gem5::X86ISA::misc_reg::Rflags, and gem5::BaseInterrupts::tc.

Referenced by getInterrupt(), and updateIntrInfo().

◆ checkInterruptsRaw()

| bool gem5::X86ISA::Interrupts::checkInterruptsRaw | ( | ) | const |

Check if there are pending interrupts without ignoring the interrupts disabled flag.

- Returns

- true if there are interrupts pending.

Definition at line 688 of file interrupts.cc.

References gem5::X86ISA::APIC_TASK_PRIORITY, gem5::bits(), IRRV, ISRV, pendingExtInt, pendingUnmaskableInt, and regs.

◆ clear()

|

inlineoverridevirtual |

Reimplemented from gem5::BaseInterrupts.

Definition at line 308 of file interrupts.hh.

References gem5::X86ISA::index, and panic.

◆ clearAll()

|

inlineoverridevirtual |

Reimplemented from gem5::BaseInterrupts.

Definition at line 314 of file interrupts.hh.

References panic.

◆ clearRegArrayBit()

|

inlineprotected |

Definition at line 163 of file interrupts.hh.

References gem5::X86ISA::base, regs, and vector.

Referenced by requestInterrupt(), setReg(), and updateIntrInfo().

◆ clockPeriod()

|

inlineprotected |

Definition at line 174 of file interrupts.hh.

References clockDomain.

◆ completeIPI()

| void gem5::X86ISA::Interrupts::completeIPI | ( | PacketPtr | pkt | ) |

Definition at line 369 of file interrupts.cc.

References gem5::X86ISA::APIC_INTERRUPT_COMMAND_LOW, DPRINTF, pendingIPIs, and regs.

◆ EndBitUnion()

|

protected |

References EndBitUnion(), and processApicTimerEvent().

Referenced by EndBitUnion().

◆ findRegArrayMSB()

|

inlineprotected |

Definition at line 133 of file interrupts.hh.

References gem5::X86ISA::base, gem5::findMsbSet(), findRegArrayMSB(), gem5::X86ISA::offset, and regs.

Referenced by findRegArrayMSB(), updateIRRV(), and updateISRV().

◆ getAddrRanges()

| AddrRangeList gem5::X86ISA::Interrupts::getAddrRanges | ( | ) | const |

Definition at line 383 of file interrupts.cc.

References gem5::X86ISA::PageBytes, pioAddr, gem5::RangeSize(), and gem5::BaseInterrupts::tc.

◆ getInitialApicId()

|

inline |

Definition at line 196 of file interrupts.hh.

References initialApicId.

◆ getIntAddrRange()

| AddrRangeList gem5::X86ISA::Interrupts::getIntAddrRange | ( | ) | const |

Definition at line 393 of file interrupts.cc.

References initialApicId, gem5::X86ISA::PhysAddrAPICRangeSize, gem5::RangeEx(), and gem5::X86ISA::x86InterruptAddress().

◆ getInterrupt()

|

overridevirtual |

Implements gem5::BaseInterrupts.

Definition at line 696 of file interrupts.cc.

References checkInterrupts(), DPRINTF, extIntVector, initVector, IRRV, nmiVector, gem5::NoFault, panic, pendingExtInt, pendingInit, pendingNmi, pendingSmi, pendingStartup, pendingUnmaskableInt, and startupVector.

◆ getPort()

|

inlineoverridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

gem5 has a request and response port interface. All memory objects are connected together via ports. These ports provide a rigid interface between these memory objects. These ports implement three different memory system modes: timing, atomic, and functional. The most important mode is the timing mode and here timing mode is used for conducting cycle-level timing experiments. The other modes are only used in special circumstances and should not be used to conduct cycle-level timing experiments. The other modes are only used in special circumstances. These ports allow SimObjects to communicate with each other.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from gem5::SimObject.

Definition at line 234 of file interrupts.hh.

References gem5::SimObject::getPort(), intRequestPort, intResponsePort, gem5::InvalidPortID, lint0Pin, lint1Pin, and pioPort.

◆ getRegArrayBit()

|

inlineprotected |

Definition at line 169 of file interrupts.hh.

References gem5::X86ISA::base, gem5::bits(), regs, and vector.

Referenced by requestInterrupt().

◆ hasPendingUnmaskable()

|

inline |

Check if there are pending unmaskable interrupts.

- Returns

- true there are unmaskable interrupts pending.

Definition at line 287 of file interrupts.hh.

References pendingUnmaskableInt.

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Definition at line 328 of file interrupts.cc.

References intRequestPort, intResponsePort, gem5::Named::name(), panic_if, and pioPort.

◆ lowerInterruptPin()

| void gem5::X86ISA::Interrupts::lowerInterruptPin | ( | int | number | ) |

Definition at line 303 of file interrupts.cc.

◆ post()

|

inlineoverridevirtual |

Reimplemented from gem5::BaseInterrupts.

Definition at line 302 of file interrupts.hh.

References gem5::X86ISA::index, and panic.

◆ processApicTimerEvent()

|

protected |

Definition at line 822 of file interrupts.cc.

References gem5::X86ISA::APIC_INITIAL_COUNT, readReg(), setReg(), and triggerTimerInterrupt().

Referenced by EndBitUnion(), and Interrupts().

◆ raiseInterruptPin()

| void gem5::X86ISA::Interrupts::raiseInterruptPin | ( | int | number | ) |

Definition at line 278 of file interrupts.cc.

References gem5::X86ISA::APIC_LVT_LINT0, gem5::X86ISA::APIC_LVT_LINT1, gem5::X86ISA::buildIntAcknowledgePacket(), gem5::MipsISA::dm, DPRINTF, gem5::Packet::getLE(), intRequestPort, panic_if, regs, requestInterrupt(), sys, and trigger.

◆ read()

Definition at line 194 of file interrupts.cc.

References gem5::X86ISA::decodeAddr(), DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getSize(), gem5::htole(), gem5::Packet::makeAtomicResponse(), gem5::X86ISA::mask, gem5::X86ISA::offset, panic, pioAddr, pioDelay, readReg(), gem5::X86ISA::reg, gem5::Packet::setData(), and gem5::X86ISA::val.

◆ readReg()

| uint32_t gem5::X86ISA::Interrupts::readReg | ( | ApicRegIndex | miscReg | ) |

Definition at line 404 of file interrupts.cc.

References gem5::X86ISA::APIC_ARBITRATION_PRIORITY, gem5::X86ISA::APIC_CURRENT_COUNT, gem5::X86ISA::APIC_DIVIDE_CONFIGURATION, gem5::X86ISA::APIC_ERROR_STATUS, gem5::X86ISA::APIC_INTERNAL_STATE, gem5::X86ISA::APIC_PROCESSOR_PRIORITY, gem5::X86ISA::APIC_TRIGGER_MODE(), clockPeriod(), gem5::curTick(), gem5::divideFromConf(), panic, gem5::X86ISA::reg, regs, and gem5::X86ISA::val.

Referenced by processApicTimerEvent(), and read().

◆ recvMessage()

Definition at line 341 of file interrupts.cc.

References gem5::Packet::cmd, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getRaw(), initialApicId, gem5::Packet::makeAtomicResponse(), gem5::X86ISA::offset, panic, pioDelay, requestInterrupt(), gem5::MemCmd::WriteReq, and gem5::X86ISA::x86InterruptAddress().

◆ requestInterrupt()

|

protected |

Definition at line 228 of file interrupts.cc.

References gem5::X86ISA::APIC_INTERRUPT_REQUEST_BASE, gem5::X86ISA::APIC_TRIGGER_MODE_BASE, clearRegArrayBit(), deliveryMode, DPRINTF, extIntVector, gem5::FullSystem, getRegArrayBit(), initVector, IRRV, gem5::X86ISA::level, nmiVector, pendingExtInt, pendingInit, pendingNmi, pendingSmi, pendingStartup, pendingUnmaskableInt, setRegArrayBit(), smiVector, startedUp, startupVector, gem5::BaseInterrupts::tc, and vector.

Referenced by raiseInterruptPin(), recvMessage(), setReg(), and triggerTimerInterrupt().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 765 of file interrupts.cc.

References extIntVector, initVector, IRRV, ISRV, nmiVector, gem5::X86ISA::NUM_APIC_REGS, pendingExtInt, pendingInit, pendingIPIs, pendingNmi, pendingSmi, pendingStartup, pendingUnmaskableInt, regs, SERIALIZE_ARRAY, SERIALIZE_SCALAR, smiVector, startedUp, and startupVector.

◆ setReg()

| void gem5::X86ISA::Interrupts::setReg | ( | ApicRegIndex | reg, |

| uint32_t | val ) |

Definition at line 442 of file interrupts.cc.

References gem5::X86ISA::APIC_ARBITRATION_PRIORITY, gem5::X86ISA::APIC_CURRENT_COUNT, gem5::X86ISA::APIC_DESTINATION_FORMAT, gem5::X86ISA::APIC_DIVIDE_CONFIGURATION, gem5::X86ISA::APIC_EOI, gem5::X86ISA::APIC_ERROR_STATUS, gem5::X86ISA::APIC_ID, gem5::X86ISA::APIC_IN_SERVICE(), gem5::X86ISA::APIC_IN_SERVICE_BASE, gem5::X86ISA::APIC_INITIAL_COUNT, gem5::X86ISA::APIC_INTERNAL_STATE, gem5::X86ISA::APIC_INTERRUPT_COMMAND_HIGH, gem5::X86ISA::APIC_INTERRUPT_COMMAND_LOW, gem5::X86ISA::APIC_INTERRUPT_REQUEST(), gem5::X86ISA::APIC_LOGICAL_DESTINATION, gem5::X86ISA::APIC_LVT_ERROR, gem5::X86ISA::APIC_LVT_LINT0, gem5::X86ISA::APIC_LVT_LINT1, gem5::X86ISA::APIC_LVT_PERFORMANCE_MONITORING_COUNTERS, gem5::X86ISA::APIC_LVT_THERMAL_SENSOR, gem5::X86ISA::APIC_LVT_TIMER, gem5::X86ISA::APIC_PROCESSOR_PRIORITY, gem5::X86ISA::APIC_SPURIOUS_INTERRUPT_VECTOR, gem5::X86ISA::APIC_TASK_PRIORITY, gem5::X86ISA::APIC_TRIGGER_MODE(), gem5::X86ISA::APIC_VERSION, gem5::bits(), gem5::X86ISA::buildIntTriggerPacket(), clearRegArrayBit(), clockPeriod(), gem5::curTick(), gem5::divideFromConf(), hack_once, gem5::ArmISA::i, initialApicId, intRequestPort, ISRV, gem5::X86ISA::offset, panic, pendingIPIs, gem5::X86ISA::reg, regs, requestInterrupt(), gem5::EventManager::reschedule(), sys, updateISRV(), gem5::X86ISA::val, and warn.

Referenced by processApicTimerEvent(), and write().

◆ setRegArrayBit()

|

inlineprotected |

Definition at line 157 of file interrupts.hh.

References gem5::X86ISA::base, regs, and vector.

Referenced by requestInterrupt(), and updateIntrInfo().

◆ setRegNoEffect()

|

inline |

Definition at line 259 of file interrupts.hh.

References gem5::X86ISA::reg, regs, and gem5::X86ISA::val.

◆ setThreadContext()

|

overridevirtual |

Reimplemented from gem5::BaseInterrupts.

Definition at line 312 of file interrupts.cc.

References gem5::X86ISA::APIC_ID, gem5::ThreadContext::cpuId(), initialApicId, panic_if, pioAddr, regs, gem5::BaseInterrupts::setThreadContext(), gem5::BaseInterrupts::tc, and gem5::X86ISA::x86LocalAPICAddress().

◆ triggerTimerInterrupt()

|

inline |

Definition at line 219 of file interrupts.hh.

References gem5::X86ISA::APIC_LVT_TIMER, regs, and requestInterrupt().

Referenced by processApicTimerEvent().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 790 of file interrupts.cc.

References extIntVector, initVector, IRRV, ISRV, nmiVector, gem5::X86ISA::NUM_APIC_REGS, pendingExtInt, pendingInit, pendingIPIs, pendingNmi, pendingSmi, pendingStartup, pendingUnmaskableInt, regs, gem5::EventManager::reschedule(), gem5::EventManager::schedule(), smiVector, startedUp, startupVector, UNSERIALIZE_ARRAY, and UNSERIALIZE_SCALAR.

◆ updateIntrInfo()

|

overridevirtual |

Implements gem5::BaseInterrupts.

Definition at line 730 of file interrupts.cc.

References gem5::X86ISA::APIC_IN_SERVICE_BASE, gem5::X86ISA::APIC_INTERRUPT_REQUEST_BASE, checkInterrupts(), clearRegArrayBit(), DPRINTF, IRRV, ISRV, pendingExtInt, pendingInit, pendingNmi, pendingSmi, pendingStartup, pendingUnmaskableInt, setRegArrayBit(), startedUp, and updateIRRV().

◆ updateIRRV()

|

inlineprotected |

Definition at line 145 of file interrupts.hh.

References gem5::X86ISA::APIC_INTERRUPT_REQUEST_BASE, findRegArrayMSB(), and IRRV.

Referenced by updateIntrInfo().

◆ updateISRV()

|

inlineprotected |

Definition at line 151 of file interrupts.hh.

References gem5::X86ISA::APIC_IN_SERVICE_BASE, findRegArrayMSB(), and ISRV.

Referenced by setReg().

◆ write()

Definition at line 211 of file interrupts.cc.

References gem5::X86ISA::decodeAddr(), DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getSize(), gem5::letoh(), gem5::Packet::makeAtomicResponse(), gem5::X86ISA::mask, gem5::X86ISA::offset, panic, pioAddr, pioDelay, gem5::X86ISA::reg, regs, setReg(), gem5::X86ISA::val, and gem5::Packet::writeData().

Member Data Documentation

◆ clockDomain

|

protected |

Definition at line 82 of file interrupts.hh.

Referenced by clockPeriod(), and Interrupts().

◆ deliveryMode

|

protected |

Definition at line 89 of file interrupts.hh.

Referenced by requestInterrupt().

◆ extIntVector

|

protected |

Definition at line 113 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), and unserialize().

◆ initialApicId

|

protected |

Definition at line 178 of file interrupts.hh.

Referenced by getInitialApicId(), getIntAddrRange(), recvMessage(), setReg(), and setThreadContext().

◆ initVector

|

protected |

Definition at line 115 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), and unserialize().

◆ intRequestPort

|

protected |

Definition at line 182 of file interrupts.hh.

Referenced by getPort(), init(), raiseInterruptPin(), and setReg().

◆ intResponsePort

|

protected |

Definition at line 181 of file interrupts.hh.

◆ IRRV

|

protected |

Definition at line 129 of file interrupts.hh.

Referenced by checkInterrupts(), checkInterruptsRaw(), getInterrupt(), requestInterrupt(), serialize(), unserialize(), updateIntrInfo(), and updateIRRV().

◆ ISRV

|

protected |

Definition at line 130 of file interrupts.hh.

Referenced by checkInterrupts(), checkInterruptsRaw(), serialize(), setReg(), unserialize(), updateIntrInfo(), and updateISRV().

◆ lint0Pin

|

protected |

Definition at line 185 of file interrupts.hh.

Referenced by getPort().

◆ lint1Pin

|

protected |

Definition at line 186 of file interrupts.hh.

Referenced by getPort().

◆ masked

|

protected |

Definition at line 94 of file interrupts.hh.

◆ nmiVector

|

protected |

Definition at line 111 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), and unserialize().

◆ pendingExtInt

|

protected |

Definition at line 112 of file interrupts.hh.

Referenced by checkInterrupts(), checkInterruptsRaw(), getInterrupt(), requestInterrupt(), serialize(), unserialize(), and updateIntrInfo().

◆ pendingInit

|

protected |

Definition at line 114 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), unserialize(), and updateIntrInfo().

◆ pendingIPIs

|

protected |

Definition at line 124 of file interrupts.hh.

Referenced by completeIPI(), serialize(), setReg(), and unserialize().

◆ pendingNmi

|

protected |

Definition at line 110 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), unserialize(), and updateIntrInfo().

◆ pendingSmi

|

protected |

Definition at line 108 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), unserialize(), and updateIntrInfo().

◆ pendingStartup

|

protected |

Definition at line 116 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), unserialize(), and updateIntrInfo().

◆ pendingUnmaskableInt

|

protected |

Definition at line 121 of file interrupts.hh.

Referenced by checkInterrupts(), checkInterruptsRaw(), getInterrupt(), hasPendingUnmaskable(), requestInterrupt(), serialize(), unserialize(), and updateIntrInfo().

◆ periodic

|

protected |

Definition at line 95 of file interrupts.hh.

◆ pioAddr

Definition at line 192 of file interrupts.hh.

Referenced by getAddrRanges(), read(), setThreadContext(), and write().

◆ pioDelay

|

protected |

Definition at line 191 of file interrupts.hh.

Referenced by read(), recvMessage(), and write().

◆ pioPort

|

protected |

Definition at line 189 of file interrupts.hh.

◆ polarity

|

protected |

Definition at line 91 of file interrupts.hh.

◆ regs

|

protected |

Definition at line 85 of file interrupts.hh.

Referenced by checkInterrupts(), checkInterruptsRaw(), clearRegArrayBit(), completeIPI(), findRegArrayMSB(), getRegArrayBit(), raiseInterruptPin(), readReg(), serialize(), setReg(), setRegArrayBit(), setRegNoEffect(), setThreadContext(), triggerTimerInterrupt(), unserialize(), and write().

◆ remoteIRR

|

protected |

Definition at line 92 of file interrupts.hh.

◆ smiVector

|

protected |

Definition at line 109 of file interrupts.hh.

Referenced by requestInterrupt(), serialize(), and unserialize().

◆ startedUp

|

protected |

Definition at line 118 of file interrupts.hh.

Referenced by requestInterrupt(), serialize(), unserialize(), and updateIntrInfo().

◆ startupVector

|

protected |

Definition at line 117 of file interrupts.hh.

Referenced by getInterrupt(), requestInterrupt(), serialize(), and unserialize().

◆ status

|

protected |

Definition at line 90 of file interrupts.hh.

◆ sys

|

protected |

Definition at line 81 of file interrupts.hh.

Referenced by Interrupts(), raiseInterruptPin(), and setReg().

◆ trigger

|

protected |

Definition at line 93 of file interrupts.hh.

Referenced by raiseInterruptPin().

◆ vector

|

protected |

Definition at line 88 of file interrupts.hh.

Referenced by clearRegArrayBit(), getRegArrayBit(), requestInterrupt(), and setRegArrayBit().

The documentation for this class was generated from the following files:

- arch/x86/interrupts.hh

- arch/x86/interrupts.cc

Generated on Sat Oct 18 2025 08:07:52 for gem5 by doxygen 1.14.0