#include <indirect_memory.hh>

Classes | |

| struct | IndirectPatternDetectorEntry |

| Indirect Pattern Detector entrt. More... | |

| struct | PrefetchTableEntry |

| Prefetch Table Entry. More... | |

Public Member Functions | |

| IndirectMemory (const IndirectMemoryPrefetcherParams &p) | |

| ~IndirectMemory ()=default | |

| void | calculatePrefetch (const PrefetchInfo &pfi, std::vector< AddrPriority > &addresses, const CacheAccessor &cache) override |

| Public Member Functions inherited from gem5::prefetch::Queued | |

| Queued (const QueuedPrefetcherParams &p) | |

| virtual | ~Queued () |

| void | notify (const CacheAccessProbeArg &acc, const PrefetchInfo &pfi) override |

| Notify prefetcher of cache access (may be any access or just misses, depending on cache parameters.) | |

| void | insert (const PacketPtr &pkt, PrefetchInfo &new_pfi, int32_t priority, const CacheAccessor &cache) |

| PacketPtr | getPacket () override |

| Tick | nextPrefetchReadyTime () const override |

| void | printQueue (const std::list< DeferredPacket > &queue) const |

| Public Member Functions inherited from gem5::prefetch::Base | |

| Base (const BasePrefetcherParams &p) | |

| virtual | ~Base ()=default |

| virtual void | setParentInfo (System *sys, ProbeManager *pm, unsigned blk_size) |

| virtual void | notifyFill (const CacheAccessProbeArg &acc) |

| Notify prefetcher of cache fill. | |

| virtual void | notifyEvict (const EvictionInfo &info) |

| Notify prefetcher of cache eviction. | |

| void | prefetchUnused () |

| void | incrDemandMhsrMisses () |

| void | pfHitInCache () |

| void | pfHitInMSHR () |

| void | pfHitInWB () |

| void | regProbeListeners () override |

| Register probe points for this object. | |

| void | probeNotify (const CacheAccessProbeArg &acc, bool miss) |

| Process a notification event from the ProbeListener. | |

| void | addEventProbe (SimObject *obj, const char *name) |

| Add a SimObject and a probe name to listen events from. | |

| void | addMMU (BaseMMU *mmu) |

| Add a BaseMMU object to be used whenever a translation is needed. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Private Member Functions | |

| void | allocateOrUpdateIPDEntry (const PrefetchTableEntry *pt_entry, int64_t index) |

| Allocate or update an entry in the IPD. | |

| void | trackMissIndex1 (Addr miss_addr) |

| Update an IPD entry with a detected miss address, when the first index is being tracked. | |

| void | trackMissIndex2 (Addr miss_addr) |

| Update an IPD entry with a detected miss address, when the second index is being tracked. | |

| void | checkAccessMatchOnActiveEntries (Addr addr) |

| Checks if an access to the cache matches any active PT entry, if so, the indirect confidence counter is incremented. | |

Private Attributes | |

| const unsigned int | maxPrefetchDistance |

| Maximum number of prefetches generated per event. | |

| const std::vector< int > | shiftValues |

| Shift values considered. | |

| const unsigned int | prefetchThreshold |

| Counter threshold to start prefetching. | |

| const int | streamCounterThreshold |

| streamCounter value to trigger the streaming prefetcher | |

| const int | streamingDistance |

| Number of prefetches generated when using the streaming prefetcher. | |

| AssociativeCache< PrefetchTableEntry > | prefetchTable |

| Prefetch table. | |

| AssociativeCache< IndirectPatternDetectorEntry > | ipd |

| Indirect Pattern Detector (IPD) table. | |

| IndirectPatternDetectorEntry * | ipdEntryTrackingMisses |

| Entry currently tracking misses. | |

| const ByteOrder | byteOrder |

| Byte order used to access the cache. | |

Additional Inherited Members | |

| Public Types inherited from gem5::prefetch::Queued | |

| using | AddrPriority = std::pair<Addr, int32_t> |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| Protected Types inherited from gem5::prefetch::Queued | |

| using | const_iterator = std::list<DeferredPacket>::const_iterator |

| using | iterator = std::list<DeferredPacket>::iterator |

| Protected Member Functions inherited from gem5::prefetch::Base | |

| bool | observeAccess (const PacketPtr &pkt, bool miss, bool prefetched) const |

| Determine if this access should be observed. | |

| bool | samePage (Addr a, Addr b) const |

| Determine if addresses are on the same page. | |

| Addr | blockAddress (Addr a) const |

| Determine the address of the block in which a lays. | |

| Addr | blockIndex (Addr a) const |

| Determine the address of a at block granularity. | |

| Addr | pageAddress (Addr a) const |

| Determine the address of the page in which a lays. | |

| Addr | pageOffset (Addr a) const |

| Determine the page-offset of a. | |

| Addr | pageIthBlockAddress (Addr page, uint32_t i) const |

| Build the address of the i-th block inside the page. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

| Protected Attributes inherited from gem5::prefetch::Queued | |

| std::list< DeferredPacket > | pfq |

| std::list< DeferredPacket > | pfqMissingTranslation |

| const unsigned | queueSize |

| Maximum size of the prefetch queue. | |

| const unsigned | missingTranslationQueueSize |

| Maximum size of the queue holding prefetch requests with missing address translations. | |

| const Cycles | latency |

| Cycles after generation when a prefetch can first be issued. | |

| const bool | queueSquash |

| Squash queued prefetch if demand access observed. | |

| const bool | queueFilter |

| Filter prefetches if already queued. | |

| const bool | cacheSnoop |

| Snoop the cache before generating prefetch (cheating basically) | |

| const bool | tagPrefetch |

| Tag prefetch with PC of generating access? | |

| const unsigned int | throttleControlPct |

| Percentage of requests that can be throttled. | |

| gem5::prefetch::Queued::QueuedStats | statsQueued |

| Protected Attributes inherited from gem5::prefetch::Base | |

| System * | system |

| Pointer to the parent system. | |

| ProbeManager * | probeManager |

| Pointer to the parent cache's probe manager. | |

| unsigned | blkSize |

| The block size of the parent cache. | |

| unsigned | lBlkSize |

| log_2(block size of the parent cache). | |

| const bool | onMiss |

| Only consult prefetcher on cache misses? | |

| const bool | onRead |

| Consult prefetcher on reads? | |

| const bool | onWrite |

| Consult prefetcher on reads? | |

| const bool | onData |

| Consult prefetcher on data accesses? | |

| const bool | onInst |

| Consult prefetcher on instruction accesses? | |

| const RequestorID | requestorId |

| Request id for prefetches. | |

| const Addr | pageBytes |

| const bool | prefetchOnAccess |

| Prefetch on every access, not just misses. | |

| const bool | prefetchOnPfHit |

| Prefetch on hit on prefetched lines. | |

| const bool | useVirtualAddresses |

| Use Virtual Addresses for prefetching. | |

| gem5::prefetch::Base::StatGroup | prefetchStats |

| uint64_t | issuedPrefetches |

| Total prefetches issued. | |

| uint64_t | usefulPrefetches |

| Total prefetches that has been useful. | |

| BaseMMU * | mmu |

| Registered mmu for address translations. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

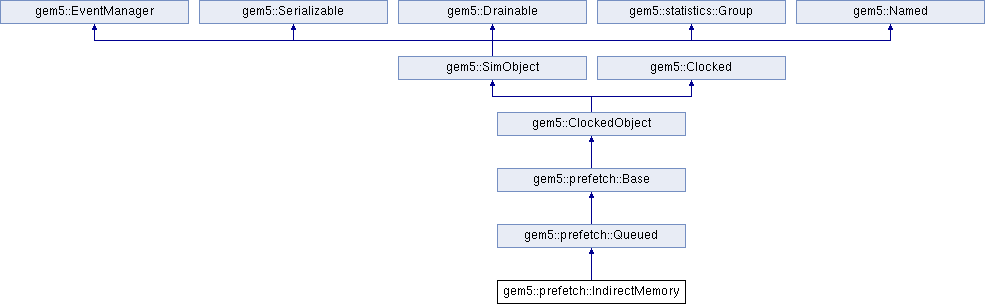

Detailed Description

Definition at line 57 of file indirect_memory.hh.

Constructor & Destructor Documentation

◆ IndirectMemory()

| gem5::prefetch::IndirectMemory::IndirectMemory | ( | const IndirectMemoryPrefetcherParams & | p | ) |

Definition at line 40 of file indirect_memory.cc.

References byteOrder, gem5::genTagExtractor(), ipd, ipdEntryTrackingMisses, maxPrefetchDistance, gem5::Named::name(), gem5::MipsISA::p, prefetchTable, prefetchThreshold, gem5::prefetch::Queued::Queued(), shiftValues, streamCounterThreshold, and streamingDistance.

◆ ~IndirectMemory()

|

default |

Member Function Documentation

◆ allocateOrUpdateIPDEntry()

|

private |

Allocate or update an entry in the IPD.

- Parameters

-

pt_entry Pointer to the associated page table entry index Detected first index value

Definition at line 172 of file indirect_memory.cc.

References gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::idx1, gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::idx2, gem5::MipsISA::index, ipd, ipdEntryTrackingMisses, and gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::secondIndexSet.

Referenced by calculatePrefetch().

◆ calculatePrefetch()

|

overridevirtual |

Implements gem5::prefetch::Queued.

Definition at line 63 of file indirect_memory.cc.

References gem5::X86ISA::addr, gem5::prefetch::IndirectMemory::PrefetchTableEntry::address, allocateOrUpdateIPDEntry(), gem5::prefetch::IndirectMemory::PrefetchTableEntry::baseAddr, byteOrder, gem5::GenericSatCounter< T >::calcSaturation(), checkAccessMatchOnActiveEntries(), gem5::prefetch::IndirectMemory::PrefetchTableEntry::enabled, gem5::prefetch::Base::PrefetchInfo::get(), gem5::prefetch::Base::PrefetchInfo::getAddr(), gem5::prefetch::Base::PrefetchInfo::getPC(), gem5::prefetch::Base::PrefetchInfo::getSize(), gem5::prefetch::Base::PrefetchInfo::hasPC(), gem5::ArmISA::i, gem5::prefetch::IndirectMemory::PrefetchTableEntry::increasedIndirectCounter, gem5::MipsISA::index, gem5::prefetch::IndirectMemory::PrefetchTableEntry::index, gem5::prefetch::IndirectMemory::PrefetchTableEntry::indirectCounter, ipdEntryTrackingMisses, gem5::prefetch::Base::PrefetchInfo::isCacheMiss(), gem5::prefetch::Base::PrefetchInfo::isSecure(), gem5::prefetch::Base::PrefetchInfo::isWrite(), maxPrefetchDistance, gem5::MipsISA::pc, prefetchTable, prefetchThreshold, gem5::prefetch::IndirectMemory::PrefetchTableEntry::secure, gem5::prefetch::IndirectMemory::PrefetchTableEntry::shift, gem5::prefetch::IndirectMemory::PrefetchTableEntry::streamCounter, streamCounterThreshold, streamingDistance, trackMissIndex1(), and trackMissIndex2().

◆ checkAccessMatchOnActiveEntries()

|

private |

Checks if an access to the cache matches any active PT entry, if so, the indirect confidence counter is incremented.

- Parameters

-

addr address of the access

Definition at line 254 of file indirect_memory.cc.

References gem5::X86ISA::addr, and prefetchTable.

Referenced by calculatePrefetch().

◆ trackMissIndex1()

|

private |

Update an IPD entry with a detected miss address, when the first index is being tracked.

- Parameters

-

miss_addr The address that caused the miss

Definition at line 202 of file indirect_memory.cc.

References gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::baseAddr, gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::idx1, ipdEntryTrackingMisses, gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::numMisses, gem5::ArmISA::shift, and shiftValues.

Referenced by calculatePrefetch().

◆ trackMissIndex2()

|

private |

Update an IPD entry with a detected miss address, when the second index is being tracked.

- Parameters

-

miss_addr The address that caused the miss

Definition at line 221 of file indirect_memory.cc.

References gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::baseAddr, gem5::prefetch::IndirectMemory::PrefetchTableEntry::baseAddr, gem5::prefetch::IndirectMemory::PrefetchTableEntry::enabled, gem5::TaggedEntry::getTag(), gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::idx2, gem5::prefetch::IndirectMemory::PrefetchTableEntry::indirectCounter, ipd, ipdEntryTrackingMisses, gem5::prefetch::IndirectMemory::IndirectPatternDetectorEntry::numMisses, gem5::GenericSatCounter< T >::reset(), gem5::ArmISA::shift, gem5::prefetch::IndirectMemory::PrefetchTableEntry::shift, and shiftValues.

Referenced by calculatePrefetch().

Member Data Documentation

◆ byteOrder

|

private |

Byte order used to access the cache.

Definition at line 174 of file indirect_memory.hh.

Referenced by calculatePrefetch(), and IndirectMemory().

◆ ipd

|

private |

Indirect Pattern Detector (IPD) table.

Definition at line 168 of file indirect_memory.hh.

Referenced by allocateOrUpdateIPDEntry(), IndirectMemory(), and trackMissIndex2().

◆ ipdEntryTrackingMisses

|

private |

Entry currently tracking misses.

Definition at line 171 of file indirect_memory.hh.

Referenced by allocateOrUpdateIPDEntry(), calculatePrefetch(), IndirectMemory(), trackMissIndex1(), and trackMissIndex2().

◆ maxPrefetchDistance

|

private |

Maximum number of prefetches generated per event.

Definition at line 60 of file indirect_memory.hh.

Referenced by calculatePrefetch(), and IndirectMemory().

◆ prefetchTable

|

private |

Prefetch table.

Definition at line 127 of file indirect_memory.hh.

Referenced by calculatePrefetch(), checkAccessMatchOnActiveEntries(), and IndirectMemory().

◆ prefetchThreshold

|

private |

Counter threshold to start prefetching.

Definition at line 64 of file indirect_memory.hh.

Referenced by calculatePrefetch(), and IndirectMemory().

◆ shiftValues

|

private |

Shift values considered.

Definition at line 62 of file indirect_memory.hh.

Referenced by IndirectMemory(), trackMissIndex1(), and trackMissIndex2().

◆ streamCounterThreshold

|

private |

streamCounter value to trigger the streaming prefetcher

Definition at line 66 of file indirect_memory.hh.

Referenced by calculatePrefetch(), and IndirectMemory().

◆ streamingDistance

|

private |

Number of prefetches generated when using the streaming prefetcher.

Definition at line 68 of file indirect_memory.hh.

Referenced by calculatePrefetch(), and IndirectMemory().

The documentation for this class was generated from the following files:

- mem/cache/prefetch/indirect_memory.hh

- mem/cache/prefetch/indirect_memory.cc

Generated on Sat Oct 18 2025 08:07:01 for gem5 by doxygen 1.14.0