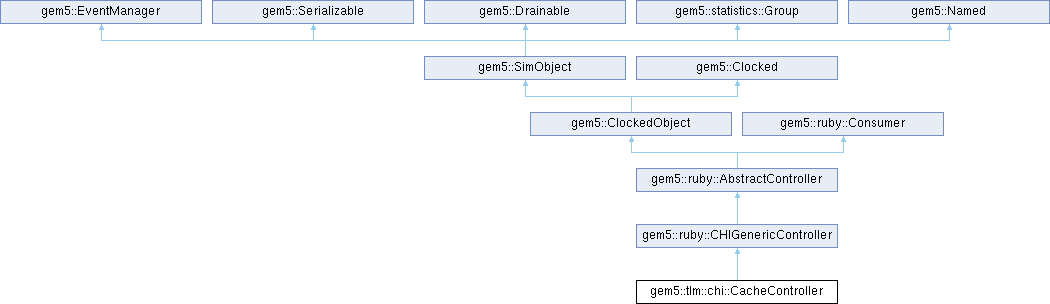

The tlm::chi::CacheController is a ruby CacheController which acts as a bridge between the AMBA TLM 2.0 implementation of CHI 1 with the gem5 (ruby) one. More...

#include <controller.hh>

Classes | |

| struct | DatalessTransaction |

| struct | ReadTransaction |

| struct | Transaction |

| struct | WriteTransaction |

Public Member Functions | |

| PARAMS (TlmController) | |

| CacheController (const Params &p) | |

| bool | recvRequestMsg (const CHIRequestMsg *msg) override |

| bool | recvSnoopMsg (const CHIRequestMsg *msg) override |

| bool | recvResponseMsg (const CHIResponseMsg *msg) override |

| bool | recvDataMsg (const CHIDataMsg *msg) override |

| void | sendMsg (ARM::CHI::Payload &payload, ARM::CHI::Phase &phase) |

| void | sendRequestMsg (ARM::CHI::Payload &payload, ARM::CHI::Phase &phase) |

| void | sendResponseMsg (ARM::CHI::Payload &payload, ARM::CHI::Phase &phase) |

| void | sendCompAck (ARM::CHI::Payload &payload, ARM::CHI::Phase &phase) |

| void | sendDataMsg (ARM::CHI::Payload &payload, ARM::CHI::Phase &phase) |

| Addr | reqAddr (ARM::CHI::Payload &payload, ARM::CHI::Phase &phase) const |

| Addr | reqSize (ARM::CHI::Payload &payload, ARM::CHI::Phase &phase) const |

| void | pCreditGrant (const CHIResponseMsg *msg) |

| Public Member Functions inherited from gem5::ruby::CHIGenericController | |

| PARAMS (CHIGenericController) | |

| CHIGenericController (const Params &p) | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| MessageBuffer * | getMandatoryQueue () const override |

| MessageBuffer * | getMemReqQueue () const override |

| MessageBuffer * | getMemRespQueue () const override |

| void | initNetQueues () override |

| Initialize the message buffers. | |

| void | print (std::ostream &out) const override |

| void | wakeup () override |

| void | resetStats () override |

| Callback to reset stats. | |

| void | regStats () override |

| Callback to set stat parameters. | |

| void | collateStats () override |

| Function for collating statistics from all the controllers of this particular type. | |

| void | recordCacheTrace (int cntrl, CacheRecorder *tr) override |

| Sequencer * | getCPUSequencer () const override |

| DMASequencer * | getDMASequencer () const override |

| GPUCoalescer * | getGPUCoalescer () const override |

| void | addSequencer (RubyPort *seq) |

| bool | functionalReadBuffers (PacketPtr &) override |

| These functions are used by ruby system to read/write the data blocks that exist with in the controller. | |

| bool | functionalReadBuffers (PacketPtr &, WriteMask &) override |

| Functional read that reads only blocks not present in the mask. | |

| int | functionalWriteBuffers (PacketPtr &) override |

| The return value indicates the number of messages written with the data from the packet. | |

| AccessPermission | getAccessPermission (const Addr ¶m_addr) override |

| void | functionalRead (const Addr ¶m_addr, Packet *param_pkt, WriteMask ¶m_mask) override |

| int | functionalWrite (const Addr ¶m_addr, Packet *param_pkt) override |

| bool | sendRequestMsg (CHIRequestMsgPtr msg) |

| bool | sendSnoopMsg (CHIRequestMsgPtr msg) |

| bool | sendResponseMsg (CHIResponseMsgPtr msg) |

| bool | sendDataMsg (CHIDataMsgPtr msg) |

| Public Member Functions inherited from gem5::ruby::AbstractController | |

| PARAMS (RubyController) | |

| AbstractController (const Params &p) | |

| NodeID | getVersion () const |

| MachineType | getType () const |

| void | initNetworkPtr (Network *net_ptr) |

| void | blockOnQueue (Addr, MessageBuffer *) |

| bool | isBlocked (Addr) const |

| void | unblock (Addr) |

| bool | isBlocked (Addr) |

| void | memRespQueueDequeued () |

| void | dequeueMemRespQueue () |

| virtual Cycles | mandatoryQueueLatency (const RubyRequestType ¶m_type) |

| virtual void | functionalRead (const Addr &addr, PacketPtr) |

| virtual int | functionalReadPriority () |

| Returns the priority used by functional reads when deciding from which controller to read a Maybe_Stale data block. | |

| virtual void | functionalRead (const Addr &addr, PacketPtr pkt, WriteMask &mask) |

| void | functionalMemoryRead (PacketPtr) |

| virtual int | functionalWrite (const Addr &addr, PacketPtr)=0 |

| int | functionalMemoryWrite (PacketPtr) |

| virtual void | enqueuePrefetch (const Addr &, const RubyRequestType &) |

| Function for enqueuing a prefetch request. | |

| virtual void | notifyCoalesced (const Addr &addr, const RubyRequestType &type, const RequestPtr &req, const DataBlock &data_blk, const bool &was_miss) |

| Notifies controller of a request coalesced at the sequencer. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| A function used to return the port associated with this bus object. | |

| bool | recvTimingResp (PacketPtr pkt) |

| Tick | recvAtomic (PacketPtr pkt) |

| const AddrRangeList & | getAddrRanges () const |

| MachineID | getMachineID () const |

| RequestorID | getRequestorId () const |

| statistics::Histogram & | getDelayHist () |

| statistics::Histogram & | getDelayVCHist (uint32_t index) |

| bool | respondsTo (Addr addr) |

| MachineID | mapAddressToMachine (Addr addr, MachineType mtype) const |

| Map an address to the correct MachineID. | |

| MachineID | mapAddressToDownstreamMachine (Addr addr, MachineType mtype=MachineType_NUM) const |

| Maps an address to the correct dowstream MachineID (i.e. | |

| const NetDest & | allDownstreamDest () const |

| List of downstream destinations (towards memory) | |

| const NetDest & | allUpstreamDest () const |

| List of upstream destinations (towards the CPU) | |

| Addr | getOffset (Addr addr) const |

| Addr | makeLineAddress (Addr addr) const |

| std::string | printAddress (Addr addr) const |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

| Public Member Functions inherited from gem5::ruby::Consumer | |

| Consumer (ClockedObject *em, Event::Priority ev_prio=Event::Default_Pri) | |

| virtual | ~Consumer () |

| virtual void | storeEventInfo (int info) |

| bool | alreadyScheduled (Tick time) |

| ClockedObject * | getObject () |

| void | scheduleEventAbsolute (Tick timeAbs) |

| void | scheduleEvent (Cycles timeDelta) |

Public Attributes | |

| std::function< void(ARM::CHI::Payload *payload, ARM::CHI::Phase *phase)> | bw |

| Set this to send data upstream. | |

| std::unordered_map< uint16_t, std::unique_ptr< Transaction > > | pendingTransactions |

| Public Attributes inherited from gem5::ruby::CHIGenericController | |

| const int | cacheLineSize |

| const int | cacheLineBits |

| const int | dataChannelSize |

| const int | dataMsgsPerLine |

| Public Attributes inherited from gem5::ruby::AbstractController | |

| gem5::ruby::AbstractController::ControllerStats | stats |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Additional Inherited Members | |

| Public Types inherited from gem5::ruby::CHIGenericController | |

| enum | CHIChannel { CHI_REQ = 0 , CHI_SNP = 1 , CHI_RSP = 2 , CHI_DAT = 3 } |

| using | CHIRequestMsg = CHI::CHIRequestMsg |

| using | CHIResponseMsg = CHI::CHIResponseMsg |

| using | CHIDataMsg = CHI::CHIDataMsg |

| using | CHIRequestMsgPtr = std::shared_ptr<CHIRequestMsg> |

| using | CHIResponseMsgPtr = std::shared_ptr<CHIResponseMsg> |

| using | CHIDataMsgPtr = std::shared_ptr<CHIDataMsg> |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Protected Types inherited from gem5::ruby::AbstractController | |

| typedef std::vector< MessageBuffer * > | MsgVecType |

| typedef std::set< MessageBuffer * > | MsgBufType |

| typedef std::map< Addr, MsgVecType * > | WaitingBufType |

| Protected Member Functions inherited from gem5::ruby::AbstractController | |

| void | profileRequest (const std::string &request) |

| Profiles original cache requests including PUTs. | |

| void | profileMsgDelay (uint32_t virtualNetwork, Cycles delay) |

| Profiles the delay associated with messages. | |

| template<typename EventType, typename StateType> | |

| void | incomingTransactionStart (Addr addr, EventType type, StateType initialState, bool retried, bool isAddressed=true) |

| Profiles an event that initiates a protocol transactions for a specific line (e.g. | |

| template<typename StateType> | |

| void | incomingTransactionEnd (Addr addr, StateType finalState, bool isAddressed=true) |

| Profiles an event that ends a transaction. | |

| template<typename EventType> | |

| void | outgoingTransactionStart (Addr addr, EventType type, bool isAddressed=true) |

| Profiles an event that initiates a transaction in a peer controller (e.g. | |

| void | outgoingTransactionEnd (Addr addr, bool retried, bool isAddressed=true) |

| Profiles the end of an outgoing transaction. | |

| void | stallBuffer (MessageBuffer *buf, Addr addr) |

| void | wakeUpBuffer (MessageBuffer *buf, Addr addr) |

| void | wakeUpBuffers (Addr addr) |

| void | wakeUpAllBuffers (Addr addr) |

| void | wakeUpAllBuffers () |

| bool | serviceMemoryQueue () |

| virtual bool | inCache (const Addr &addr, const bool &is_secure) |

| Functions needed by CacheAccessor. | |

| virtual bool | hasBeenPrefetched (const Addr &addr, const bool &is_secure) |

| virtual bool | hasBeenPrefetched (const Addr &addr, const bool &is_secure, const RequestorID &requestor) |

| virtual bool | inMissQueue (const Addr &addr, const bool &is_secure) |

| virtual bool | coalesce () |

| NetDest | broadcast (MachineType type) |

| int | machineCount (MachineType machType) |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

| Protected Attributes inherited from gem5::ruby::CHIGenericController | |

| MessageBuffer *const | reqOut |

| MessageBuffer *const | snpOut |

| MessageBuffer *const | rspOut |

| MessageBuffer *const | datOut |

| MessageBuffer *const | reqIn |

| MessageBuffer *const | snpIn |

| MessageBuffer *const | rspIn |

| MessageBuffer *const | datIn |

| std::vector< RubyPort * > | sequencers |

| Protected Attributes inherited from gem5::ruby::AbstractController | |

| std::unordered_map< Addr, TransMapPair > | m_inTransAddressed |

| std::unordered_map< Addr, TransMapPair > | m_outTransAddressed |

| std::unordered_map< Addr, TransMapPair > | m_inTransUnaddressed |

| std::unordered_map< Addr, TransMapPair > | m_outTransUnaddressed |

| const NodeID | m_version |

| MachineID | m_machineID |

| const NodeID | m_clusterID |

| const RequestorID | m_id |

| Network * | m_net_ptr |

| bool | m_is_blocking |

| std::map< Addr, MessageBuffer * > | m_block_map |

| WaitingBufType | m_waiting_buffers |

| unsigned int | m_in_ports |

| unsigned int | m_cur_in_port |

| const int | m_number_of_TBEs |

| const int | m_transitions_per_cycle |

| const unsigned int | m_buffer_size |

| Cycles | m_recycle_latency |

| const Cycles | m_mandatory_queue_latency |

| bool | m_waiting_mem_retry |

| bool | m_mem_ctrl_waiting_retry |

| MemoryPort | memoryPort |

| RubySystem * | m_ruby_system = nullptr |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Detailed Description

The tlm::chi::CacheController is a ruby CacheController which acts as a bridge between the AMBA TLM 2.0 implementation of CHI 1 with the gem5 (ruby) one.

In other words it translates AMBA CHI transactions into ruby messages (which are then forwarded to the MessageQueues) and viceversa.

ARM::CHI::Payload, CHIRequestMsg <--> CHIDataMsg ARM::CHI::Phase CHIResponseMsg CHIDataMsg

To connect the tlm::chi::CacheController in python is relatively straightforward. The upstream initiator/RNF needs to have a pointer to the controller, and this can be done for example with SimObject params. Example:

class MyRNF(): chi_controller = Param.TlmController("TLM-to-Ruby CacheController")

The RNF C++ code would then have to set the tlm::chi::CacheController::bw callback to implement the backward path to send data from downstream to upstream.

Definition at line 91 of file controller.hh.

Constructor & Destructor Documentation

◆ CacheController()

| gem5::tlm::chi::CacheController::CacheController | ( | const Params & | p | ) |

Definition at line 52 of file controller.cc.

References gem5::ruby::CHIGenericController::CHIGenericController(), and gem5::MipsISA::p.

Referenced by gem5::tlm::chi::CacheController::Transaction::gen(), and gem5::tlm::chi::CacheController::Transaction::Transaction().

Member Function Documentation

◆ PARAMS()

| gem5::tlm::chi::CacheController::PARAMS | ( | TlmController | ) |

References gem5::MipsISA::p.

◆ pCreditGrant()

| void gem5::tlm::chi::CacheController::pCreditGrant | ( | const CHIResponseMsg * | msg | ) |

◆ recvDataMsg()

|

overridevirtual |

Implements gem5::ruby::CHIGenericController.

Definition at line 120 of file controller.cc.

References pendingTransactions.

◆ recvRequestMsg()

|

overridevirtual |

Implements gem5::ruby::CHIGenericController.

Definition at line 58 of file controller.cc.

References panic.

◆ recvResponseMsg()

|

overridevirtual |

Implements gem5::ruby::CHIGenericController.

Definition at line 97 of file controller.cc.

References panic, pCreditGrant(), and pendingTransactions.

◆ recvSnoopMsg()

|

overridevirtual |

Implements gem5::ruby::CHIGenericController.

Definition at line 65 of file controller.cc.

References bw, and gem5::tlm::chi::ruby_to_tlm::snpOpcode().

◆ reqAddr()

| Addr gem5::tlm::chi::CacheController::reqAddr | ( | ARM::CHI::Payload & | payload, |

| ARM::CHI::Phase & | phase ) const |

Definition at line 272 of file controller.cc.

References gem5::ruby::CHIGenericController::cacheLineBits, gem5::ctz64(), and gem5::ruby::makeLineAddress().

Referenced by sendRequestMsg().

◆ reqSize()

| Addr gem5::tlm::chi::CacheController::reqSize | ( | ARM::CHI::Payload & | payload, |

| ARM::CHI::Phase & | phase ) const |

Definition at line 285 of file controller.cc.

References gem5::popCount(), and gem5::tlm::chi::transactionSize().

Referenced by sendRequestMsg().

◆ sendCompAck()

| void gem5::tlm::chi::CacheController::sendCompAck | ( | ARM::CHI::Payload & | payload, |

| ARM::CHI::Phase & | phase ) |

Definition at line 237 of file controller.cc.

References gem5::ruby::CHIGenericController::cacheLineBits, gem5::ruby::CHIGenericController::cacheLineSize, gem5::curTick(), gem5::ruby::AbstractController::getMachineID(), gem5::ruby::AbstractController::m_ruby_system, gem5::ruby::makeLineAddress(), gem5::ruby::AbstractController::mapAddressToDownstreamMachine(), and sendResponseMsg().

◆ sendDataMsg()

| void gem5::tlm::chi::CacheController::sendDataMsg | ( | ARM::CHI::Payload & | payload, |

| ARM::CHI::Phase & | phase ) |

Definition at line 327 of file controller.cc.

References gem5::bits(), gem5::ruby::CHIGenericController::cacheLineBits, gem5::ruby::CHIGenericController::cacheLineSize, gem5::curTick(), gem5::tlm::chi::tlm_to_ruby::datOpcode(), gem5::ruby::AbstractController::getMachineID(), gem5::ruby::AbstractController::m_ruby_system, gem5::ruby::makeLineAddress(), gem5::ruby::AbstractController::mapAddressToDownstreamMachine(), and sendDataMsg().

Referenced by sendDataMsg(), and sendMsg().

◆ sendMsg()

| void gem5::tlm::chi::CacheController::sendMsg | ( | ARM::CHI::Payload & | payload, |

| ARM::CHI::Phase & | phase ) |

Definition at line 254 of file controller.cc.

References panic, sendDataMsg(), sendRequestMsg(), and sendResponseMsg().

◆ sendRequestMsg()

| void gem5::tlm::chi::CacheController::sendRequestMsg | ( | ARM::CHI::Payload & | payload, |

| ARM::CHI::Phase & | phase ) |

Definition at line 298 of file controller.cc.

References gem5::ruby::CHIGenericController::cacheLineBits, gem5::ruby::CHIGenericController::cacheLineSize, gem5::curTick(), gem5::tlm::chi::CacheController::Transaction::gen(), gem5::ruby::AbstractController::getMachineID(), gem5::ruby::AbstractController::m_ruby_system, gem5::ruby::makeLineAddress(), gem5::ruby::AbstractController::mapAddressToDownstreamMachine(), pendingTransactions, reqAddr(), gem5::tlm::chi::tlm_to_ruby::reqOpcode(), reqSize(), and sendRequestMsg().

Referenced by sendMsg(), and sendRequestMsg().

◆ sendResponseMsg()

| void gem5::tlm::chi::CacheController::sendResponseMsg | ( | ARM::CHI::Payload & | payload, |

| ARM::CHI::Phase & | phase ) |

Definition at line 356 of file controller.cc.

References gem5::ruby::CHIGenericController::cacheLineBits, gem5::ruby::CHIGenericController::cacheLineSize, gem5::curTick(), gem5::ruby::AbstractController::getMachineID(), gem5::ruby::AbstractController::m_ruby_system, gem5::ruby::makeLineAddress(), gem5::ruby::AbstractController::mapAddressToDownstreamMachine(), gem5::tlm::chi::tlm_to_ruby::rspOpcode(), and sendResponseMsg().

Referenced by sendCompAck(), sendMsg(), and sendResponseMsg().

Member Data Documentation

◆ bw

| std::function<void(ARM::CHI::Payload* payload, ARM::CHI::Phase* phase)> gem5::tlm::chi::CacheController::bw |

Set this to send data upstream.

Definition at line 98 of file controller.hh.

Referenced by pCreditGrant(), and recvSnoopMsg().

◆ pendingTransactions

| std::unordered_map<uint16_t, std::unique_ptr<Transaction> > gem5::tlm::chi::CacheController::pendingTransactions |

Definition at line 170 of file controller.hh.

Referenced by recvDataMsg(), recvResponseMsg(), and sendRequestMsg().

The documentation for this class was generated from the following files:

- mem/ruby/protocol/chi/tlm/controller.hh

- mem/ruby/protocol/chi/tlm/controller.cc

Generated on Sat Oct 18 2025 08:07:04 for gem5 by doxygen 1.14.0