#include <AbstractController.hh>

Classes | |

| struct | ControllerStats |

| class | MemoryPort |

| Port that forwards requests and receives responses from the memory controller. More... | |

| struct | SenderState |

| struct | TransMapPair |

Public Member Functions | |

| PARAMS (RubyController) | |

| AbstractController (const Params &p) | |

| void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| NodeID | getVersion () const |

| MachineType | getType () const |

| void | initNetworkPtr (Network *net_ptr) |

| void | blockOnQueue (Addr, MessageBuffer *) |

| bool | isBlocked (Addr) const |

| void | unblock (Addr) |

| bool | isBlocked (Addr) |

| virtual MessageBuffer * | getMandatoryQueue () const =0 |

| virtual MessageBuffer * | getMemReqQueue () const =0 |

| virtual MessageBuffer * | getMemRespQueue () const =0 |

| void | memRespQueueDequeued () |

| void | dequeueMemRespQueue () |

| virtual AccessPermission | getAccessPermission (const Addr &addr)=0 |

| virtual void | print (std::ostream &out) const =0 |

| virtual void | wakeup ()=0 |

| virtual void | resetStats ()=0 |

| Callback to reset stats. | |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | recordCacheTrace (int cntrl, CacheRecorder *tr)=0 |

| virtual Sequencer * | getCPUSequencer () const =0 |

| virtual DMASequencer * | getDMASequencer () const =0 |

| virtual GPUCoalescer * | getGPUCoalescer () const =0 |

| virtual Cycles | mandatoryQueueLatency (const RubyRequestType ¶m_type) |

| virtual bool | functionalReadBuffers (PacketPtr &)=0 |

| These functions are used by ruby system to read/write the data blocks that exist with in the controller. | |

| virtual void | functionalRead (const Addr &addr, PacketPtr) |

| virtual int | functionalReadPriority () |

| Returns the priority used by functional reads when deciding from which controller to read a Maybe_Stale data block. | |

| virtual bool | functionalReadBuffers (PacketPtr &, WriteMask &mask)=0 |

| Functional read that reads only blocks not present in the mask. | |

| virtual void | functionalRead (const Addr &addr, PacketPtr pkt, WriteMask &mask) |

| void | functionalMemoryRead (PacketPtr) |

| virtual int | functionalWriteBuffers (PacketPtr &)=0 |

| The return value indicates the number of messages written with the data from the packet. | |

| virtual int | functionalWrite (const Addr &addr, PacketPtr)=0 |

| int | functionalMemoryWrite (PacketPtr) |

| virtual void | enqueuePrefetch (const Addr &, const RubyRequestType &) |

| Function for enqueuing a prefetch request. | |

| virtual void | notifyCoalesced (const Addr &addr, const RubyRequestType &type, const RequestPtr &req, const DataBlock &data_blk, const bool &was_miss) |

| Notifies controller of a request coalesced at the sequencer. | |

| virtual void | collateStats () |

| Function for collating statistics from all the controllers of this particular type. | |

| virtual void | initNetQueues ()=0 |

| Initialize the message buffers. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| A function used to return the port associated with this bus object. | |

| bool | recvTimingResp (PacketPtr pkt) |

| Tick | recvAtomic (PacketPtr pkt) |

| const AddrRangeList & | getAddrRanges () const |

| MachineID | getMachineID () const |

| RequestorID | getRequestorId () const |

| statistics::Histogram & | getDelayHist () |

| statistics::Histogram & | getDelayVCHist (uint32_t index) |

| bool | respondsTo (Addr addr) |

| MachineID | mapAddressToMachine (Addr addr, MachineType mtype) const |

| Map an address to the correct MachineID. | |

| MachineID | mapAddressToDownstreamMachine (Addr addr, MachineType mtype=MachineType_NUM) const |

| Maps an address to the correct dowstream MachineID (i.e. | |

| const NetDest & | allDownstreamDest () const |

| List of downstream destinations (towards memory) | |

| const NetDest & | allUpstreamDest () const |

| List of upstream destinations (towards the CPU) | |

| Addr | getOffset (Addr addr) const |

| Addr | makeLineAddress (Addr addr) const |

| std::string | printAddress (Addr addr) const |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

| Public Member Functions inherited from gem5::ruby::Consumer | |

| Consumer (ClockedObject *em, Event::Priority ev_prio=Event::Default_Pri) | |

| virtual | ~Consumer () |

| virtual void | storeEventInfo (int info) |

| bool | alreadyScheduled (Tick time) |

| ClockedObject * | getObject () |

| void | scheduleEventAbsolute (Tick timeAbs) |

| void | scheduleEvent (Cycles timeDelta) |

Public Attributes | |

| gem5::ruby::AbstractController::ControllerStats | stats |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Protected Types | |

| typedef std::vector< MessageBuffer * > | MsgVecType |

| typedef std::set< MessageBuffer * > | MsgBufType |

| typedef std::map< Addr, MsgVecType * > | WaitingBufType |

Protected Member Functions | |

| void | profileRequest (const std::string &request) |

| Profiles original cache requests including PUTs. | |

| void | profileMsgDelay (uint32_t virtualNetwork, Cycles delay) |

| Profiles the delay associated with messages. | |

| template<typename EventType, typename StateType> | |

| void | incomingTransactionStart (Addr addr, EventType type, StateType initialState, bool retried, bool isAddressed=true) |

| Profiles an event that initiates a protocol transactions for a specific line (e.g. | |

| template<typename StateType> | |

| void | incomingTransactionEnd (Addr addr, StateType finalState, bool isAddressed=true) |

| Profiles an event that ends a transaction. | |

| template<typename EventType> | |

| void | outgoingTransactionStart (Addr addr, EventType type, bool isAddressed=true) |

| Profiles an event that initiates a transaction in a peer controller (e.g. | |

| void | outgoingTransactionEnd (Addr addr, bool retried, bool isAddressed=true) |

| Profiles the end of an outgoing transaction. | |

| void | stallBuffer (MessageBuffer *buf, Addr addr) |

| void | wakeUpBuffer (MessageBuffer *buf, Addr addr) |

| void | wakeUpBuffers (Addr addr) |

| void | wakeUpAllBuffers (Addr addr) |

| void | wakeUpAllBuffers () |

| bool | serviceMemoryQueue () |

| virtual bool | inCache (const Addr &addr, const bool &is_secure) |

| Functions needed by CacheAccessor. | |

| virtual bool | hasBeenPrefetched (const Addr &addr, const bool &is_secure) |

| virtual bool | hasBeenPrefetched (const Addr &addr, const bool &is_secure, const RequestorID &requestor) |

| virtual bool | inMissQueue (const Addr &addr, const bool &is_secure) |

| virtual bool | coalesce () |

| NetDest | broadcast (MachineType type) |

| int | machineCount (MachineType machType) |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Private Member Functions | |

| void | sendRetryRespToMem () |

Private Attributes | |

| const AddrRangeList | addrRanges |

| The address range to which the controller responds on the CPU side. | |

| std::unordered_map< MachineType, AddrRangeMap< MachineID, 3 > > | downstreamAddrMap |

| NetDest | downstreamDestinations |

| NetDest | upstreamDestinations |

| MemberEventWrapper<&AbstractController::sendRetryRespToMem > | mRetryRespEvent |

Friends | |

| class | RubyPrefetcherProxy |

Additional Inherited Members | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

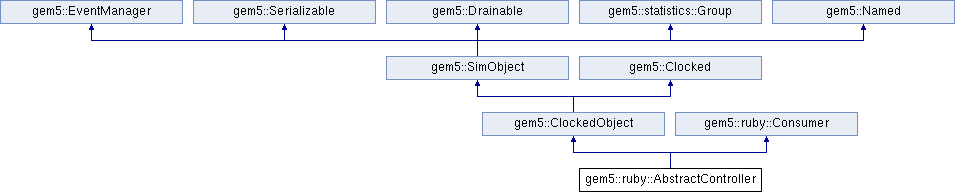

Detailed Description

Definition at line 84 of file AbstractController.hh.

Member Typedef Documentation

◆ MsgBufType

|

protected |

Definition at line 419 of file AbstractController.hh.

◆ MsgVecType

|

protected |

Definition at line 418 of file AbstractController.hh.

◆ WaitingBufType

|

protected |

Definition at line 420 of file AbstractController.hh.

Constructor & Destructor Documentation

◆ AbstractController()

| gem5::ruby::AbstractController::AbstractController | ( | const Params & | p | ) |

Definition at line 56 of file AbstractController.cc.

References addrRanges, gem5::ClockedObject::ClockedObject(), collateStats(), gem5::ruby::Consumer::Consumer(), gem5::csprintf(), getRequestorId(), m_buffer_size, m_clusterID, m_id, m_is_blocking, m_mandatory_queue_latency, m_mem_ctrl_waiting_retry, m_number_of_TBEs, m_recycle_latency, m_transitions_per_cycle, m_version, m_waiting_mem_retry, memoryPort, mRetryRespEvent, gem5::Named::name(), gem5::MipsISA::p, gem5::statistics::registerDumpCallback(), stats, and gem5::X86ISA::system.

Referenced by gem5::ruby::CHIGenericController::CHIGenericController(), and gem5::ruby::AbstractController::MemoryPort::MemoryPort().

Member Function Documentation

◆ allDownstreamDest()

|

inline |

List of downstream destinations (towards memory)

Definition at line 236 of file AbstractController.hh.

References downstreamDestinations.

◆ allUpstreamDest()

|

inline |

List of upstream destinations (towards the CPU)

Definition at line 239 of file AbstractController.hh.

References upstreamDestinations.

◆ blockOnQueue()

| void gem5::ruby::AbstractController::blockOnQueue | ( | Addr | addr, |

| MessageBuffer * | port ) |

Definition at line 324 of file AbstractController.cc.

References gem5::X86ISA::addr, m_block_map, and m_is_blocking.

◆ broadcast()

|

protected |

Definition at line 500 of file AbstractController.cc.

References gem5::ruby::NetDest::add(), gem5::ArmISA::i, and m_ruby_system.

◆ coalesce()

|

inlineprotectedvirtual |

Definition at line 401 of file AbstractController.hh.

References fatal.

◆ collateStats()

|

inlinevirtual |

Function for collating statistics from all the controllers of this particular type.

This function should only be called from the version 0 of this controller type.

Reimplemented in gem5::ruby::CHIGenericController.

Definition at line 176 of file AbstractController.hh.

References fatal.

Referenced by AbstractController().

◆ dequeueMemRespQueue()

| void gem5::ruby::AbstractController::dequeueMemRespQueue | ( | ) |

Definition at line 466 of file AbstractController.cc.

References gem5::Clocked::clockEdge(), gem5_assert, getMemRespQueue(), memRespQueueDequeued(), and gem5::ArmISA::q.

◆ enqueuePrefetch()

|

inlinevirtual |

Function for enqueuing a prefetch request.

Definition at line 161 of file AbstractController.hh.

References fatal.

◆ functionalMemoryRead()

| void gem5::ruby::AbstractController::functionalMemoryRead | ( | PacketPtr | pkt | ) |

Definition at line 358 of file AbstractController.cc.

References gem5::ruby::MessageBuffer::functionalRead(), getMemReqQueue(), and memoryPort.

◆ functionalMemoryWrite()

| int gem5::ruby::AbstractController::functionalMemoryWrite | ( | PacketPtr | pkt | ) |

Definition at line 367 of file AbstractController.cc.

References memoryPort.

◆ functionalRead() [1/2]

|

inlinevirtual |

Definition at line 149 of file AbstractController.hh.

References gem5::X86ISA::addr, gem5::ArmISA::mask, and panic.

◆ functionalRead() [2/2]

|

inlinevirtual |

Definition at line 135 of file AbstractController.hh.

References gem5::X86ISA::addr, and panic.

Referenced by gem5::ruby::RubySystem::partialFunctionalRead(), and gem5::ruby::RubySystem::simpleFunctionalRead().

◆ functionalReadBuffers() [1/2]

|

pure virtual |

These functions are used by ruby system to read/write the data blocks that exist with in the controller.

Implemented in gem5::ruby::CHIGenericController.

Referenced by gem5::ruby::RubySystem::partialFunctionalRead().

◆ functionalReadBuffers() [2/2]

|

pure virtual |

Functional read that reads only blocks not present in the mask.

Return number of bytes read.

Implemented in gem5::ruby::CHIGenericController.

References gem5::ArmISA::mask.

◆ functionalReadPriority()

|

inlinevirtual |

Returns the priority used by functional reads when deciding from which controller to read a Maybe_Stale data block.

Lower positive values have higher priority, negative values are ignored.

- Returns

- the controller's priority

Definition at line 144 of file AbstractController.hh.

Referenced by gem5::ruby::RubySystem::simpleFunctionalRead().

◆ functionalWrite()

|

pure virtual |

References gem5::X86ISA::addr.

◆ functionalWriteBuffers()

|

pure virtual |

The return value indicates the number of messages written with the data from the packet.

Implemented in gem5::ruby::CHIGenericController.

◆ getAccessPermission()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

References gem5::X86ISA::addr.

◆ getAddrRanges()

|

inline |

Definition at line 189 of file AbstractController.hh.

References addrRanges.

Referenced by gem5::ruby::Network::Network().

◆ getCPUSequencer()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

Referenced by gem5::ruby::Profiler::collateStats().

◆ getDelayHist()

|

inline |

Definition at line 195 of file AbstractController.hh.

References stats.

Referenced by gem5::ruby::Profiler::collateStats().

◆ getDelayVCHist()

|

inline |

Definition at line 196 of file AbstractController.hh.

References gem5::MipsISA::index, and stats.

Referenced by gem5::ruby::Profiler::collateStats().

◆ getDMASequencer()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

◆ getGPUCoalescer()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

Referenced by gem5::ruby::Profiler::collateStats().

◆ getMachineID()

|

inline |

Definition at line 192 of file AbstractController.hh.

References m_machineID.

Referenced by gem5::ruby::Network::Network(), gem5::ruby::RubySystem::registerAbstractController(), gem5::tlm::chi::CacheController::sendCompAck(), gem5::tlm::chi::CacheController::sendDataMsg(), gem5::tlm::chi::CacheController::sendRequestMsg(), and gem5::tlm::chi::CacheController::sendResponseMsg().

◆ getMandatoryQueue()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

◆ getMemReqQueue()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

Referenced by functionalMemoryRead(), init(), and serviceMemoryQueue().

◆ getMemRespQueue()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

Referenced by dequeueMemRespQueue(), and recvTimingResp().

◆ getOffset()

Definition at line 482 of file AbstractController.cc.

References gem5::X86ISA::addr, gem5::ruby::getOffset(), and m_ruby_system.

Referenced by serviceMemoryQueue().

◆ getPort()

|

virtual |

A function used to return the port associated with this bus object.

Reimplemented from gem5::SimObject.

Definition at line 352 of file AbstractController.cc.

References memoryPort.

◆ getRequestorId()

|

inline |

Definition at line 193 of file AbstractController.hh.

References m_id.

Referenced by AbstractController().

◆ getType()

|

inline |

Definition at line 92 of file AbstractController.hh.

References m_machineID.

Referenced by gem5::ruby::Network::Network(), and gem5::ruby::Topology::Topology().

◆ getVersion()

|

inline |

Definition at line 91 of file AbstractController.hh.

References m_machineID.

Referenced by gem5::ruby::Network::Network(), and gem5::ruby::Topology::Topology().

◆ hasBeenPrefetched() [1/2]

|

inlineprotectedvirtual |

Definition at line 391 of file AbstractController.hh.

References gem5::X86ISA::addr, and fatal.

◆ hasBeenPrefetched() [2/2]

|

inlineprotectedvirtual |

Definition at line 394 of file AbstractController.hh.

References gem5::X86ISA::addr, and fatal.

◆ inCache()

|

inlineprotectedvirtual |

Functions needed by CacheAccessor.

These are implemented in SLICC, thus the const& for all args to match the generated code.

Definition at line 388 of file AbstractController.hh.

References gem5::X86ISA::addr, and fatal.

◆ incomingTransactionEnd()

|

inlineprotected |

Profiles an event that ends a transaction.

This function also supports "unaddressed" transactions, those not associated with an address in memory but instead associated with a unique ID.

- Parameters

-

addr address or unique ID with an outstanding transaction finalState state of the line after the transaction isAddressed is addr a line address or a unique ID

Definition at line 298 of file AbstractController.hh.

References gem5::X86ISA::addr, gem5::curTick(), gem5_assert, m_inTransAddressed, m_inTransUnaddressed, gem5::Named::name(), stats, and gem5::Clocked::ticksToCycles().

◆ incomingTransactionStart()

|

inlineprotected |

Profiles an event that initiates a protocol transactions for a specific line (e.g.

events triggered by incoming request messages). A histogram with the latency of the transactions is generated for all combinations of trigger event, initial state, and final state. This function also supports "unaddressed" transactions, those not associated with an address in memory but instead associated with a unique ID.

- Parameters

-

addr address of the line, or unique transaction ID type event that started the transaction initialState state of the line before the transaction isAddressed is addr a line address or a unique ID

Definition at line 275 of file AbstractController.hh.

References gem5::X86ISA::addr, gem5::curTick(), m_inTransAddressed, m_inTransUnaddressed, and stats.

◆ init()

|

virtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Reimplemented in gem5::ruby::CHIGenericController.

Definition at line 79 of file AbstractController.cc.

References downstreamAddrMap, downstreamDestinations, fatal, getMemReqQueue(), gem5::ruby::Network::getNumberOfVirtualNetworks(), gem5::ruby::MachineID::getType(), gem5::ArmISA::i, m_ruby_system, gem5::Named::name(), gem5::SimObject::params(), gem5::ruby::MessageBuffer::setConsumer(), stats, and upstreamDestinations.

Referenced by gem5::ruby::CHIGenericController::init().

◆ initNetQueues()

|

pure virtual |

Initialize the message buffers.

Implemented in gem5::ruby::CHIGenericController.

References gem5::InvalidPortID.

◆ initNetworkPtr()

|

inline |

Definition at line 94 of file AbstractController.hh.

References m_net_ptr.

Referenced by gem5::ruby::Network::Network().

◆ inMissQueue()

|

inlineprotectedvirtual |

Definition at line 398 of file AbstractController.hh.

References gem5::X86ISA::addr, and fatal.

◆ isBlocked() [1/2]

| bool gem5::ruby::AbstractController::isBlocked | ( | Addr | addr | ) |

Definition at line 346 of file AbstractController.cc.

References gem5::X86ISA::addr, and m_block_map.

◆ isBlocked() [2/2]

| bool gem5::ruby::AbstractController::isBlocked | ( | Addr | addr | ) | const |

Definition at line 331 of file AbstractController.cc.

References gem5::X86ISA::addr, m_block_map, and m_is_blocking.

◆ machineCount()

|

protected |

Definition at line 514 of file AbstractController.cc.

References m_ruby_system.

◆ makeLineAddress()

Definition at line 488 of file AbstractController.cc.

References gem5::X86ISA::addr, m_ruby_system, and gem5::ruby::makeLineAddress().

◆ mandatoryQueueLatency()

|

inlinevirtual |

Definition at line 129 of file AbstractController.hh.

References m_mandatory_queue_latency.

◆ mapAddressToDownstreamMachine()

| MachineID gem5::ruby::AbstractController::mapAddressToDownstreamMachine | ( | Addr | addr, |

| MachineType | mtype = MachineType_NUM ) const |

Maps an address to the correct dowstream MachineID (i.e.

the component in the next level of the cache hierarchy towards memory)

This function uses the local list of possible destinations instead of querying the network.

- Parameters

-

the destination address the type of the destination (optional)

- Returns

- the MachineID of the destination

Definition at line 434 of file AbstractController.cc.

References gem5::X86ISA::addr, downstreamAddrMap, fatal, gem5::ArmISA::i, and gem5::Named::name().

Referenced by gem5::tlm::chi::CacheController::sendCompAck(), gem5::tlm::chi::CacheController::sendDataMsg(), gem5::tlm::chi::CacheController::sendRequestMsg(), and gem5::tlm::chi::CacheController::sendResponseMsg().

◆ mapAddressToMachine()

| MachineID gem5::ruby::AbstractController::mapAddressToMachine | ( | Addr | addr, |

| MachineType | mtype ) const |

Map an address to the correct MachineID.

This function querries the network for the NodeID of the destination for a given request using its address and the type of the destination. For example for a request with a given address to a directory it will return the MachineID of the authorative directory.

- Parameters

-

the destination address the type of the destination

- Returns

- the MachineID of the destination

Definition at line 426 of file AbstractController.cc.

References gem5::X86ISA::addr, and m_net_ptr.

◆ memRespQueueDequeued()

| void gem5::ruby::AbstractController::memRespQueueDequeued | ( | ) |

Definition at line 459 of file AbstractController.cc.

References gem5::Clocked::clockEdge(), m_mem_ctrl_waiting_retry, mRetryRespEvent, and gem5::EventManager::schedule().

Referenced by dequeueMemRespQueue().

◆ notifyCoalesced()

|

inlinevirtual |

Notifies controller of a request coalesced at the sequencer.

By default, it does nothing. Behavior is protocol-specific

Definition at line 166 of file AbstractController.hh.

References gem5::X86ISA::addr.

◆ outgoingTransactionEnd()

|

inlineprotected |

Profiles the end of an outgoing transaction.

(e.g. receiving the response for a requests) This function also supports "unaddressed" transactions, those not associated with an address in memory but instead associated with a unique ID.

- Parameters

-

addr address of the line with an outstanding transaction isAddressed is addr a line address or a unique ID

Definition at line 356 of file AbstractController.hh.

References gem5::X86ISA::addr, gem5::curTick(), gem5_assert, m_outTransAddressed, m_outTransUnaddressed, gem5::Named::name(), stats, and gem5::Clocked::ticksToCycles().

◆ outgoingTransactionStart()

|

inlineprotected |

Profiles an event that initiates a transaction in a peer controller (e.g.

an event that sends a request message) This function also supports "unaddressed" transactions, those not associated with an address in memory but instead associated with a unique ID.

- Parameters

-

addr address of the line or a unique transaction ID type event that started the transaction isAddressed is addr a line address or a unique ID

Definition at line 337 of file AbstractController.hh.

References gem5::X86ISA::addr, gem5::curTick(), m_outTransAddressed, and m_outTransUnaddressed.

◆ PARAMS()

| gem5::ruby::AbstractController::PARAMS | ( | RubyController | ) |

References gem5::MipsISA::p.

◆ print()

|

pure virtual |

Implements gem5::ruby::Consumer.

Implemented in gem5::ruby::CHIGenericController.

◆ printAddress()

| std::string gem5::ruby::AbstractController::printAddress | ( | Addr | addr | ) | const |

Definition at line 494 of file AbstractController.cc.

References gem5::X86ISA::addr, m_ruby_system, and gem5::ruby::printAddress().

◆ profileMsgDelay()

|

protected |

Profiles the delay associated with messages.

Definition at line 141 of file AbstractController.cc.

References stats.

◆ profileRequest()

|

protected |

Profiles original cache requests including PUTs.

◆ recordCacheTrace()

|

pure virtual |

Implemented in gem5::ruby::CHIGenericController.

◆ recvAtomic()

Definition at line 420 of file AbstractController.cc.

References memoryPort, and gem5::Clocked::ticksToCycles().

Referenced by gem5::ruby::RubyPort::MemResponsePort::recvAtomic().

◆ recvTimingResp()

| bool gem5::ruby::AbstractController::recvTimingResp | ( | PacketPtr | pkt | ) |

Definition at line 377 of file AbstractController.cc.

References gem5::Clocked::clockEdge(), gem5::curTick(), gem5::Clocked::cyclesToTicks(), gem5_assert, gem5::Packet::getAddr(), getMemRespQueue(), gem5::Packet::getPtr(), gem5::Packet::isRead(), gem5::Packet::isResponse(), gem5::Packet::isWrite(), m_machineID, m_mem_ctrl_waiting_retry, m_ruby_system, panic, gem5::ArmISA::s, and gem5::Packet::senderState.

Referenced by serviceMemoryQueue().

◆ regStats()

|

virtual |

Callback to set stat parameters.

This callback is typically used for complex stats (e.g., distributions) that need parameters in addition to a name and a description. Stat names and descriptions should typically be set from the constructor usingo from the constructor using the ADD_STAT macro.

Reimplemented from gem5::statistics::Group.

Reimplemented in gem5::ruby::CHIGenericController.

Definition at line 135 of file AbstractController.cc.

References gem5::statistics::Group::regStats().

Referenced by gem5::ruby::CHIGenericController::regStats().

◆ resetStats()

|

pure virtual |

Callback to reset stats.

Reimplemented from gem5::statistics::Group.

Implemented in gem5::ruby::CHIGenericController.

Definition at line 124 of file AbstractController.cc.

References gem5::ruby::Network::getNumberOfVirtualNetworks(), gem5::ArmISA::i, gem5::statistics::Group::resetStats(), and stats.

Referenced by gem5::ruby::CHIGenericController::resetStats().

◆ respondsTo()

|

inline |

Definition at line 199 of file AbstractController.hh.

References gem5::X86ISA::addr, and addrRanges.

◆ sendRetryRespToMem()

|

private |

Definition at line 474 of file AbstractController.cc.

References m_mem_ctrl_waiting_retry, and memoryPort.

◆ serviceMemoryQueue()

|

protected |

Definition at line 265 of file AbstractController.cc.

References gem5::Packet::allocate(), gem5::Clocked::clockEdge(), gem5::Packet::createRead(), gem5::Packet::createWrite(), gem5::Packet::dataDynamic(), getMemReqQueue(), getOffset(), m_id, m_ruby_system, m_waiting_mem_retry, memoryPort, panic, gem5::Packet::pushSenderState(), recvTimingResp(), gem5::ArmISA::s, gem5::ruby::Consumer::scheduleEvent(), and gem5::Packet::setData().

◆ stallBuffer()

|

protected |

Definition at line 149 of file AbstractController.cc.

References gem5::X86ISA::addr, DPRINTF, m_cur_in_port, m_in_ports, and m_waiting_buffers.

◆ unblock()

| void gem5::ruby::AbstractController::unblock | ( | Addr | addr | ) |

Definition at line 337 of file AbstractController.cc.

References gem5::X86ISA::addr, m_block_map, and m_is_blocking.

◆ wakeup()

|

pure virtual |

Implements gem5::ruby::Consumer.

Implemented in gem5::ruby::CHIGenericController.

◆ wakeUpAllBuffers() [1/2]

|

protected |

Definition at line 226 of file AbstractController.cc.

References gem5::Clocked::clockEdge(), and m_waiting_buffers.

◆ wakeUpAllBuffers() [2/2]

|

protected |

Definition at line 206 of file AbstractController.cc.

References gem5::X86ISA::addr, gem5::Clocked::clockEdge(), m_in_ports, and m_waiting_buffers.

◆ wakeUpBuffer()

|

protected |

Definition at line 163 of file AbstractController.cc.

References gem5::X86ISA::addr, gem5::Clocked::clockEdge(), m_waiting_buffers, and gem5::ruby::MessageBuffer::reanalyzeMessages().

◆ wakeUpBuffers()

|

protected |

Definition at line 185 of file AbstractController.cc.

References gem5::X86ISA::addr, gem5::Clocked::clockEdge(), m_cur_in_port, and m_waiting_buffers.

Friends And Related Symbol Documentation

◆ RubyPrefetcherProxy

|

friend |

Definition at line 404 of file AbstractController.hh.

References RubyPrefetcherProxy.

Referenced by RubyPrefetcherProxy.

Member Data Documentation

◆ addrRanges

|

private |

The address range to which the controller responds on the CPU side.

Definition at line 478 of file AbstractController.hh.

Referenced by AbstractController(), getAddrRanges(), and respondsTo().

◆ downstreamAddrMap

|

private |

Definition at line 481 of file AbstractController.hh.

Referenced by init(), and mapAddressToDownstreamMachine().

◆ downstreamDestinations

|

private |

Definition at line 483 of file AbstractController.hh.

Referenced by allDownstreamDest(), and init().

◆ m_block_map

|

protected |

Definition at line 416 of file AbstractController.hh.

Referenced by blockOnQueue(), isBlocked(), isBlocked(), and unblock().

◆ m_buffer_size

|

protected |

Definition at line 427 of file AbstractController.hh.

Referenced by AbstractController().

◆ m_clusterID

|

protected |

Definition at line 409 of file AbstractController.hh.

Referenced by AbstractController().

◆ m_cur_in_port

|

protected |

Definition at line 424 of file AbstractController.hh.

Referenced by stallBuffer(), and wakeUpBuffers().

◆ m_id

|

protected |

Definition at line 412 of file AbstractController.hh.

Referenced by AbstractController(), getRequestorId(), and serviceMemoryQueue().

◆ m_in_ports

|

protected |

Definition at line 423 of file AbstractController.hh.

Referenced by stallBuffer(), and wakeUpAllBuffers().

◆ m_inTransAddressed

|

protected |

Definition at line 254 of file AbstractController.hh.

Referenced by incomingTransactionEnd(), and incomingTransactionStart().

◆ m_inTransUnaddressed

|

protected |

Definition at line 257 of file AbstractController.hh.

Referenced by incomingTransactionEnd(), and incomingTransactionStart().

◆ m_is_blocking

|

protected |

Definition at line 415 of file AbstractController.hh.

Referenced by AbstractController(), blockOnQueue(), isBlocked(), and unblock().

◆ m_machineID

|

protected |

Definition at line 408 of file AbstractController.hh.

Referenced by gem5::ruby::CHIGenericController::CHIGenericController(), getMachineID(), getType(), getVersion(), gem5::ruby::CHIGenericController::initNetQueues(), and recvTimingResp().

◆ m_mandatory_queue_latency

|

protected |

Definition at line 429 of file AbstractController.hh.

Referenced by AbstractController(), and mandatoryQueueLatency().

◆ m_mem_ctrl_waiting_retry

|

protected |

Definition at line 431 of file AbstractController.hh.

Referenced by AbstractController(), memRespQueueDequeued(), recvTimingResp(), and sendRetryRespToMem().

◆ m_net_ptr

|

protected |

Definition at line 414 of file AbstractController.hh.

Referenced by gem5::ruby::CHIGenericController::initNetQueues(), initNetworkPtr(), and mapAddressToMachine().

◆ m_number_of_TBEs

|

protected |

Definition at line 425 of file AbstractController.hh.

Referenced by AbstractController().

◆ m_outTransAddressed

|

protected |

Definition at line 255 of file AbstractController.hh.

Referenced by outgoingTransactionEnd(), and outgoingTransactionStart().

◆ m_outTransUnaddressed

|

protected |

Definition at line 258 of file AbstractController.hh.

Referenced by outgoingTransactionEnd(), and outgoingTransactionStart().

◆ m_recycle_latency

|

protected |

Definition at line 428 of file AbstractController.hh.

Referenced by AbstractController().

◆ m_ruby_system

|

protected |

Definition at line 469 of file AbstractController.hh.

Referenced by broadcast(), gem5::ruby::CHIGenericController::CHIGenericController(), getOffset(), init(), gem5::ruby::CHIGenericController::initNetQueues(), machineCount(), makeLineAddress(), printAddress(), recvTimingResp(), gem5::tlm::chi::CacheController::sendCompAck(), gem5::tlm::chi::CacheController::sendDataMsg(), gem5::ruby::CHIGenericController::sendMessage(), gem5::tlm::chi::CacheController::sendRequestMsg(), gem5::tlm::chi::CacheController::sendResponseMsg(), and serviceMemoryQueue().

◆ m_transitions_per_cycle

|

protected |

Definition at line 426 of file AbstractController.hh.

Referenced by AbstractController().

◆ m_version

|

protected |

Definition at line 407 of file AbstractController.hh.

Referenced by AbstractController(), gem5::ruby::CHIGenericController::CHIGenericController(), gem5::ruby::CHIGenericController::initNetQueues(), and gem5::ruby::CHIGenericController::print().

◆ m_waiting_buffers

|

protected |

Definition at line 421 of file AbstractController.hh.

Referenced by stallBuffer(), wakeUpAllBuffers(), wakeUpAllBuffers(), wakeUpBuffer(), and wakeUpBuffers().

◆ m_waiting_mem_retry

|

protected |

Definition at line 430 of file AbstractController.hh.

Referenced by AbstractController(), and serviceMemoryQueue().

◆ memoryPort

|

protected |

Definition at line 457 of file AbstractController.hh.

Referenced by AbstractController(), functionalMemoryRead(), functionalMemoryWrite(), getPort(), recvAtomic(), sendRetryRespToMem(), and serviceMemoryQueue().

◆ mRetryRespEvent

|

private |

Definition at line 487 of file AbstractController.hh.

Referenced by AbstractController(), and memRespQueueDequeued().

◆ stats

| gem5::ruby::AbstractController::ControllerStats gem5::ruby::AbstractController::stats |

◆ upstreamDestinations

|

private |

Definition at line 484 of file AbstractController.hh.

Referenced by allUpstreamDest(), and init().

The documentation for this class was generated from the following files:

- mem/ruby/slicc_interface/AbstractController.hh

- mem/ruby/slicc_interface/AbstractController.cc

Generated on Sat Oct 18 2025 08:07:02 for gem5 by doxygen 1.14.0