Event triggered to check the value of the destination registers. More...

#include <tarmac_parser.hh>

Public Member Functions | |

| TarmacParserRecordEvent (TarmacParser &_parent, ThreadContext *_thread, const StaticInstPtr _inst, const PCStateBase &_pc, bool _mismatch, bool _mismatch_on_pc_or_opcode) | |

| void | process () |

| const char * | description () const |

| Return a C string describing the event. | |

| Public Member Functions inherited from gem5::Event | |

| Event (Priority p=Default_Pri, Flags f=0) | |

| bool | scheduled () const |

| Determine if the current event is scheduled. | |

| void | squash () |

| Squash the current event. | |

| bool | squashed () const |

| Check whether the event is squashed. | |

| bool | isExitEvent () const |

| See if this is a SimExitEvent (without resorting to RTTI) | |

| bool | isManaged () const |

| Check whether this event will auto-delete. | |

| bool | isAutoDelete () const |

| The function returns true if the object is automatically deleted after the event is processed. | |

| Tick | when () const |

| Get the time that the event is scheduled. | |

| Priority | priority () const |

| Get the event priority. | |

| virtual BaseGlobalEvent * | globalEvent () |

| If this is part of a GlobalEvent, return the pointer to the Global Event. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| virtual | ~Event () |

| virtual const std::string | name () const |

| void | dump () const |

| Dump the current event data. | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

Public Attributes | |

| TarmacParser & | parent |

| Reference to the TARMAC trace object to which this record belongs. | |

| ThreadContext * | thread |

| Current thread context. | |

| const StaticInstPtr | inst |

| Current instruction. | |

| std::unique_ptr< PCStateBase > | pc |

| PC of the current instruction. | |

| bool | mismatch |

| True if a mismatch has been detected for this instruction. | |

| bool | mismatchOnPcOrOpcode |

| True if a mismatch has been detected for this instruction on PC or opcode. | |

Additional Inherited Members | |

| Public Types inherited from gem5::EventBase | |

| typedef int8_t | Priority |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Static Public Attributes inherited from gem5::EventBase | |

| static const Priority | Minimum_Pri = SCHAR_MIN |

| Event priorities, to provide tie-breakers for events scheduled at the same cycle. | |

| static const Priority | Debug_Enable_Pri = -101 |

| If we enable tracing on a particular cycle, do that as the very first thing so we don't miss any of the events on that cycle (even if we enter the debugger). | |

| static const Priority | Debug_Break_Pri = -100 |

| Breakpoints should happen before anything else (except enabling trace output), so we don't miss any action when debugging. | |

| static const Priority | CPU_Switch_Pri = -31 |

| CPU switches schedule the new CPU's tick event for the same cycle (after unscheduling the old CPU's tick event). | |

| static const Priority | Delayed_Writeback_Pri = -1 |

| For some reason "delayed" inter-cluster writebacks are scheduled before regular writebacks (which have default priority). | |

| static const Priority | Default_Pri = 0 |

| Default is zero for historical reasons. | |

| static const Priority | DVFS_Update_Pri = 31 |

| DVFS update event leads to stats dump therefore given a lower priority to ensure all relevant states have been updated. | |

| static const Priority | Serialize_Pri = 32 |

| Serailization needs to occur before tick events also, so that a serialize/unserialize is identical to an on-line CPU switch. | |

| static const Priority | CPU_Tick_Pri = 50 |

| CPU ticks must come after other associated CPU events (such as writebacks). | |

| static const Priority | CPU_Exit_Pri = 64 |

| If we want to exit a thread in a CPU, it comes after CPU_Tick_Pri. | |

| static const Priority | Stat_Event_Pri = 90 |

| Statistics events (dump, reset, etc.) come after everything else, but before exit. | |

| static const Priority | Progress_Event_Pri = 95 |

| Progress events come at the end. | |

| static const Priority | Sim_Exit_Pri = 100 |

| If we want to exit on this cycle, it's the very last thing we do. | |

| static const Priority | Maximum_Pri = SCHAR_MAX |

| Maximum priority. | |

| Protected Types inherited from gem5::EventBase | |

| typedef unsigned short | FlagsType |

| typedef ::gem5::Flags< FlagsType > | Flags |

| Protected Member Functions inherited from gem5::Event | |

| Flags | getFlags () const |

| bool | isFlagSet (Flags _flags) const |

| void | setFlags (Flags _flags) |

| void | clearFlags (Flags _flags) |

| void | clearFlags () |

| virtual void | trace (const char *action) |

| This function isn't really useful if TRACING_ON is not defined. | |

| const std::string | instanceString () const |

| Return the instance number as a string. | |

| void | acquire () |

| Memory management hooks for events that have the Managed flag set. | |

| void | release () |

| Managed event removed from the event queue. | |

| virtual void | acquireImpl () |

| virtual void | releaseImpl () |

| Static Protected Attributes inherited from gem5::EventBase | |

| static const FlagsType | PublicRead = 0x003f |

| static const FlagsType | PublicWrite = 0x001d |

| static const FlagsType | Squashed = 0x0001 |

| static const FlagsType | Scheduled = 0x0002 |

| static const FlagsType | Managed = 0x0004 |

| static const FlagsType | AutoDelete = Managed |

| static const FlagsType | Reserved0 = 0x0008 |

| This used to be AutoSerialize. | |

| static const FlagsType | IsExitEvent = 0x0010 |

| static const FlagsType | IsMainQueue = 0x0020 |

| static const FlagsType | Initialized = 0x7a40 |

| static const FlagsType | InitMask = 0xffc0 |

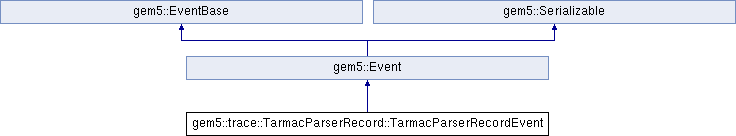

Detailed Description

Event triggered to check the value of the destination registers.

Needed to handle some cases where registers are modified after the trace record has been dumped. E.g., the SVC instruction updates the CPSR and SPSR as part of the fault handling routine.

Definition at line 76 of file tarmac_parser.hh.

Constructor & Destructor Documentation

◆ TarmacParserRecordEvent()

|

inline |

Definition at line 96 of file tarmac_parser.hh.

References inst, mismatch, mismatchOnPcOrOpcode, parent, pc, and thread.

Member Function Documentation

◆ description()

|

virtual |

Return a C string describing the event.

This string should not be dynamically allocated; just a const char array describing the event class.

Reimplemented from gem5::Event.

Definition at line 939 of file tarmac_parser.cc.

◆ process()

|

virtual |

Implements gem5::Event.

Definition at line 758 of file tarmac_parser.cc.

References gem5::VecRegContainer< SIZE >::as(), gem5::ArmISA::cc_reg::C, gem5::trace::TarmacParserRecord::destRegRecords, gem5::exitSimLoop(), gem5::ArmISA::cc_reg::Ge, gem5::ArmISA::i, inst, gem5::trace::TarmacParserRecord::instRecord, gem5::ArmISA::intRegClass, gem5::trace::TarmacBaseRecord::ISET_A64, gem5::trace::TarmacParserRecord::maxVectorLength, gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_FPCR, gem5::ArmISA::MISCREG_FPSCR, gem5::ArmISA::MISCREG_FPSR, gem5::ArmISA::MISCREG_NZCV, mismatch, mismatchOnPcOrOpcode, gem5::ArmISA::cc_reg::Nz, gem5::trace::output(), gem5::MipsISA::p, panic, parent, pc, gem5::trace::TarmacParserRecord::printMismatchHeader(), gem5::trace::TarmacBaseRecord::REG_D, gem5::trace::TarmacBaseRecord::REG_MISC, gem5::trace::TarmacBaseRecord::REG_P, gem5::trace::TarmacBaseRecord::REG_Q, gem5::trace::TarmacBaseRecord::REG_R, gem5::trace::TarmacBaseRecord::REG_S, gem5::trace::TarmacBaseRecord::REG_X, gem5::trace::TarmacBaseRecord::REG_Z, gem5::trace::InstRecord::size, thread, gem5::ArmISA::cc_reg::V, gem5::ArmISA::v, gem5::ArmISA::vecElemClass, gem5::ArmISA::vecPredRegClass, and gem5::ArmISA::vecRegClass.

Member Data Documentation

◆ inst

| const StaticInstPtr gem5::trace::TarmacParserRecord::TarmacParserRecordEvent::inst |

Current instruction.

Definition at line 85 of file tarmac_parser.hh.

Referenced by process(), and TarmacParserRecordEvent().

◆ mismatch

| bool gem5::trace::TarmacParserRecord::TarmacParserRecordEvent::mismatch |

True if a mismatch has been detected for this instruction.

Definition at line 89 of file tarmac_parser.hh.

Referenced by process(), and TarmacParserRecordEvent().

◆ mismatchOnPcOrOpcode

| bool gem5::trace::TarmacParserRecord::TarmacParserRecordEvent::mismatchOnPcOrOpcode |

True if a mismatch has been detected for this instruction on PC or opcode.

Definition at line 94 of file tarmac_parser.hh.

Referenced by process(), and TarmacParserRecordEvent().

◆ parent

| TarmacParser& gem5::trace::TarmacParserRecord::TarmacParserRecordEvent::parent |

Reference to the TARMAC trace object to which this record belongs.

Definition at line 81 of file tarmac_parser.hh.

Referenced by process(), and TarmacParserRecordEvent().

◆ pc

| std::unique_ptr<PCStateBase> gem5::trace::TarmacParserRecord::TarmacParserRecordEvent::pc |

PC of the current instruction.

Definition at line 87 of file tarmac_parser.hh.

Referenced by process(), and TarmacParserRecordEvent().

◆ thread

| ThreadContext* gem5::trace::TarmacParserRecord::TarmacParserRecordEvent::thread |

Current thread context.

Definition at line 83 of file tarmac_parser.hh.

Referenced by process(), and TarmacParserRecordEvent().

The documentation for this struct was generated from the following files:

- arch/arm/tracers/tarmac_parser.hh

- arch/arm/tracers/tarmac_parser.cc

Generated on Sat Oct 18 2025 08:07:04 for gem5 by doxygen 1.14.0