#include <faults.hh>

Public Member Functions | |

| bool | routeToMonitor (ThreadContext *tc) const override |

| bool | routeToHyp (ThreadContext *tc) const override |

| bool | abortDisable (ThreadContext *tc) override |

| uint32_t | vectorCatchFlag () const override |

Public Member Functions inherited from gem5::ArmISA::ArmFaultVals< Interrupt > Public Member Functions inherited from gem5::ArmISA::ArmFaultVals< Interrupt > | |

| ArmFaultVals (ExtMachInst mach_inst=0, uint32_t _iss=0) | |

| FaultName | name () const override |

| FaultOffset | offset (ThreadContext *tc) override |

| FaultOffset | offset64 (ThreadContext *tc) override |

| OperatingMode | nextMode () override |

| uint8_t | armPcOffset (bool is_hyp) override |

| uint8_t | thumbPcOffset (bool is_hyp) override |

| uint8_t | armPcElrOffset () override |

| uint8_t | thumbPcElrOffset () override |

| bool | fiqDisable (ThreadContext *tc) override |

| ExceptionClass | ec (ThreadContext *tc) const override |

| Syndrome methods. | |

| bool | il (ThreadContext *tc) const override |

| uint32_t | iss () const override |

Public Member Functions inherited from gem5::ArmISA::ArmFault Public Member Functions inherited from gem5::ArmISA::ArmFault | |

| ArmFault (ExtMachInst mach_inst=0, uint32_t _iss=0) | |

| MiscRegIndex | getSyndromeReg64 () const |

| void | invoke (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) override |

| void | invoke32 (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

| void | invoke64 (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

| virtual void | update (ThreadContext *tc) |

| bool | isResetSPSR () |

| bool | vectorCatch (ThreadContext *tc, const StaticInstPtr &inst) |

| ArmStaticInst * | instrAnnotate (const StaticInstPtr &inst) |

| virtual void | annotate (AnnotationIDs id, uint64_t val) |

| virtual bool | isStage2 () const |

| virtual FSR | getFsr (ThreadContext *tc) const |

| virtual void | setSyndrome (ThreadContext *tc, MiscRegIndex syndrome_reg) |

| virtual bool | getFaultVAddr (Addr &va) const |

| OperatingMode | getToMode () const |

| virtual bool | isExternalAbort () const |

Public Member Functions inherited from gem5::FaultBase Public Member Functions inherited from gem5::FaultBase | |

| virtual | ~FaultBase () |

Additional Inherited Members | |

Public Types inherited from gem5::ArmISA::ArmFault Public Types inherited from gem5::ArmISA::ArmFault | |

| enum | FaultSource { AlignmentFault = 0 , InstructionCacheMaintenance , SynchExtAbtOnTranslTableWalkLL , SynchPtyErrOnTranslTableWalkLL = SynchExtAbtOnTranslTableWalkLL + 4 , TranslationLL = SynchPtyErrOnTranslTableWalkLL + 4 , AccessFlagLL = TranslationLL + 4 , DomainLL = AccessFlagLL + 4 , PermissionLL = DomainLL + 4 , DebugEvent = PermissionLL + 4 , SynchronousExternalAbort , TLBConflictAbort , SynchPtyErrOnMemoryAccess , AsynchronousExternalAbort , AsynchPtyErrOnMemoryAccess , AddressSizeLL , PrefetchTLBMiss = AddressSizeLL + 4 , PrefetchUncacheable , NumFaultSources , FaultSourceInvalid = 0xff } |

| Generic fault source enums used to index into {short/long/aarch64}DescFaultSources[] to get the actual encodings based on the current register width state and the translation table format in use. More... | |

| enum | AnnotationIDs { S1PTW , OVA , SAS , SSE , SRT , CM , OFA , WnR , SF , AR } |

| enum | DebugType { NODEBUG = 0 , BRKPOINT , VECTORCATCH , WPOINT_CM , WPOINT_NOCM } |

Static Public Attributes inherited from gem5::ArmISA::ArmFault Static Public Attributes inherited from gem5::ArmISA::ArmFault | |

| static uint8_t | shortDescFaultSources [NumFaultSources] |

| Encodings of the fault sources when the short-desc. | |

| static uint8_t | longDescFaultSources [NumFaultSources] |

| Encodings of the fault sources when the long-desc. | |

| static uint8_t | aarch64FaultSources [NumFaultSources] |

| Encodings of the fault sources in AArch64 state. | |

Protected Member Functions inherited from gem5::ArmISA::ArmFaultVals< Interrupt > Protected Member Functions inherited from gem5::ArmISA::ArmFaultVals< Interrupt > | |

| ArmFault::FaultVals | vals ("Reset", 0x000, 0x000, 0x000, 0x000, 0x000, MODE_SVC, 0, 0, 0, 0, false, true, true, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals ("Undefined Instruction", 0x004, 0x000, 0x200, 0x400, 0x600, MODE_UNDEFINED, 4, 2, 0, 0, true, false, false, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals ("Supervisor Call", 0x008, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 4, 2, 4, 2, true, false, false, ExceptionClass::SVC_TO_HYP) |

| ArmFault::FaultVals | vals ("Secure Monitor Call", 0x008, 0x000, 0x200, 0x400, 0x600, MODE_MON, 4, 4, 4, 4, false, true, true, ExceptionClass::SMC_TO_HYP) |

| ArmFault::FaultVals | vals ("Hypervisor Call", 0x008, 0x000, 0x200, 0x400, 0x600, MODE_HYP, 4, 4, 4, 4, true, false, false, ExceptionClass::HVC) |

| ArmFault::FaultVals | vals ("Prefetch Abort", 0x00C, 0x000, 0x200, 0x400, 0x600, MODE_ABORT, 4, 4, 0, 0, true, true, false, ExceptionClass::PREFETCH_ABORT_TO_HYP) |

| ArmFault::FaultVals | vals ("Data Abort", 0x010, 0x000, 0x200, 0x400, 0x600, MODE_ABORT, 8, 8, 0, 0, true, true, false, ExceptionClass::DATA_ABORT_TO_HYP) |

| ArmFault::FaultVals | vals ("Virtual Data Abort", 0x010, 0x000, 0x200, 0x400, 0x600, MODE_ABORT, 8, 8, 0, 0, true, true, false, ExceptionClass::INVALID) |

| ArmFault::FaultVals | vals ("Hypervisor Trap", 0x014, 0x000, 0x200, 0x400, 0x600, MODE_HYP, 0, 0, 0, 0, false, false, false, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals ("Secure Monitor Trap", 0x004, 0x000, 0x200, 0x400, 0x600, MODE_MON, 4, 2, 0, 0, false, false, false, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals ("IRQ", 0x018, 0x080, 0x280, 0x480, 0x680, MODE_IRQ, 4, 4, 0, 0, false, true, false, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals ("Virtual IRQ", 0x018, 0x080, 0x280, 0x480, 0x680, MODE_IRQ, 4, 4, 0, 0, false, true, false, ExceptionClass::INVALID) |

| ArmFault::FaultVals | vals ("FIQ", 0x01C, 0x100, 0x300, 0x500, 0x700, MODE_FIQ, 4, 4, 0, 0, false, true, true, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals ("Virtual FIQ", 0x01C, 0x100, 0x300, 0x500, 0x700, MODE_FIQ, 4, 4, 0, 0, false, true, true, ExceptionClass::INVALID) |

| ArmFault::FaultVals | vals ("Illegal Inst Set State Fault", 0x004, 0x000, 0x200, 0x400, 0x600, MODE_UNDEFINED, 4, 2, 0, 0, true, false, false, ExceptionClass::ILLEGAL_INST) |

| ArmFault::FaultVals | vals ("Supervisor Trap", 0x014, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 0, 0, 0, 0, false, false, false, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals ("PC Alignment Fault", 0x000, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 0, 0, 0, 0, true, false, false, ExceptionClass::PC_ALIGNMENT) |

| ArmFault::FaultVals | vals ("SP Alignment Fault", 0x000, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 0, 0, 0, 0, true, false, false, ExceptionClass::STACK_PTR_ALIGNMENT) |

| ArmFault::FaultVals | vals ("SError", 0x000, 0x180, 0x380, 0x580, 0x780, MODE_SVC, 0, 0, 0, 0, false, true, true, ExceptionClass::SERROR) |

| ArmFault::FaultVals | vals ("Software Breakpoint", 0x000, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 0, 0, 0, 0, true, false, false, ExceptionClass::SOFTWARE_BREAKPOINT) |

| ArmFault::FaultVals | vals ("Hardware Breakpoint", 0x000, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 0, 0, 0, 0, true, false, false, ExceptionClass::HW_BREAKPOINT) |

| ArmFault::FaultVals | vals ("Watchpoint", 0x000, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 0, 0, 0, 0, true, false, false, ExceptionClass::WATCHPOINT) |

| ArmFault::FaultVals | vals ("SoftwareStep", 0x000, 0x000, 0x200, 0x400, 0x600, MODE_SVC, 0, 0, 0, 0, true, false, false, ExceptionClass::SOFTWARE_STEP) |

| ArmFault::FaultVals | vals ("ArmSev Flush", 0x000, 0x000, 0x000, 0x000, 0x000, MODE_SVC, 0, 0, 0, 0, false, true, true, ExceptionClass::UNKNOWN) |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

| ArmFault::FaultVals | vals |

Protected Member Functions inherited from gem5::ArmISA::ArmFault Protected Member Functions inherited from gem5::ArmISA::ArmFault | |

| virtual Addr | getVector (ThreadContext *tc) |

| Addr | getVector64 (ThreadContext *tc) |

Protected Attributes inherited from gem5::ArmISA::ArmFault Protected Attributes inherited from gem5::ArmISA::ArmFault | |

| ExtMachInst | machInst |

| uint32_t | issRaw |

| bool | bStep |

| bool | from64 |

| bool | to64 |

| ExceptionLevel | fromEL |

| ExceptionLevel | toEL |

| OperatingMode | fromMode |

| OperatingMode | toMode |

| bool | faultUpdated |

| bool | hypRouted |

| bool | span |

Static Protected Attributes inherited from gem5::ArmISA::ArmFaultVals< Interrupt > Static Protected Attributes inherited from gem5::ArmISA::ArmFaultVals< Interrupt > | |

| static FaultVals | vals |

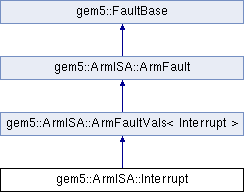

Detailed Description

Member Function Documentation

◆ abortDisable()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFaultVals< Interrupt >.

Definition at line 1468 of file faults.cc.

References gem5::ArmISA::EL3, gem5::ArmSystem::haveEL(), gem5::ArmISA::MISCREG_SCR_EL3, and gem5::ThreadContext::readMiscRegNoEffect().

◆ routeToHyp()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Definition at line 1460 of file faults.cc.

References gem5::ArmISA::EL1, gem5::ArmISA::EL2, gem5::ArmISA::EL2Enabled(), gem5::ArmISA::ArmFault::fromEL, gem5::ArmISA::MISCREG_HCR_EL2, and gem5::ThreadContext::readMiscRegNoEffect().

◆ routeToMonitor()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFaultVals< Interrupt >.

Definition at line 1452 of file faults.cc.

References gem5::ArmISA::EL3, gem5::ArmSystem::haveEL(), gem5::ArmISA::MISCREG_SCR_EL3, and gem5::ThreadContext::readMiscRegNoEffect().

◆ vectorCatchFlag()

|

inlineoverridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

The documentation for this class was generated from the following files: