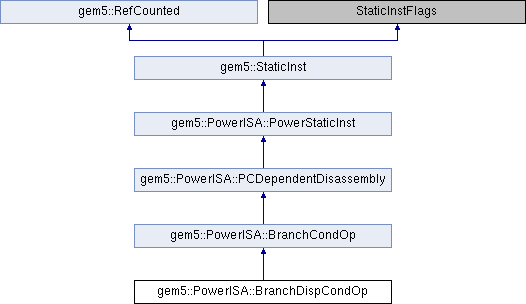

Base class for conditional, PC-relative or absolute address branches. More...

#include <branch.hh>

Protected Member Functions | |

| BranchDispCondOp (const char *mnem, MachInst _machInst, OpClass __opClass) | |

| Constructor. | |

| std::unique_ptr< PCStateBase > | branchTarget (ThreadContext *tc) const override |

| Return the target address for an indirect branch (jump). | |

| std::string | generateDisassembly (Addr pc, const loader::SymbolTable *symtab) const override |

| Internal function to generate disassembly string. | |

| virtual std::unique_ptr< PCStateBase > | branchTarget (const PCStateBase &pc) const |

| Explicitly import the otherwise hidden branchTarget. | |

| Protected Member Functions inherited from gem5::PowerISA::BranchCondOp | |

| BranchCondOp (const char *mnem, MachInst _machInst, OpClass __opClass) | |

| Constructor. | |

| bool | ctrOk (uint64_t &ctr) const |

| bool | condOk (uint32_t cr) const |

| Protected Member Functions inherited from gem5::PowerISA::PCDependentDisassembly | |

| PCDependentDisassembly (const char *mnem, ExtMachInst _machInst, OpClass __opClass) | |

| Constructor. | |

| const std::string & | disassemble (Addr pc, const loader::SymbolTable *symtab) const |

| Return string representation of disassembled instruction. | |

| Protected Member Functions inherited from gem5::PowerISA::PowerStaticInst | |

| PowerStaticInst (const char *mnem, ExtMachInst _machInst, OpClass __opClass) | |

| uint32_t | insertCRField (uint32_t cr, uint32_t bf, uint32_t value) const |

| void | printReg (std::ostream &os, RegId reg) const |

| Print a register name for disassembly given the unique dependence tag number (FP or int). | |

| std::string | generateDisassembly (Addr pc, const loader::SymbolTable *symtab) const override |

| Internal function to generate disassembly string. | |

| void | advancePC (PCStateBase &pc_state) const override |

| void | advancePC (ThreadContext *tc) const override |

| std::unique_ptr< PCStateBase > | buildRetPC (const PCStateBase &cur_pc, const PCStateBase &call_pc) const override |

| size_t | asBytes (void *buf, size_t max_size) override |

| Instruction classes can override this function to return a a representation of themselves as a blob of bytes, generally assumed to be that instructions ExtMachInst. | |

| void | setRegIdxArrays (RegIdArrayPtr src, RegIdArrayPtr dest) |

| Set the pointers which point to the arrays of source and destination register indices. | |

| StaticInst (const char *_mnemonic, OpClass op_class) | |

| Constructor. | |

| template<typename T> | |

| size_t | simpleAsBytes (void *buf, size_t max_size, const T &t) |

Protected Attributes | |

| bool | aa |

| int64_t | bd |

| Protected Attributes inherited from gem5::PowerISA::BranchCondOp | |

| bool | lk |

| uint8_t | bi |

| uint8_t | bo |

| Protected Attributes inherited from gem5::PowerISA::PCDependentDisassembly | |

| Addr | cachedPC |

| Cached program counter from last disassembly. | |

| const loader::SymbolTable * | cachedSymtab |

| Cached symbol table pointer from last disassembly. | |

| Protected Attributes inherited from gem5::PowerISA::PowerStaticInst | |

| ExtMachInst | machInst |

| Protected Attributes inherited from gem5::StaticInst | |

| std::bitset< Num_Flags > | flags |

| Flag values for this instruction. | |

| OpClass | _opClass |

| See opClass(). | |

| uint8_t | _numSrcRegs = 0 |

| See numSrcRegs(). | |

| uint8_t | _numDestRegs = 0 |

| See numDestRegs(). | |

| std::array< uint8_t, MiscRegClass+1 > | _numTypedDestRegs = {} |

| size_t | _size = 0 |

| Instruction size in bytes. | |

| const char * | mnemonic |

| Base mnemonic (e.g., "add"). | |

| std::unique_ptr< std::string > | cachedDisassembly |

| String representation of disassembly (lazily evaluated via disassemble()). | |

Additional Inherited Members | |

| Public Types inherited from gem5::StaticInst | |

| using | RegIdArrayPtr = RegId (StaticInst:: *)[] |

| Public Member Functions inherited from gem5::StaticInst | |

| uint8_t | numSrcRegs () const |

| Number of source registers. | |

| uint8_t | numDestRegs () const |

| Number of destination registers. | |

| uint8_t | numDestRegs (RegClassType type) const |

| Number of destination registers of a particular type. | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isMatrix () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isFullMemBarrier () const |

| bool | isReadBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isUnverifiable () const |

| bool | isPseudo () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isInvalid () const |

| bool | isHtmCmd () const |

| void | setFirstMicroop () |

| void | setLastMicroop () |

| void | setDelayedCommit () |

| void | setFlag (Flags f) |

| OpClass | opClass () const |

| Operation class. Used to select appropriate function unit in issue. | |

| const RegId & | destRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th destination reg. | |

| void | setDestRegIdx (int i, const RegId &val) |

| const RegId & | srcRegIdx (int i) const |

| Return logical index (architectural reg num) of i'th source reg. | |

| void | setSrcRegIdx (int i, const RegId &val) |

| virtual uint64_t | getEMI () const |

| virtual | ~StaticInst () |

| virtual Fault | execute (ExecContext *xc, trace::InstRecord *traceData) const =0 |

| virtual Fault | initiateAcc (ExecContext *xc, trace::InstRecord *traceData) const |

| virtual Fault | completeAcc (Packet *pkt, ExecContext *xc, trace::InstRecord *trace_data) const |

| size_t | size () const |

| virtual void | size (size_t newSize) |

| virtual StaticInstPtr | fetchMicroop (MicroPC upc) const |

| Return the microop that goes with a particular micropc. | |

| void | printFlags (std::ostream &outs, const std::string &separator) const |

| Print a separator separated list of this instruction's set flag names on the given stream. | |

| std::string | getName () |

| Return name of machine instruction. | |

| Public Member Functions inherited from gem5::RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. | |

| void | incref () const |

| Increment the reference count. | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. | |

| static StaticInstPtr | nullStaticInstPtr |

| Pointer to a statically allocated "null" instruction object. | |

Detailed Description

Base class for conditional, PC-relative or absolute address branches.

Constructor & Destructor Documentation

◆ BranchDispCondOp()

|

inlineprotected |

Constructor.

Definition at line 156 of file branch.hh.

References aa, bd, gem5::PowerISA::BranchCondOp::BranchCondOp(), gem5::PowerISA::PowerStaticInst::machInst, and gem5::sext().

Member Function Documentation

◆ branchTarget() [1/2]

|

protectedvirtual |

Explicitly import the otherwise hidden branchTarget.

Reimplemented from gem5::StaticInst.

Definition at line 341 of file static_inst.cc.

◆ branchTarget() [2/2]

|

overrideprotectedvirtual |

Return the target address for an indirect branch (jump).

The register value is read from the supplied thread context, so the result is valid only if the thread context is about to execute the branch in question. Invalid if not an indirect branch (i.e. isIndirectCtrl() should be true).

Reimplemented from gem5::StaticInst.

Definition at line 109 of file branch.cc.

References aa, gem5::X86ISA::addr, bd, gem5::ThreadContext::getReg(), gem5::PCStateBase::instAddr(), gem5::PowerISA::int_reg::Msr, and gem5::ThreadContext::pcState().

◆ generateDisassembly()

|

overrideprotectedvirtual |

Internal function to generate disassembly string.

Implements gem5::StaticInst.

Definition at line 125 of file branch.cc.

References aa, bd, gem5::PowerISA::BranchCondOp::bi, gem5::PowerISA::BranchCondOp::bo, gem5::ccprintf(), gem5::loader::SymbolTable::end(), gem5::loader::SymbolTable::find(), gem5::PowerISA::BranchCondOp::lk, gem5::StaticInst::mnemonic, gem5::MipsISA::pc, and gem5::ArmISA::ss.

Member Data Documentation

◆ aa

|

protected |

Definition at line 152 of file branch.hh.

Referenced by BranchDispCondOp(), branchTarget(), and generateDisassembly().

◆ bd

|

protected |

Definition at line 153 of file branch.hh.

Referenced by BranchDispCondOp(), branchTarget(), and generateDisassembly().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:07:00 for gem5 by doxygen 1.14.0