#include <tlb.hh>

Classes | |

| class | CpuSidePort |

| class | MemSidePort |

| MemSidePort is the TLB Port closer to the memory side If this is a last level TLB then this port will not be connected. More... | |

| class | TLBEvent |

| class | Translation |

| struct | VegaTLBStats |

Public Types | |

| enum | tlbOutcome { TLB_HIT , TLB_MISS , PAGE_WALK , MISS_RETURN } |

| typedef enum BaseMMU::Mode | Mode |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| GpuTLB (const VegaGPUTLBParams &p) | |

| ~GpuTLB () | |

| Addr | pageAlign (Addr vaddr) |

| void | dumpAll () |

| VegaTlbEntry * | lookup (Addr va, bool update_lru=true) |

| Walker * | getWalker () |

| void | invalidateAll () |

| void | demapPage (Addr va, uint64_t asn) |

| VegaTlbEntry * | insert (Addr vpn, VegaTlbEntry &entry) |

| virtual void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| virtual void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| void | issueTranslation () |

| VegaTlbEntry * | tlbLookup (const RequestPtr &req, bool update_stats) |

| TLB_lookup will only perform a TLB lookup returning the TLB entry on a TLB hit and nullptr on a TLB miss. | |

| void | walkerResponse (VegaTlbEntry &entry, PacketPtr pkt) |

| void | handleTranslationReturn (Addr addr, tlbOutcome outcome, PacketPtr pkt) |

| handleTranslationReturn is called on a TLB hit, when a TLB miss returns or when a page fault returns. | |

| void | handleFuncTranslationReturn (PacketPtr pkt, tlbOutcome outcome) |

| handleFuncTranslationReturn is called on a TLB hit, when a TLB miss returns or when a page fault returns. | |

| void | pagingProtectionChecks (PacketPtr pkt, VegaTlbEntry *tlb_entry, Mode mode) |

| Do Paging protection checks. | |

| void | updatePhysAddresses (Addr virt_page_addr, VegaTlbEntry *tlb_entry, Addr phys_page_addr) |

| void | issueTLBLookup (PacketPtr pkt) |

| Do the TLB lookup for this coalesced request and schedule another event <TLB access latency> cycles later. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Fault | createPagefault (Addr vaddr, Mode mode) |

| void | translationReturn (Addr virtPageAddr, tlbOutcome outcome, PacketPtr pkt) |

| A TLBEvent is scheduled after the TLB lookup and helps us take the appropriate actions: (e.g., update TLB on a hit, send request to lower level TLB on a miss, or start a page walk if this was the last-level TLB). | |

| void | cleanup () |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Public Attributes | |

| int | hitLatency |

| int | missLatency1 |

| int | missLatency2 |

| gem5::VegaISA::GpuTLB::VegaTLBStats | stats |

| std::vector< CpuSidePort * > | cpuSidePort |

| std::vector< MemSidePort * > | memSidePort |

| int | maxCoalescedReqs |

| int | outstandingReqs |

| std::unordered_map< Addr, TLBEvent * > | translationReturnEvent |

| std::queue< Addr > | cleanupQueue |

| EventFunctionWrapper | cleanupEvent |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Protected Types | |

| typedef std::list< VegaTlbEntry * > | EntryList |

Protected Member Functions | |

| EntryList::iterator | lookupIt (Addr va, bool update_lru=true) |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| Walker * | walker |

| AMDGPUDevice * | gpuDevice |

| int | size |

| int | assoc |

| int | numSets |

| bool | FA |

| true if this is a fully-associative TLB | |

| Addr | setMask |

| bool | allocationPolicy |

| Allocation Policy: true if we always allocate on a hit, false otherwise. | |

| bool | hasMemSidePort |

| if true, then this is not the last level TLB | |

| std::vector< VegaTlbEntry > | tlb |

| std::vector< EntryList > | freeList |

| std::vector< EntryList > | entryList |

| An entryList per set is the equivalent of an LRU stack; it's used to guide replacement decisions. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

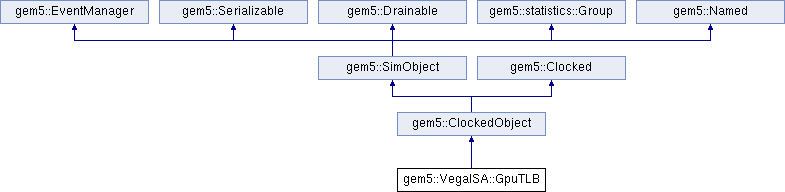

Detailed Description

Member Typedef Documentation

◆ EntryList

|

protected |

◆ Mode

| typedef enum BaseMMU::Mode gem5::VegaISA::GpuTLB::Mode |

Member Enumeration Documentation

◆ tlbOutcome

Constructor & Destructor Documentation

◆ GpuTLB()

| gem5::VegaISA::GpuTLB::GpuTLB | ( | const VegaGPUTLBParams & | p | ) |

Definition at line 52 of file tlb.cc.

References cleanup(), cleanupEvent, gem5::ClockedObject::ClockedObject(), gpuDevice, gem5::VegaISA::p, size, stats, and walker.

Referenced by gem5::VegaISA::GpuTLB::CpuSidePort::CpuSidePort(), gem5::VegaISA::GpuTLB::MemSidePort::MemSidePort(), and gem5::VegaISA::GpuTLB::TLBEvent::TLBEvent().

◆ ~GpuTLB()

Member Function Documentation

◆ cleanup()

| void gem5::VegaISA::GpuTLB::cleanup | ( | ) |

the higher level coalescer should retry if it has any pending requests.

Definition at line 940 of file tlb.cc.

References cleanupQueue, cpuSidePort, DPRINTF, gem5::ArmISA::i, outstandingReqs, and translationReturnEvent.

Referenced by GpuTLB().

◆ createPagefault()

Definition at line 136 of file tlb.cc.

References DPRINTF, gem5::VegaISA::INST_PAGE, gem5::VegaISA::LOAD_PAGE, gem5::ArmISA::mode, gem5::BaseMMU::Read, gem5::VegaISA::STORE_PAGE, gem5::MipsISA::vaddr, and gem5::BaseMMU::Write.

◆ demapPage()

| void gem5::VegaISA::GpuTLB::demapPage | ( | Addr | va, |

| uint64_t | asn ) |

Definition at line 238 of file tlb.cc.

References entryList, freeList, lookupIt(), gem5::VegaISA::PageShift, gem5::ArmISA::set, setMask, and gem5::ArmISA::va.

◆ dumpAll()

| void gem5::VegaISA::GpuTLB::dumpAll | ( | ) |

References gem5::ArmISA::va.

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

gem5 has a request and response port interface. All memory objects are connected together via ports. These ports provide a rigid interface between these memory objects. These ports implement three different memory system modes: timing, atomic, and functional. The most important mode is the timing mode and here timing mode is used for conducting cycle-level timing experiments. The other modes are only used in special circumstances and should not be used to conduct cycle-level timing experiments. The other modes are only used in special circumstances. These ports allow SimObjects to communicate with each other.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from gem5::SimObject.

Definition at line 114 of file tlb.cc.

References cpuSidePort, hasMemSidePort, memSidePort, and panic.

◆ getWalker()

| Walker * gem5::VegaISA::GpuTLB::getWalker | ( | ) |

◆ handleFuncTranslationReturn()

| void gem5::VegaISA::GpuTLB::handleFuncTranslationReturn | ( | PacketPtr | pkt, |

| tlbOutcome | tlb_outcome ) |

handleFuncTranslationReturn is called on a TLB hit, when a TLB miss returns or when a page fault returns.

It updates LRU, inserts the TLB entry on a miss depending on the allocation policy and does the required protection checks. It does NOT create a new packet to update the packet's addr; this is done in hsail-gpu code.

We are returning either from a page walk or from a hit at a lower TLB level. The senderState should be "carrying" a pointer to the correct TLBEntry.

Do paging checks if it's a normal functional access. If it's for a prefetch, then sometimes you can try to prefetch something that won't pass protection. We don't actually want to fault becuase there is no demand access to deem this a violation. Just put it in the TLB and it will fault if indeed a future demand access touches it in violation.

This feature could be used to explore security issues around speculative memory accesses.

Definition at line 703 of file tlb.cc.

References allocationPolicy, DPRINTF, insert(), gem5::GpuTranslationState::isPrefetch, gem5::ArmISA::mode, gem5::VegaISA::PageBytes, pagingProtectionChecks(), gem5::Packet::req, gem5::roundDown(), gem5::safe_cast(), gem5::Packet::senderState, TLB_HIT, gem5::GpuTranslationState::tlbEntry, gem5::GpuTranslationState::tlbMode, gem5::Request::UNCACHEABLE, and gem5::MipsISA::vaddr.

◆ handleTranslationReturn()

| void gem5::VegaISA::GpuTLB::handleTranslationReturn | ( | Addr | virt_page_addr, |

| tlbOutcome | tlb_outcome, | ||

| PacketPtr | pkt ) |

handleTranslationReturn is called on a TLB hit, when a TLB miss returns or when a page fault returns.

The latter calls handelHit with TLB miss as tlbOutcome.

We are returning either from a page walk or from a hit at a lower TLB level. The senderState should be "carrying" a pointer to the correct TLBEntry.

At this point the packet carries an up-to-date tlbEntry pointer in its senderState. Next step is to do the paging protection checks.

Definition at line 459 of file tlb.cc.

References allocationPolicy, cleanupEvent, cleanupQueue, cpuSidePort, gem5::Clocked::curCycle(), gem5::curTick(), DPRINTF, insert(), gem5::GpuTranslationState::isPrefetch, gem5::Packet::isRequest(), gem5::Packet::makeTimingResponse(), gem5::ArmISA::mode, pagingProtectionChecks(), gem5::Packet::req, gem5::GpuTranslationState::reqCnt, gem5::safe_cast(), gem5::EventManager::schedule(), gem5::Packet::senderState, stats, TLB_HIT, gem5::GpuTranslationState::tlbEntry, gem5::GpuTranslationState::tlbMode, gem5::Request::UNCACHEABLE, and gem5::MipsISA::vaddr.

Referenced by translationReturn(), and walkerResponse().

◆ insert()

| VegaTlbEntry * gem5::VegaISA::GpuTLB::insert | ( | Addr | vpn, |

| VegaTlbEntry & | entry ) |

Definition at line 157 of file tlb.cc.

References DPRINTF, entryList, freeList, gem5::VegaISA::PageShift, gem5::ArmISA::set, and setMask.

Referenced by handleFuncTranslationReturn(), and handleTranslationReturn().

◆ invalidateAll()

| void gem5::VegaISA::GpuTLB::invalidateAll | ( | ) |

◆ issueTLBLookup()

| void gem5::VegaISA::GpuTLB::issueTLBLookup | ( | PacketPtr | pkt | ) |

Do the TLB lookup for this coalesced request and schedule another event <TLB access latency> cycles later.

The page size is not fixed in Vega and tracking events by VPN could potentially lead to redundant page walks by using the smallest page size. The actual VPN can be determined after the first walk is done and fixed up later.

Definition at line 313 of file tlb.cc.

References gem5::Clocked::curCycle(), gem5::curTick(), gem5::Clocked::cyclesToTicks(), DPRINTF, hitLatency, gem5::GpuTranslationState::hitLevel, gem5::GpuTranslationState::isPrefetch, lookup(), gem5::VegaISA::PageBytes, panic, gem5::Packet::req, gem5::GpuTranslationState::reqCnt, gem5::roundDown(), gem5::safe_cast(), gem5::EventManager::schedule(), gem5::Packet::senderState, stats, TLB_HIT, TLB_MISS, gem5::GpuTranslationState::tlbEntry, tlbLookup(), and translationReturnEvent.

◆ issueTranslation()

| void gem5::VegaISA::GpuTLB::issueTranslation | ( | ) |

◆ lookup()

| VegaTlbEntry * gem5::VegaISA::GpuTLB::lookup | ( | Addr | va, |

| bool | update_lru = true ) |

Definition at line 211 of file tlb.cc.

References entryList, lookupIt(), gem5::VegaISA::PageShift, gem5::ArmISA::set, setMask, and gem5::ArmISA::va.

Referenced by issueTLBLookup(), and tlbLookup().

◆ lookupIt()

|

protected |

Definition at line 181 of file tlb.cc.

References DPRINTF, entryList, FA, gem5::VegaISA::PageShift, gem5::ArmISA::set, setMask, and gem5::ArmISA::va.

Referenced by demapPage(), and lookup().

◆ pageAlign()

Definition at line 150 of file tlb.cc.

References gem5::ArmISA::mask, gem5::VegaISA::PageShift, and gem5::MipsISA::vaddr.

Referenced by tlbLookup().

◆ pagingProtectionChecks()

| void gem5::VegaISA::GpuTLB::pagingProtectionChecks | ( | PacketPtr | pkt, |

| VegaTlbEntry * | tlb_entry, | ||

| Mode | mode ) |

Do Paging protection checks.

If we encounter a page fault, then an assertion is fired.

Definition at line 417 of file tlb.cc.

References fatal, gem5::ArmISA::mode, gem5::Packet::req, and gem5::BaseMMU::Write.

Referenced by handleFuncTranslationReturn(), and handleTranslationReturn().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

◆ tlbLookup()

| VegaTlbEntry * gem5::VegaISA::GpuTLB::tlbLookup | ( | const RequestPtr & | req, |

| bool | update_stats ) |

TLB_lookup will only perform a TLB lookup returning the TLB entry on a TLB hit and nullptr on a TLB miss.

Many of the checks about different modes have been converted to assertions, since these parts of the code are not really used. On a hit it will update the LRU stack.

Definition at line 260 of file tlb.cc.

References DPRINTF, lookup(), pageAlign(), stats, and gem5::MipsISA::vaddr.

Referenced by issueTLBLookup().

◆ translationReturn()

| void gem5::VegaISA::GpuTLB::translationReturn | ( | Addr | virtPageAddr, |

| tlbOutcome | outcome, | ||

| PacketPtr | pkt ) |

A TLBEvent is scheduled after the TLB lookup and helps us take the appropriate actions: (e.g., update TLB on a hit, send request to lower level TLB on a miss, or start a page walk if this was the last-level TLB).

Here we take the appropriate actions based on the result of the TLB lookup.

There is a TLB below. Send the coalesced request. We actually send the very first packet of all the pending packets for this virtual page address.

we add an extra cycle in the return path of the translation requests in between the various TLB levels.

Definition at line 556 of file tlb.cc.

References gem5::RiscvISA::base, gem5::Clocked::curCycle(), gem5::curTick(), gem5::Clocked::cyclesToTicks(), gem5::GpuTranslationState::deviceId, DPRINTF, gpuDevice, handleTranslationReturn(), hasMemSidePort, gem5::GpuTranslationState::isPrefetch, memSidePort, MISS_RETURN, missLatency2, PAGE_WALK, panic, gem5::GpuTranslationState::pasId, gem5::BaseMMU::Read, gem5::Packet::req, gem5::GpuTranslationState::reqCnt, gem5::safe_cast(), gem5::EventManager::schedule(), gem5::Packet::senderState, stats, TLB_HIT, TLB_MISS, translationReturnEvent, gem5::VegaISA::GpuTLB::TLBEvent::updateOutcome(), gem5::MipsISA::vaddr, and walker.

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

◆ updatePhysAddresses()

| void gem5::VegaISA::GpuTLB::updatePhysAddresses | ( | Addr | virt_page_addr, |

| VegaTlbEntry * | tlb_entry, | ||

| Addr | phys_page_addr ) |

◆ walkerResponse()

| void gem5::VegaISA::GpuTLB::walkerResponse | ( | VegaTlbEntry & | entry, |

| PacketPtr | pkt ) |

Definition at line 433 of file tlb.cc.

References DPRINTF, handleTranslationReturn(), gem5::ArmISA::mask, gem5::VegaISA::PageBytes, gem5::VegaISA::PageShift, gem5::Packet::req, gem5::roundDown(), gem5::safe_cast(), gem5::Packet::senderState, TLB_MISS, and gem5::GpuTranslationState::tlbEntry.

Member Data Documentation

◆ allocationPolicy

|

protected |

Allocation Policy: true if we always allocate on a hit, false otherwise.

Default is true.

Definition at line 126 of file tlb.hh.

Referenced by handleFuncTranslationReturn(), and handleTranslationReturn().

◆ assoc

◆ cleanupEvent

| EventFunctionWrapper gem5::VegaISA::GpuTLB::cleanupEvent |

Definition at line 320 of file tlb.hh.

Referenced by GpuTLB(), and handleTranslationReturn().

◆ cleanupQueue

| std::queue<Addr> gem5::VegaISA::GpuTLB::cleanupQueue |

Definition at line 314 of file tlb.hh.

Referenced by cleanup(), and handleTranslationReturn().

◆ cpuSidePort

| std::vector<CpuSidePort*> gem5::VegaISA::GpuTLB::cpuSidePort |

Definition at line 261 of file tlb.hh.

Referenced by cleanup(), getPort(), and handleTranslationReturn().

◆ entryList

|

protected |

An entryList per set is the equivalent of an LRU stack; it's used to guide replacement decisions.

The head of the list contains the MRU TLB entry of the given set. If the freeList for this set is empty, the last element of the list is evicted (i.e., dropped on the floor).

Definition at line 149 of file tlb.hh.

Referenced by demapPage(), insert(), invalidateAll(), lookup(), and lookupIt().

◆ FA

|

protected |

true if this is a fully-associative TLB

Definition at line 119 of file tlb.hh.

Referenced by lookupIt().

◆ freeList

|

protected |

Definition at line 140 of file tlb.hh.

Referenced by demapPage(), insert(), and invalidateAll().

◆ gpuDevice

|

protected |

Definition at line 110 of file tlb.hh.

Referenced by GpuTLB(), and translationReturn().

◆ hasMemSidePort

|

protected |

if true, then this is not the last level TLB

Definition at line 131 of file tlb.hh.

Referenced by getPort(), and translationReturn().

◆ hitLatency

| int gem5::VegaISA::GpuTLB::hitLatency |

Definition at line 153 of file tlb.hh.

Referenced by issueTLBLookup().

◆ maxCoalescedReqs

◆ memSidePort

| std::vector<MemSidePort*> gem5::VegaISA::GpuTLB::memSidePort |

Definition at line 263 of file tlb.hh.

Referenced by getPort(), and translationReturn().

◆ missLatency1

◆ missLatency2

| int gem5::VegaISA::GpuTLB::missLatency2 |

Definition at line 155 of file tlb.hh.

Referenced by translationReturn().

◆ numSets

|

protected |

Definition at line 114 of file tlb.hh.

Referenced by invalidateAll().

◆ outstandingReqs

| int gem5::VegaISA::GpuTLB::outstandingReqs |

◆ setMask

|

protected |

Definition at line 120 of file tlb.hh.

Referenced by demapPage(), insert(), lookup(), and lookupIt().

◆ size

|

protected |

◆ stats

| gem5::VegaISA::GpuTLB::VegaTLBStats gem5::VegaISA::GpuTLB::stats |

Referenced by GpuTLB(), handleTranslationReturn(), issueTLBLookup(), tlbLookup(), and translationReturn().

◆ tlb

|

protected |

◆ translationReturnEvent

Definition at line 310 of file tlb.hh.

Referenced by cleanup(), issueTLBLookup(), and translationReturn().

◆ walker

|

protected |

Definition at line 109 of file tlb.hh.

Referenced by getWalker(), GpuTLB(), and translationReturn().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:07:04 for gem5 by doxygen 1.14.0