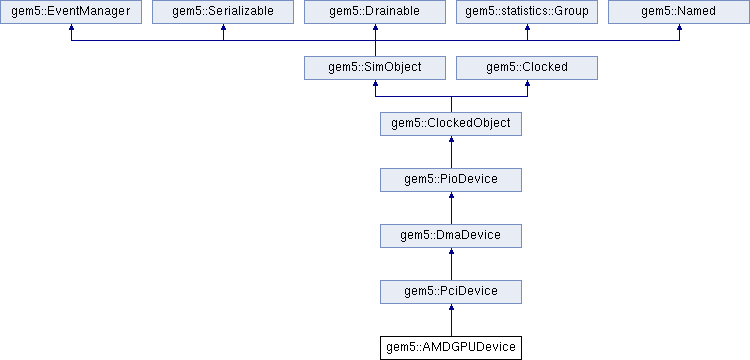

Device model for an AMD GPU. More...

#include <amdgpu_device.hh>

Classes | |

| struct | AddrRangeHasher |

Public Member Functions | |

| AMDGPUDevice (const AMDGPUDeviceParams &p) | |

| void | intrPost () |

| Methods inherited from PciEndpoint. | |

| Tick | writeConfig (PacketPtr pkt) override |

| Write to the PCI config space data that is stored locally. | |

| Tick | readConfig (PacketPtr pkt) override |

| Read from the PCI config space data that is stored locally. | |

| Tick | read (PacketPtr pkt) override |

| Pure virtual function that the device must implement. | |

| Tick | write (PacketPtr pkt) override |

| Pure virtual function that the device must implement. | |

| AddrRangeList | getAddrRanges () const override |

| Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to. | |

| void | serialize (CheckpointOut &cp) const override |

| Checkpoint support. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| AMDGPUInterruptHandler * | getIH () |

| Get handles to GPU blocks. | |

| SDMAEngine * | getSDMAById (int id) |

| SDMAEngine * | getSDMAEngine (Addr offset) |

| AMDGPUVM & | getVM () |

| AMDGPUMemoryManager * | getMemMgr () |

| GPUCommandProcessor * | CP () |

| void | setDoorbellType (uint32_t offset, QueueType qt, int ip_id=0) |

| Set handles to GPU blocks. | |

| void | unsetDoorbell (uint32_t offset) |

| void | processPendingDoorbells (uint32_t offset) |

| void | setSDMAEngine (Addr offset, SDMAEngine *eng) |

| uint32_t | getRegVal (uint64_t addr) |

| Register value getter/setter. | |

| void | setRegVal (uint64_t addr, uint32_t value) |

| RequestorID | vramRequestorId () |

| Methods related to translations and system/device memory. | |

| uint16_t | lastVMID () |

| uint16_t | allocateVMID (uint16_t pasid) |

| void | deallocateVmid (uint16_t vmid) |

| void | deallocatePasid (uint16_t pasid) |

| void | deallocateAllQueues (bool unmap_static) |

| void | mapDoorbellToVMID (Addr doorbell, uint16_t vmid) |

| uint16_t | getVMID (Addr doorbell) |

| std::unordered_map< uint16_t, std::set< int > > & | getUsedVMIDs () |

| void | insertQId (uint16_t vmid, int id) |

| GfxVersion | getGfxVersion () const |

| Public Member Functions inherited from gem5::PciEndpoint | |

| PciEndpoint (const PciEndpointParams ¶ms) | |

| Constructor for PCI Dev. | |

| Tick | writeConfig (PacketPtr pkt) override |

| Write to the PCI config space data that is stored locally. | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. | |

| Public Member Functions inherited from gem5::PciDevice | |

| Addr | pciToDma (Addr pci_addr) const |

| void | intrPost () |

| void | intrClear () |

| uint8_t | interruptLine () const |

| AddrRangeList | getAddrRanges () const override |

| Determine the address ranges that this device responds to. | |

| PciDevice (const PciDeviceParams ¶ms, std::initializer_list< PciBar * > BARs_init) | |

| Constructor for PCI Dev. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. | |

| const PciBusAddr & | busAddr () const |

| Public Member Functions inherited from gem5::DmaDevice | |

| DmaDevice (const Params &p) | |

| virtual | ~DmaDevice ()=default |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| bool | dmaPending () const |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Addr | cacheBlockSize () const |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::PioDevice | |

| PioDevice (const Params &p) | |

| virtual | ~PioDevice () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Private Types | |

| typedef void(SDMAEngine::* | sdmaFuncPtr) (uint32_t) |

Private Member Functions | |

| void | dispatchAccess (PacketPtr pkt, bool read) |

| Convert a PCI packet into a response. | |

| void | readFrame (PacketPtr pkt, Addr offset) |

| Helper methods to handle specific BAR read/writes. | |

| void | readDoorbell (PacketPtr pkt, Addr offset) |

| void | readMMIO (PacketPtr pkt, Addr offset) |

| void | writeFrame (PacketPtr pkt, Addr offset) |

| void | writeDoorbell (PacketPtr pkt, Addr offset) |

| void | writeMMIO (PacketPtr pkt, Addr offset) |

| bool | isROM (Addr addr) const |

| void | readROM (PacketPtr pkt) |

| void | writeROM (PacketPtr pkt) |

Private Attributes | |

| std::unordered_map< uint32_t, DoorbellInfo > | doorbells |

| Structures to hold registers, doorbells, and some frame memory. | |

| std::unordered_map< uint32_t, PacketPtr > | pendingDoorbellPkts |

| AddrRange | romRange |

| VGA ROM methods. | |

| std::array< uint8_t, ROM_SIZE > | rom |

| AMDMMIOReader | mmioReader |

| MMIO reader to populate device registers map. | |

| AMDGPUNbio | nbio |

| Blocks of the GPU. | |

| AMDGPUGfx | gfx |

| AMDGPUMemoryManager * | gpuMemMgr |

| AMDGPUInterruptHandler * | deviceIH |

| AMDGPUVM | gpuvm |

| GPUCommandProcessor * | cp |

| std::unordered_map< int, PM4PacketProcessor * > | pm4PktProcs |

| std::unordered_map< AddrRange, PM4PacketProcessor *, AddrRangeHasher > | pm4Ranges |

| std::unordered_map< uint32_t, SDMAEngine * > | sdmaEngs |

| std::unordered_map< uint32_t, SDMAEngine * > | sdmaIds |

| std::unordered_map< uint32_t, AddrRange > | sdmaMmios |

| std::unordered_map< uint32_t, sdmaFuncPtr > | sdmaFunc |

| bool | checkpoint_before_mmios |

| Initial checkpoint support variables. | |

| int | init_interrupt_count |

| std::unordered_map< uint16_t, uint16_t > | idMap |

| std::unordered_map< Addr, uint16_t > | doorbellVMIDMap |

| std::unordered_map< uint16_t, std::set< int > > | usedVMIDs |

| uint16_t | _lastVMID |

| memory::PhysicalMemory | deviceMem |

| GfxVersion | gfx_version = GfxVersion::gfx900 |

Additional Inherited Members | |

| Public Types inherited from gem5::DmaDevice | |

| typedef DmaDeviceParams | Params |

| Public Types inherited from gem5::PioDevice | |

| using | Params = PioDeviceParams |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| Protected Member Functions inherited from gem5::PciEndpoint | |

| PCIConfigType0 & | config () |

| Protected Member Functions inherited from gem5::PciDevice | |

| bool | getBAR (Addr addr, int &num, Addr &offs) |

| Which base address register (if any) maps the given address? | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

| Protected Attributes inherited from gem5::PciDevice | |

| const PciBusAddr | _busAddr |

| std::vector< MSIXTable > | msix_table |

| MSIX Table and PBA Structures. | |

| std::vector< MSIXPbaEntry > | msix_pba |

| std::vector< PciBar * > | BARs {} |

| PciHost::DeviceInterface | hostInterface |

| Tick | pioDelay |

| Tick | configDelay |

| const int | PMCAP_BASE |

| The capability list structures and base addresses. | |

| const int | PMCAP_ID_OFFSET |

| const int | PMCAP_PC_OFFSET |

| const int | PMCAP_PMCS_OFFSET |

| PMCAP | pmcap |

| const int | MSICAP_BASE |

| MSICAP | msicap |

| const int | MSIXCAP_BASE |

| const int | MSIXCAP_ID_OFFSET |

| const int | MSIXCAP_MXC_OFFSET |

| const int | MSIXCAP_MTAB_OFFSET |

| const int | MSIXCAP_MPBA_OFFSET |

| int | MSIX_TABLE_OFFSET |

| int | MSIX_TABLE_END |

| int | MSIX_PBA_OFFSET |

| int | MSIX_PBA_END |

| MSIXCAP | msixcap |

| const int | PXCAP_BASE |

| PXCAP | pxcap |

| Protected Attributes inherited from gem5::DmaDevice | |

| DmaPort | dmaPort |

| Protected Attributes inherited from gem5::PioDevice | |

| System * | sys |

| PioPort< PioDevice > | pioPort |

| The pioPort that handles the requests for us and provides us requests that it sees. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Detailed Description

Device model for an AMD GPU.

This models the interface between the PCI bus and the various IP blocks behind it. It translates requests to the various BARs and sends them to the appropriate IP block. BAR0 requests are VRAM requests that go to device memory, BAR2 are doorbells which are decoded and sent to the corresponding IP block. BAR5 is the MMIO interface which writes data values to registers controlling the IP blocks.

Definition at line 63 of file amdgpu_device.hh.

Member Typedef Documentation

◆ sdmaFuncPtr

|

private |

Definition at line 136 of file amdgpu_device.hh.

Constructor & Destructor Documentation

◆ AMDGPUDevice()

| gem5::AMDGPUDevice::AMDGPUDevice | ( | const AMDGPUDeviceParams & | p | ) |

Definition at line 55 of file amdgpu_device.cc.

References _lastVMID, AMDGPUDevice(), checkpoint_before_mmios, gem5::PciEndpoint::config(), cp, deviceIH, deviceMem, DPRINTF, gpuMemMgr, init_interrupt_count, gem5::ArmISA::m, name(), gem5::MipsISA::p, gem5::PciEndpoint::PciEndpoint(), gem5::RangeSize(), gem5::ROM_SIZE, romRange, gem5::ArmISA::s, sdmaMmios, and gem5::VGA_ROM_DEFAULT.

Referenced by AMDGPUDevice(), dispatchAccess(), getRegVal(), processPendingDoorbells(), readConfig(), readDoorbell(), readFrame(), readMMIO(), readROM(), setDoorbellType(), setRegVal(), write(), writeConfig(), writeDoorbell(), writeFrame(), writeMMIO(), and writeROM().

Member Function Documentation

◆ allocateVMID()

| uint16_t gem5::AMDGPUDevice::allocateVMID | ( | uint16_t | pasid | ) |

Definition at line 938 of file amdgpu_device.cc.

References _lastVMID, allocateVMID(), gem5::AMDGPU_VM_COUNT, idMap, panic, gem5::pasid, and usedVMIDs.

Referenced by allocateVMID().

◆ CP()

|

inline |

◆ deallocateAllQueues()

| void gem5::AMDGPUDevice::deallocateAllQueues | ( | bool | unmap_static | ) |

Definition at line 971 of file amdgpu_device.cc.

References deallocateAllQueues(), doorbells, doorbellVMIDMap, idMap, gem5::ArmISA::offset, sdmaEngs, and usedVMIDs.

Referenced by deallocateAllQueues().

◆ deallocatePasid()

| void gem5::AMDGPUDevice::deallocatePasid | ( | uint16_t | pasid | ) |

Definition at line 959 of file amdgpu_device.cc.

References deallocatePasid(), idMap, gem5::pasid, and usedVMIDs.

Referenced by deallocatePasid().

◆ deallocateVmid()

| void gem5::AMDGPUDevice::deallocateVmid | ( | uint16_t | vmid | ) |

Definition at line 953 of file amdgpu_device.cc.

References deallocateVmid(), and usedVMIDs.

Referenced by deallocateVmid().

◆ dispatchAccess()

|

private |

Convert a PCI packet into a response.

Definition at line 374 of file amdgpu_device.cc.

References AMDGPUDevice(), dispatchAccess(), DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getSize(), gem5::Packet::getUintX(), gem5::Packet::makeAtomicResponse(), and read().

Referenced by dispatchAccess(), read(), and write().

◆ getAddrRanges()

|

overridevirtual |

Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to.

- Returns

- a list of non-overlapping address ranges

Implements gem5::PioDevice.

Definition at line 263 of file amdgpu_device.cc.

References getAddrRanges(), gem5::PioDevice::getAddrRanges(), gem5::MipsISA::r, and romRange.

Referenced by getAddrRanges().

◆ getGfxVersion()

|

inline |

Definition at line 227 of file amdgpu_device.hh.

References gfx_version.

◆ getIH()

|

inline |

◆ getMemMgr()

|

inline |

Definition at line 192 of file amdgpu_device.hh.

References gpuMemMgr.

◆ getRegVal()

| uint32_t gem5::AMDGPUDevice::getRegVal | ( | uint64_t | addr | ) |

Register value getter/setter.

Used by other GPU blocks to change values from incoming driver/user packets.

Definition at line 706 of file amdgpu_device.cc.

References gem5::X86ISA::addr, AMDGPUDevice(), gem5::bits(), gem5::Packet::createRead(), gem5::Packet::dataStatic(), DPRINTF, gem5::Packet::getLE(), getRegVal(), readMMIO(), and vramRequestorId().

Referenced by getRegVal().

◆ getSDMAById()

| SDMAEngine * gem5::AMDGPUDevice::getSDMAById | ( | int | id | ) |

PM4 packets selected SDMAs using an integer ID. This method simply maps the integer ID to a pointer to the SDMA and checks for invalid IDs.

Definition at line 765 of file amdgpu_device.cc.

References getSDMAById(), gem5::ArmISA::id, and sdmaIds.

Referenced by getSDMAById(), and writeMMIO().

◆ getSDMAEngine()

| SDMAEngine * gem5::AMDGPUDevice::getSDMAEngine | ( | Addr | offset | ) |

Definition at line 777 of file amdgpu_device.cc.

References getSDMAEngine(), gem5::ArmISA::offset, and sdmaEngs.

Referenced by getSDMAEngine(), and writeDoorbell().

◆ getUsedVMIDs()

| std::unordered_map< uint16_t, std::set< int > > & gem5::AMDGPUDevice::getUsedVMIDs | ( | ) |

Definition at line 996 of file amdgpu_device.cc.

References getUsedVMIDs(), and usedVMIDs.

Referenced by getUsedVMIDs().

◆ getVM()

|

inline |

Definition at line 191 of file amdgpu_device.hh.

References gpuvm.

◆ getVMID()

|

inline |

Definition at line 222 of file amdgpu_device.hh.

References doorbellVMIDMap.

◆ insertQId()

| void gem5::AMDGPUDevice::insertQId | ( | uint16_t | vmid, |

| int | id ) |

Definition at line 1002 of file amdgpu_device.cc.

References insertQId(), and usedVMIDs.

Referenced by insertQId().

◆ intrPost()

| void gem5::AMDGPUDevice::intrPost | ( | ) |

Methods inherited from PciEndpoint.

Definition at line 783 of file amdgpu_device.cc.

References intrPost(), and gem5::PciDevice::intrPost().

Referenced by intrPost().

◆ isROM()

|

inlineprivate |

Definition at line 97 of file amdgpu_device.hh.

References gem5::X86ISA::addr, and romRange.

Referenced by read(), write(), and writeROM().

◆ lastVMID()

|

inline |

Definition at line 216 of file amdgpu_device.hh.

References _lastVMID.

◆ mapDoorbellToVMID()

| void gem5::AMDGPUDevice::mapDoorbellToVMID | ( | Addr | doorbell, |

| uint16_t | vmid ) |

Definition at line 990 of file amdgpu_device.cc.

References doorbellVMIDMap, and mapDoorbellToVMID().

Referenced by mapDoorbellToVMID().

◆ processPendingDoorbells()

| void gem5::AMDGPUDevice::processPendingDoorbells | ( | uint32_t | offset | ) |

Definition at line 695 of file amdgpu_device.cc.

References AMDGPUDevice(), DPRINTF, gem5::ArmISA::offset, pendingDoorbellPkts, processPendingDoorbells(), and writeDoorbell().

Referenced by processPendingDoorbells().

◆ read()

Pure virtual function that the device must implement.

Called when a read command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 625 of file amdgpu_device.cc.

References dispatchAccess(), gem5::DOORBELL_BAR, gem5::FRAMEBUFFER_BAR, gem5::Packet::getAddr(), gem5::PciDevice::getBAR(), isROM(), gem5::MMIO_BAR, gem5::ArmISA::offset, panic, gem5::PciDevice::pioDelay, read(), readDoorbell(), readFrame(), readMMIO(), and readROM().

Referenced by dispatchAccess(), and read().

◆ readConfig()

Read from the PCI config space data that is stored locally.

This may be overridden by the device but at some point it will eventually call this for normal operations that it does not need to override.

- Parameters

-

pkt packet containing the write the offset into config space

Reimplemented from gem5::PciDevice.

Definition at line 282 of file amdgpu_device.cc.

References gem5::PciDevice::_busAddr, AMDGPUDevice(), checkpoint_before_mmios, gem5::PciDevice::configDelay, gem5::curTick(), DPRINTF, gem5::exitSimLoop(), gem5::Packet::getAddr(), gem5::Packet::getLE(), gem5::Packet::getSize(), init_interrupt_count, gem5::Packet::makeAtomicResponse(), gem5::ArmISA::offset, panic, PCI_CONFIG_SIZE, PCI_DEVICE_SPECIFIC, PCI_INTERRUPT_PIN, gem5::PciDevice::pxcap, gem5::PciDevice::PXCAP_BASE, readConfig(), gem5::PciDevice::readConfig(), gem5::Packet::setLE(), and warn.

Referenced by readConfig().

◆ readDoorbell()

Definition at line 429 of file amdgpu_device.cc.

References AMDGPUDevice(), gem5::DOORBELL_BAR, DPRINTF, mmioReader, gem5::ArmISA::offset, and readDoorbell().

Referenced by read(), and readDoorbell().

◆ readFrame()

Helper methods to handle specific BAR read/writes.

Offset is the address of the packet - base address of the BAR.

read/writeFrame are used for BAR0 requests read/writeDoorbell are used for BAR2 requests read/writeMMIO are used for BAR5 requests

Definition at line 384 of file amdgpu_device.cc.

References AMDGPUDevice(), gem5::Packet::cmd, cp, gem5::Packet::createRead(), gem5::Packet::dataDynamic(), DPRINTF, gem5::MemCmd::FunctionalReadError, gem5::Packet::getSize(), gem5::Packet::getUintX(), nbio, gem5::ArmISA::offset, readFrame(), gem5::MemCmd::ReadReq, gem5::Packet::req, gem5::Packet::setSuppressFuncError(), gem5::Packet::setUintX(), gem5::X86ISA::system, and vramRequestorId().

Referenced by read(), and readFrame().

◆ readMMIO()

Definition at line 436 of file amdgpu_device.cc.

References AMDGPUDevice(), DPRINTF, gfx, gem5::GFX_MMIO_RANGE, gpuvm, gem5::GRBM_MMIO_RANGE, gem5::GRBM_OFFSET_SHIFT, gem5::MMHUB_MMIO_RANGE, gem5::MMHUB_OFFSET_SHIFT, gem5::MMIO_BAR, mmioReader, nbio, gem5::NBIO_MMIO_RANGE, gem5::ArmISA::offset, readMMIO(), and gem5::AddrRange::start().

Referenced by getRegVal(), read(), and readMMIO().

◆ readROM()

|

private |

Definition at line 236 of file amdgpu_device.cc.

References AMDGPUDevice(), DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getSize(), readROM(), rom, gem5::ROM_SIZE, and gem5::Packet::setUintX().

◆ serialize()

|

overridevirtual |

Checkpoint support.

Implements gem5::Serializable.

Definition at line 789 of file amdgpu_device.cc.

References cp, deviceMem, doorbells, gpuvm, sdmaEngs, serialize(), gem5::PciDevice::serialize(), SERIALIZE_SCALAR, SERIALIZE_UNIQUE_PTR_ARRAY, and usedVMIDs.

Referenced by serialize().

◆ setDoorbellType()

| void gem5::AMDGPUDevice::setDoorbellType | ( | uint32_t | offset, |

| QueueType | qt, | ||

| int | ip_id = 0 ) |

Set handles to GPU blocks.

Definition at line 745 of file amdgpu_device.cc.

References AMDGPUDevice(), doorbells, DPRINTF, gem5::ArmISA::offset, and setDoorbellType().

Referenced by setDoorbellType().

◆ setRegVal()

| void gem5::AMDGPUDevice::setRegVal | ( | uint64_t | addr, |

| uint32_t | value ) |

Definition at line 730 of file amdgpu_device.cc.

References gem5::X86ISA::addr, AMDGPUDevice(), gem5::Packet::createWrite(), gem5::Packet::dataStatic(), DPRINTF, setRegVal(), vramRequestorId(), and writeMMIO().

Referenced by setRegVal().

◆ setSDMAEngine()

| void gem5::AMDGPUDevice::setSDMAEngine | ( | Addr | offset, |

| SDMAEngine * | eng ) |

Definition at line 759 of file amdgpu_device.cc.

References gem5::ArmISA::offset, sdmaEngs, and setSDMAEngine().

Referenced by setSDMAEngine().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 862 of file amdgpu_device.cc.

References cp, deviceMem, doorbells, gpuvm, sdmaEngs, sdmaIds, unserialize(), gem5::PciEndpoint::unserialize(), UNSERIALIZE_SCALAR, UNSERIALIZE_UNIQUE_PTR_ARRAY, and usedVMIDs.

Referenced by unserialize().

◆ unsetDoorbell()

| void gem5::AMDGPUDevice::unsetDoorbell | ( | uint32_t | offset | ) |

Definition at line 753 of file amdgpu_device.cc.

References doorbells, gem5::ArmISA::offset, and unsetDoorbell().

Referenced by unsetDoorbell().

◆ vramRequestorId()

|

inline |

Methods related to translations and system/device memory.

Definition at line 213 of file amdgpu_device.hh.

References gpuMemMgr.

Referenced by getRegVal(), readFrame(), setRegVal(), and writeFrame().

◆ write()

Pure virtual function that the device must implement.

Called when a write command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 654 of file amdgpu_device.cc.

References AMDGPUDevice(), data, dispatchAccess(), gem5::DOORBELL_BAR, DPRINTF, gem5::FRAMEBUFFER_BAR, gem5::Packet::getAddr(), gem5::PciDevice::getBAR(), gem5::Packet::getUintX(), isROM(), gem5::MMIO_BAR, gem5::ArmISA::offset, panic, gem5::PciDevice::pioDelay, write(), writeDoorbell(), writeFrame(), writeMMIO(), and writeROM().

Referenced by write().

◆ writeConfig()

Write to the PCI config space data that is stored locally.

This may be overridden by the device but at some point it will eventually call this for normal operations that it does not need to override.

- Parameters

-

pkt packet containing the write the offset into config space

Reimplemented from gem5::PciDevice.

Definition at line 346 of file amdgpu_device.cc.

References AMDGPUDevice(), gem5::PciDevice::configDelay, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getConstPtr(), gem5::Packet::getSize(), gem5::Packet::getUintX(), gem5::Packet::makeAtomicResponse(), gem5::ArmISA::offset, PCI_CONFIG_SIZE, PCI_DEVICE_SPECIFIC, gem5::PciDevice::pxcap, gem5::PciDevice::PXCAP_BASE, writeConfig(), and gem5::PciEndpoint::writeConfig().

Referenced by writeConfig().

◆ writeDoorbell()

Definition at line 505 of file amdgpu_device.cc.

References AMDGPUDevice(), gem5::Compute, gem5::ComputeAQL, cp, gem5::Packet::createWrite(), gem5::Packet::dataDynamic(), deviceIH, doorbells, DPRINTF, gem5::Packet::getLE(), gem5::Packet::getPtr(), getSDMAEngine(), gem5::Packet::getSize(), gem5::Gfx, gem5::InterruptHandler, gem5::ArmISA::offset, panic, pendingDoorbellPkts, pm4PktProcs, gem5::SDMAEngine::processGfx(), gem5::SDMAEngine::processPage(), gem5::SDMAEngine::processRLC(), gem5::Packet::req, gem5::RLC, gem5::SDMAGfx, gem5::SDMAPage, warn, and writeDoorbell().

Referenced by processPendingDoorbells(), write(), and writeDoorbell().

◆ writeFrame()

Definition at line 464 of file amdgpu_device.cc.

References AMDGPUDevice(), CP(), cp, gem5::Packet::createWrite(), gem5::Packet::dataDynamic(), DPRINTF, gem5::Packet::getPtr(), gem5::Packet::getSize(), gem5::Packet::getUintX(), gpuMemMgr, gpuvm, nbio, gem5::ArmISA::offset, gem5::X86ISA::system, vramRequestorId(), and writeFrame().

Referenced by write(), and writeFrame().

◆ writeMMIO()

Definition at line 571 of file amdgpu_device.cc.

References AMDGPUDevice(), deviceIH, DPRINTF, gem5::Packet::getLE(), getSDMAById(), gfx, gem5::GFX_MMIO_RANGE, gpuvm, gem5::GRBM_MMIO_RANGE, gem5::GRBM_OFFSET_SHIFT, gem5::IH_MMIO_RANGE, gem5::IH_OFFSET_SHIFT, nbio, gem5::NBIO_MMIO_RANGE, gem5::ArmISA::offset, pm4Ranges, sdmaFunc, sdmaIds, sdmaMmios, gem5::AddrRange::start(), and writeMMIO().

Referenced by setRegVal(), write(), and writeMMIO().

◆ writeROM()

|

private |

Definition at line 249 of file amdgpu_device.cc.

References AMDGPUDevice(), DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getSize(), gem5::Packet::getUintX(), isROM(), rom, romRange, and writeROM().

Referenced by write(), and writeROM().

Member Data Documentation

◆ _lastVMID

|

private |

Definition at line 153 of file amdgpu_device.hh.

Referenced by allocateVMID(), AMDGPUDevice(), and lastVMID().

◆ checkpoint_before_mmios

|

private |

Initial checkpoint support variables.

Definition at line 142 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), and readConfig().

◆ cp

|

private |

Definition at line 116 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), CP(), readFrame(), serialize(), unserialize(), writeDoorbell(), and writeFrame().

◆ deviceIH

|

private |

Definition at line 114 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), getIH(), writeDoorbell(), and writeMMIO().

◆ deviceMem

|

private |

Definition at line 158 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), serialize(), and unserialize().

◆ doorbells

|

private |

Structures to hold registers, doorbells, and some frame memory.

Definition at line 90 of file amdgpu_device.hh.

Referenced by deallocateAllQueues(), serialize(), setDoorbellType(), unserialize(), unsetDoorbell(), and writeDoorbell().

◆ doorbellVMIDMap

|

private |

Definition at line 149 of file amdgpu_device.hh.

Referenced by deallocateAllQueues(), getVMID(), and mapDoorbellToVMID().

◆ gfx

|

private |

Definition at line 112 of file amdgpu_device.hh.

Referenced by readMMIO(), and writeMMIO().

◆ gfx_version

|

private |

Definition at line 161 of file amdgpu_device.hh.

Referenced by getGfxVersion().

◆ gpuMemMgr

|

private |

Definition at line 113 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), getMemMgr(), vramRequestorId(), and writeFrame().

◆ gpuvm

|

private |

Definition at line 115 of file amdgpu_device.hh.

Referenced by getVM(), readMMIO(), serialize(), unserialize(), writeFrame(), and writeMMIO().

◆ idMap

|

private |

Definition at line 147 of file amdgpu_device.hh.

Referenced by allocateVMID(), deallocateAllQueues(), and deallocatePasid().

◆ init_interrupt_count

|

private |

Definition at line 143 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), and readConfig().

◆ mmioReader

|

private |

MMIO reader to populate device registers map.

Definition at line 106 of file amdgpu_device.hh.

Referenced by readDoorbell(), and readMMIO().

◆ nbio

|

private |

Blocks of the GPU.

Definition at line 111 of file amdgpu_device.hh.

Referenced by readFrame(), readMMIO(), writeFrame(), and writeMMIO().

◆ pendingDoorbellPkts

|

private |

Definition at line 91 of file amdgpu_device.hh.

Referenced by processPendingDoorbells(), and writeDoorbell().

◆ pm4PktProcs

|

private |

Definition at line 125 of file amdgpu_device.hh.

Referenced by writeDoorbell().

◆ pm4Ranges

|

private |

Definition at line 127 of file amdgpu_device.hh.

Referenced by writeMMIO().

◆ rom

|

private |

Definition at line 101 of file amdgpu_device.hh.

Referenced by readROM(), and writeROM().

◆ romRange

|

private |

VGA ROM methods.

Definition at line 96 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), getAddrRanges(), isROM(), and writeROM().

◆ sdmaEngs

|

private |

Definition at line 130 of file amdgpu_device.hh.

Referenced by deallocateAllQueues(), getSDMAEngine(), serialize(), setSDMAEngine(), and unserialize().

◆ sdmaFunc

|

private |

Definition at line 137 of file amdgpu_device.hh.

Referenced by writeMMIO().

◆ sdmaIds

|

private |

Definition at line 132 of file amdgpu_device.hh.

Referenced by getSDMAById(), unserialize(), and writeMMIO().

◆ sdmaMmios

|

private |

Definition at line 134 of file amdgpu_device.hh.

Referenced by AMDGPUDevice(), and writeMMIO().

◆ usedVMIDs

|

private |

Definition at line 151 of file amdgpu_device.hh.

Referenced by allocateVMID(), deallocateAllQueues(), deallocatePasid(), deallocateVmid(), getUsedVMIDs(), insertQId(), serialize(), and unserialize().

The documentation for this class was generated from the following files:

- dev/amdgpu/amdgpu_device.hh

- dev/amdgpu/amdgpu_device.cc

Generated on Sat Oct 18 2025 08:06:49 for gem5 by doxygen 1.14.0