#include <faults.hh>

Public Member Functions | |

| AbortFault (Addr _faultAddr, bool _write, DomainType _domain, uint8_t _source, bool _stage2, TranMethod _tranMethod=TranMethod::UnknownTran, ArmFault::DebugType _debug=ArmFault::NODEBUG) | |

| bool | getFaultVAddr (Addr &va) const override |

| void | invoke (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) override |

| void | update (ThreadContext *tc) override |

| FSR | getFsr (ThreadContext *tc) const override |

| uint8_t | getFaultStatusCode (ThreadContext *tc) const |

| bool | abortDisable (ThreadContext *tc) override |

| bool | isStage2 () const override |

| void | annotate (ArmFault::AnnotationIDs id, uint64_t val) override |

| void | setSyndrome (ThreadContext *tc, MiscRegIndex syndrome_reg) override |

| bool | isMMUFault () const |

| bool | isExternalAbort () const override |

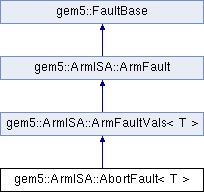

| Public Member Functions inherited from gem5::ArmISA::ArmFaultVals< T > | |

| ArmFaultVals (ExtMachInst mach_inst=0, uint32_t _iss=0) | |

| FaultName | name () const override |

| FaultOffset | offset (ThreadContext *tc) override |

| FaultOffset | offset64 (ThreadContext *tc) override |

| OperatingMode | nextMode () override |

| virtual bool | routeToMonitor (ThreadContext *tc) const override |

| uint8_t | armPcOffset (bool is_hyp) override |

| uint8_t | thumbPcOffset (bool is_hyp) override |

| uint8_t | armPcElrOffset () override |

| uint8_t | thumbPcElrOffset () override |

| bool | abortDisable (ThreadContext *tc) override |

| bool | fiqDisable (ThreadContext *tc) override |

| ExceptionClass | ec (ThreadContext *tc) const override |

| Syndrome methods. | |

| bool | il (ThreadContext *tc) const override |

| uint32_t | iss () const override |

| Public Member Functions inherited from gem5::ArmISA::ArmFault | |

| ArmFault (ExtMachInst mach_inst=0, uint32_t _iss=0) | |

| MiscRegIndex | getSyndromeReg64 () const |

| void | invoke (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) override |

| void | invoke32 (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

| void | invoke64 (ThreadContext *tc, const StaticInstPtr &inst=nullStaticInstPtr) |

| bool | isResetSPSR () |

| bool | vectorCatch (ThreadContext *tc, const StaticInstPtr &inst) |

| ArmStaticInst * | instrAnnotate (const StaticInstPtr &inst) |

| virtual bool | routeToHyp (ThreadContext *tc) const |

| virtual uint32_t | vectorCatchFlag () const |

| OperatingMode | getToMode () const |

| Public Member Functions inherited from gem5::FaultBase | |

| virtual | ~FaultBase () |

Protected Attributes | |

| Addr | faultAddr |

| The virtual address the fault occured at. | |

| Addr | OVAddr |

| Original virtual address. | |

| bool | write |

| DomainType | domain |

| uint8_t | source |

| uint8_t | srcEncoded |

| bool | stage2 |

| bool | s1ptw |

| TranMethod | tranMethod |

| ArmFault::DebugType | debugType |

| Protected Attributes inherited from gem5::ArmISA::ArmFault | |

| ExtMachInst | machInst |

| uint32_t | issRaw |

| bool | bStep |

| bool | from64 |

| bool | to64 |

| ExceptionLevel | fromEL |

| ExceptionLevel | toEL |

| OperatingMode | fromMode |

| OperatingMode | toMode |

| bool | faultUpdated |

| bool | hypRouted |

| bool | span |

Detailed Description

Constructor & Destructor Documentation

◆ AbortFault()

|

inline |

Definition at line 487 of file faults.hh.

References debugType, domain, faultAddr, gem5::ArmISA::ArmFault::NODEBUG, OVAddr, s1ptw, source, srcEncoded, stage2, tranMethod, gem5::ArmISA::UnknownTran, and write.

Member Function Documentation

◆ abortDisable()

|

overridevirtual |

Implements gem5::ArmISA::ArmFault.

Definition at line 1184 of file faults.cc.

References gem5::ArmISA::EL3, gem5::ArmSystem::haveEL(), gem5::ArmISA::MISCREG_SCR_EL3, and gem5::ThreadContext::readMiscRegNoEffect().

◆ annotate()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Reimplemented in gem5::ArmISA::DataAbort.

Definition at line 1195 of file faults.cc.

References gem5::ArmISA::ArmFault::OVA, OVAddr, gem5::ArmISA::ArmFault::S1PTW, s1ptw, and gem5::X86ISA::val.

Referenced by gem5::ArmISA::DataAbort::annotate().

◆ getFaultStatusCode()

| uint8_t gem5::ArmISA::AbortFault< T >::getFaultStatusCode | ( | ThreadContext * | tc | ) | const |

Definition at line 1133 of file faults.cc.

References gem5::ArmISA::ArmFault::aarch64FaultSources, gem5::ArmISA::ArmFault::faultUpdated, gem5::ArmISA::ArmFault::longDescFaultSources, gem5::ArmISA::LpaeTran, panic_if, gem5::ArmISA::ArmFault::shortDescFaultSources, source, gem5::ArmISA::ArmFault::to64, tranMethod, and gem5::ArmISA::UnknownTran.

Referenced by getFsr(), and setSyndrome().

◆ getFaultVAddr()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Definition at line 1242 of file faults.cc.

References faultAddr, OVAddr, stage2, and gem5::ArmISA::va.

◆ getFsr()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Definition at line 1159 of file faults.cc.

References gem5::bits(), domain, getFaultStatusCode(), gem5::ArmISA::LpaeTran, tranMethod, gem5::ArmISA::UnknownTran, and write.

Referenced by invoke().

◆ invoke()

|

overridevirtual |

Reimplemented from gem5::FaultBase.

Reimplemented in gem5::ArmISA::VirtualDataAbort.

Definition at line 1033 of file faults.cc.

References gem5::ArmISA::ArmFault::AsynchronousExternalAbort, gem5::bits(), gem5::ArmISA::ArmFault::BRKPOINT, gem5::BaseCPU::clearInterrupt(), debugType, DPRINTF, faultAddr, gem5::ThreadContext::getCpuPtr(), getFsr(), gem5::ArmISA::INT_ABT, gem5::ArmISA::ArmFault::invoke(), gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_DBGDSCRext, gem5::ArmISA::MISCREG_HPFAR, gem5::ArmISA::MISCREG_HPFAR_EL2, gem5::ArmISA::MODE_HYP, gem5::ArmISA::ArmFault::NODEBUG, OVAddr, gem5::ThreadContext::readMiscReg(), gem5::ThreadContext::setMiscReg(), source, stage2, gem5::ThreadContext::threadId(), gem5::ArmISA::ArmFault::to64, gem5::ArmISA::ArmFault::toEL, gem5::ArmISA::ArmFault::VECTORCATCH, gem5::ArmISA::ArmFault::WPOINT_CM, and gem5::ArmISA::misc_regs::writeRegister().

Referenced by gem5::ArmISA::VirtualDataAbort::invoke().

◆ isExternalAbort()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Definition at line 1231 of file faults.cc.

References gem5::ArmISA::ArmFault::AsynchronousExternalAbort, source, gem5::ArmISA::ArmFault::SynchExtAbtOnTranslTableWalkLL, and gem5::ArmISA::ArmFault::SynchronousExternalAbort.

◆ isMMUFault()

| bool gem5::ArmISA::AbortFault< T >::isMMUFault | ( | ) | const |

Definition at line 1214 of file faults.cc.

References gem5::ArmISA::ArmFault::AccessFlagLL, gem5::ArmISA::ArmFault::AlignmentFault, gem5::ArmISA::ArmFault::DomainLL, gem5::ArmISA::ArmFault::PermissionLL, source, and gem5::ArmISA::ArmFault::TranslationLL.

◆ isStage2()

|

inlineoverridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Definition at line 506 of file faults.hh.

References stage2.

◆ setSyndrome()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Definition at line 1122 of file faults.cc.

References gem5::ArmISA::ArmFault::FaultSourceInvalid, getFaultStatusCode(), panic, gem5::ArmISA::ArmFault::setSyndrome(), and srcEncoded.

◆ update()

|

overridevirtual |

Reimplemented from gem5::ArmISA::ArmFault.

Definition at line 1094 of file faults.cc.

References DPRINTF, gem5::ArmISA::longDescFormatInUse(), gem5::ArmISA::LpaeTran, gem5::ArmISA::MISCREG_TTBCR_S, gem5::ThreadContext::readMiscReg(), gem5::ArmISA::ArmFaultVals< T >::routeToMonitor(), tranMethod, gem5::ArmISA::UnknownTran, gem5::ArmISA::ArmFault::update(), and gem5::ArmISA::VmsaTran.

Member Data Documentation

◆ debugType

|

protected |

Definition at line 484 of file faults.hh.

Referenced by AbortFault(), and invoke().

◆ domain

|

protected |

Definition at line 478 of file faults.hh.

Referenced by AbortFault(), and getFsr().

◆ faultAddr

|

protected |

The virtual address the fault occured at.

If 2 stages of translation are being used then this is the intermediate physical address that is the starting point for the second stage of translation.

Definition at line 470 of file faults.hh.

Referenced by AbortFault(), getFaultVAddr(), and invoke().

◆ OVAddr

|

protected |

Original virtual address.

If the fault was generated on the second stage of translation then this variable stores the virtual address used in the original stage 1 translation.

Definition at line 476 of file faults.hh.

Referenced by AbortFault(), annotate(), getFaultVAddr(), and invoke().

◆ s1ptw

|

protected |

Definition at line 482 of file faults.hh.

Referenced by AbortFault(), and annotate().

◆ source

|

protected |

Definition at line 479 of file faults.hh.

Referenced by AbortFault(), getFaultStatusCode(), invoke(), isExternalAbort(), and isMMUFault().

◆ srcEncoded

|

protected |

Definition at line 480 of file faults.hh.

Referenced by AbortFault(), and setSyndrome().

◆ stage2

|

protected |

Definition at line 481 of file faults.hh.

Referenced by AbortFault(), getFaultVAddr(), invoke(), and isStage2().

◆ tranMethod

|

protected |

Definition at line 483 of file faults.hh.

Referenced by AbortFault(), getFaultStatusCode(), getFsr(), and update().

◆ write

|

protected |

Definition at line 477 of file faults.hh.

Referenced by AbortFault(), and getFsr().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:56 for gem5 by doxygen 1.14.0