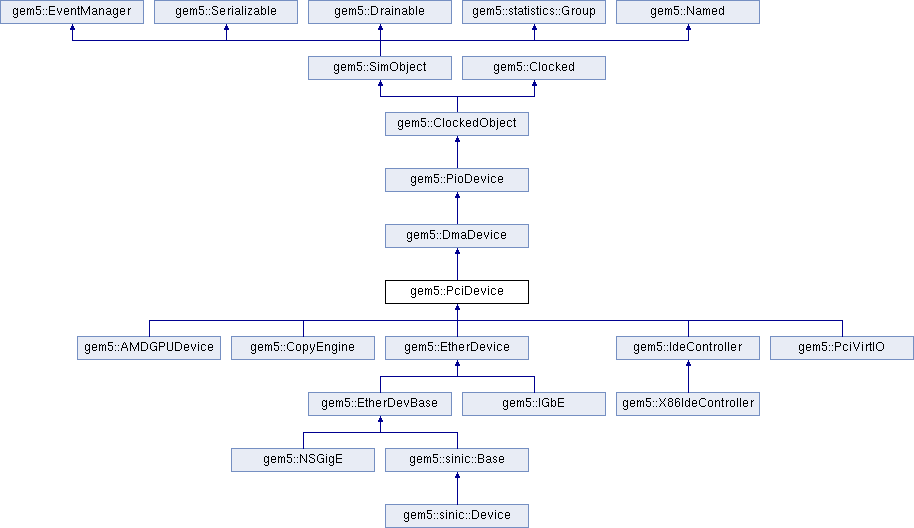

PCI device, base implementation is only config space. More...

#include <device.hh>

Public Member Functions | |

| virtual Tick | writeConfig (PacketPtr pkt) |

| Write to the PCI config space data that is stored locally. | |

| virtual Tick | readConfig (PacketPtr pkt) |

| Read from the PCI config space data that is stored locally. | |

| Addr | pciToDma (Addr pci_addr) const |

| void | intrPost () |

| void | intrClear () |

| uint8_t | interruptLine () const |

| AddrRangeList | getAddrRanges () const override |

| Determine the address ranges that this device responds to. | |

| PciDevice (const PciDeviceParams ¶ms, std::initializer_list< PciBar * > BARs_init) | |

| Constructor for PCI Dev. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. | |

| const PciBusAddr & | busAddr () const |

| Public Member Functions inherited from gem5::DmaDevice | |

| DmaDevice (const Params &p) | |

| virtual | ~DmaDevice ()=default |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| bool | dmaPending () const |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Addr | cacheBlockSize () const |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::PioDevice | |

| PioDevice (const Params &p) | |

| virtual | ~PioDevice () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| bool | getBAR (Addr addr, int &num, Addr &offs) |

| Which base address register (if any) maps the given address? | |

| Protected Member Functions inherited from gem5::PioDevice | |

| virtual Tick | read (PacketPtr pkt)=0 |

| Pure virtual function that the device must implement. | |

| virtual Tick | write (PacketPtr pkt)=0 |

| Pure virtual function that the device must implement. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| const PciBusAddr | _busAddr |

| std::vector< MSIXTable > | msix_table |

| MSIX Table and PBA Structures. | |

| std::vector< MSIXPbaEntry > | msix_pba |

| std::vector< PciBar * > | BARs {} |

| PciHost::DeviceInterface | hostInterface |

| Tick | pioDelay |

| Tick | configDelay |

| const int | PMCAP_BASE |

| The capability list structures and base addresses. | |

| const int | PMCAP_ID_OFFSET |

| const int | PMCAP_PC_OFFSET |

| const int | PMCAP_PMCS_OFFSET |

| PMCAP | pmcap |

| const int | MSICAP_BASE |

| MSICAP | msicap |

| const int | MSIXCAP_BASE |

| const int | MSIXCAP_ID_OFFSET |

| const int | MSIXCAP_MXC_OFFSET |

| const int | MSIXCAP_MTAB_OFFSET |

| const int | MSIXCAP_MPBA_OFFSET |

| int | MSIX_TABLE_OFFSET |

| int | MSIX_TABLE_END |

| int | MSIX_PBA_OFFSET |

| int | MSIX_PBA_END |

| MSIXCAP | msixcap |

| const int | PXCAP_BASE |

| PXCAP | pxcap |

| Protected Attributes inherited from gem5::DmaDevice | |

| DmaPort | dmaPort |

| Protected Attributes inherited from gem5::PioDevice | |

| System * | sys |

| PioPort< PioDevice > | pioPort |

| The pioPort that handles the requests for us and provides us requests that it sees. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Private Member Functions | |

| bool | isCommonConfig (Addr offs) |

Private Attributes | |

| friend | PciEndpoint |

| friend | PciBridge |

| PCIConfig | _config |

| The current config space. | |

Additional Inherited Members | |

| Public Types inherited from gem5::DmaDevice | |

| typedef DmaDeviceParams | Params |

| Public Types inherited from gem5::PioDevice | |

| using | Params = PioDeviceParams |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Detailed Description

Constructor & Destructor Documentation

◆ PciDevice()

| gem5::PciDevice::PciDevice | ( | const PciDeviceParams & | params, |

| std::initializer_list< PciBar * > | BARs_init ) |

Constructor for PCI Dev.

This function copies data from the config file object PCIConfigData and registers the device with a PciHost object.

Definition at line 67 of file device.cc.

References _busAddr, _config, BARs, configDelay, gem5::DmaDevice::DmaDevice(), fatal_if, hostInterface, gem5::htole(), msicap, MSICAP_BASE, msix_pba, MSIX_PBA_END, MSIX_PBA_OFFSET, msix_table, MSIX_TABLE_END, MSIX_TABLE_OFFSET, msixcap, MSIXCAP_BASE, MSIXCAP_ID, MSIXCAP_ID_OFFSET, MSIXCAP_MPBA, MSIXCAP_MPBA_OFFSET, MSIXCAP_MTAB, MSIXCAP_MTAB_OFFSET, MSIXCAP_MXC, MSIXCAP_MXC_OFFSET, MSIXVECS_PER_PBA, gem5::MipsISA::p, pioDelay, pmcap, PMCAP_BASE, PMCAP_ID, PMCAP_ID_OFFSET, PMCAP_PC, PMCAP_PC_OFFSET, PMCAP_PMCS, PMCAP_PMCS_OFFSET, pxcap, and PXCAP_BASE.

Referenced by gem5::PciBridge::PciBridge(), gem5::PciEndpoint::PciEndpoint(), readConfig(), and writeConfig().

Member Function Documentation

◆ busAddr()

|

inline |

◆ getAddrRanges()

|

overridevirtual |

Determine the address ranges that this device responds to.

- Returns

- a list of non-overlapping address ranges

Implements gem5::PioDevice.

Definition at line 267 of file device.cc.

References _config, BARs, and gem5::letoh().

◆ getBAR()

Which base address register (if any) maps the given address?

- Parameters

-

addr The address to check.

- Return values

-

num The BAR number (0-5 inclusive), only valid if return value is true. offs The offset from the base address, only valid if return value is true.

- Returns

- True iff address maps to a base address register's region.

Definition at line 336 of file device.hh.

References gem5::X86ISA::addr, BARs, and gem5::ArmISA::i.

Referenced by gem5::IdeController::dispatchAccess(), gem5::AMDGPUDevice::read(), gem5::CopyEngine::read(), gem5::IGbE::read(), gem5::PciVirtIO::read(), gem5::AMDGPUDevice::write(), gem5::CopyEngine::write(), gem5::IGbE::write(), and gem5::PciVirtIO::write().

◆ interruptLine()

|

inline |

Definition at line 384 of file device.hh.

References _config, and gem5::letoh().

Referenced by gem5::GenericPciHost::mapPciInterrupt().

◆ intrClear()

|

inline |

Definition at line 381 of file device.hh.

References hostInterface.

Referenced by gem5::IdeController::clearInterrupt(), gem5::IGbE::cpuClearInt(), gem5::NSGigE::cpuIntrClear(), gem5::sinic::Base::cpuIntrClear(), and gem5::PciVirtIO::read().

◆ intrPost()

|

inline |

Definition at line 380 of file device.hh.

References hostInterface.

Referenced by gem5::NSGigE::cpuInterrupt(), gem5::sinic::Base::cpuInterrupt(), gem5::IGbE::cpuPostInt(), gem5::AMDGPUDevice::intrPost(), gem5::PciVirtIO::kick(), and gem5::IdeController::postInterrupt().

◆ isCommonConfig()

|

inlineprivate |

Definition at line 284 of file device.hh.

References PCI_BIST, PCI_CAP_PTR, PCI_INTERRUPT_LINE, and PCI_INTERRUPT_PIN.

Referenced by gem5::PciBridge::writeConfig(), writeConfig(), and gem5::PciEndpoint::writeConfig().

◆ pciToDma()

Definition at line 375 of file device.hh.

References hostInterface.

Referenced by gem5::IGbE::TxDescCache::actionAfterWb(), gem5::IGbE::DescCache< T >::fetchDescriptors1(), gem5::IGbE::TxDescCache::getPacketData(), gem5::IGbE::TxDescCache::processContextDesc(), gem5::sinic::Device::rxKick(), gem5::sinic::Device::txKick(), gem5::IGbE::DescCache< T >::writeback1(), and gem5::IGbE::RxDescCache::writePacket().

◆ readConfig()

Read from the PCI config space data that is stored locally.

This may be overridden by the device but at some point it will eventually call this for normal operations that it does not need to override.

- Parameters

-

pkt packet containing the write the offset into config space

Reimplemented in gem5::AMDGPUDevice, and gem5::IdeController.

Definition at line 210 of file device.cc.

References _busAddr, _config, configDelay, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getLE(), gem5::Packet::getSize(), gem5::Packet::makeAtomicResponse(), name(), gem5::ArmISA::offset, panic, PCI_CONFIG_SIZE, PCI_DEVICE_SPECIFIC, PciDevice(), gem5::Packet::setLE(), and warn_once.

Referenced by gem5::GenericPciHost::read(), gem5::NSGigE::read(), gem5::AMDGPUDevice::readConfig(), and gem5::IdeController::readConfig().

◆ serialize()

|

overridevirtual |

Serialize this object to the given output stream.

- Parameters

-

os The stream to serialize to.

Reimplemented from gem5::ClockedObject.

Definition at line 386 of file device.cc.

References _config, gem5::bits(), gem5::csprintf(), gem5::ArmISA::i, msicap, msix_pba, msix_table, msixcap, MSIXCAP_BASE, MSIXVECS_PER_PBA, gem5::paramOut(), pmcap, pxcap, SERIALIZE_ARRAY, and SERIALIZE_SCALAR.

Referenced by gem5::AMDGPUDevice::serialize(), gem5::CopyEngine::serialize(), gem5::IdeController::serialize(), gem5::IGbE::serialize(), gem5::NSGigE::serialize(), and gem5::sinic::Base::serialize().

◆ unserialize()

|

overridevirtual |

Reconstruct the state of this object from a checkpoint.

- Parameters

-

cp The checkpoint use. section The section name of this object

Reimplemented from gem5::ClockedObject.

Reimplemented in gem5::PciEndpoint.

Definition at line 463 of file device.cc.

References _config, gem5::bits(), gem5::csprintf(), gem5::ArmISA::i, msicap, msix_pba, msix_table, msixcap, MSIXCAP_BASE, gem5::paramIn(), pmcap, pxcap, UNSERIALIZE_ARRAY, and UNSERIALIZE_SCALAR.

Referenced by gem5::PciBridge::unserialize(), and gem5::PciEndpoint::unserialize().

◆ writeConfig()

Write to the PCI config space data that is stored locally.

This may be overridden by the device but at some point it will eventually call this for normal operations that it does not need to override.

- Parameters

-

pkt packet containing the write the offset into config space

Reimplemented in gem5::AMDGPUDevice, gem5::IdeController, gem5::IGbE, gem5::NSGigE, gem5::PciBridge, and gem5::PciEndpoint.

Definition at line 281 of file device.cc.

References _busAddr, _config, configDelay, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getLE(), gem5::Packet::getSize(), isCommonConfig(), gem5::Packet::makeAtomicResponse(), name(), gem5::ArmISA::offset, panic, PCI_CACHE_LINE_SIZE, PCI_CLASS_CODE, PCI_COMMAND, PCI_CONFIG_SIZE, PCI_DEVICE_SPECIFIC, PCI_INTERRUPT_LINE, PCI_INTERRUPT_PIN, PCI_LATENCY_TIMER, PCI_REVISION_ID, PCI_STATUS, PciDevice(), gem5::PioDevice::pioPort, and warn_once.

Referenced by gem5::GenericPciHost::write(), gem5::PciBridge::writeConfig(), and gem5::PciEndpoint::writeConfig().

Member Data Documentation

◆ _busAddr

|

protected |

Definition at line 291 of file device.hh.

Referenced by busAddr(), PciDevice(), gem5::AMDGPUDevice::readConfig(), readConfig(), gem5::PciBridge::writeConfig(), writeConfig(), and gem5::PciEndpoint::writeConfig().

◆ _config

|

private |

The current config space.

Definition at line 281 of file device.hh.

Referenced by gem5::PciBridge::config(), gem5::PciEndpoint::config(), getAddrRanges(), interruptLine(), PciDevice(), readConfig(), serialize(), gem5::PciBridge::unserialize(), unserialize(), gem5::PciEndpoint::unserialize(), gem5::PciBridge::writeConfig(), writeConfig(), and gem5::PciEndpoint::writeConfig().

◆ BARs

|

protected |

Definition at line 324 of file device.hh.

Referenced by getAddrRanges(), getBAR(), PciDevice(), gem5::PciVirtIO::PciVirtIO(), gem5::sinic::Device::read(), gem5::PciBridge::unserialize(), gem5::PciEndpoint::unserialize(), gem5::sinic::Device::write(), gem5::PciBridge::writeConfig(), and gem5::PciEndpoint::writeConfig().

◆ configDelay

|

protected |

Definition at line 371 of file device.hh.

Referenced by PciDevice(), gem5::AMDGPUDevice::readConfig(), gem5::IdeController::readConfig(), readConfig(), gem5::AMDGPUDevice::writeConfig(), gem5::IdeController::writeConfig(), gem5::IGbE::writeConfig(), gem5::NSGigE::writeConfig(), gem5::PciBridge::writeConfig(), writeConfig(), and gem5::PciEndpoint::writeConfig().

◆ hostInterface

|

protected |

Definition at line 368 of file device.hh.

Referenced by intrClear(), intrPost(), PciDevice(), pciToDma(), gem5::PciBridge::unserialize(), gem5::PciEndpoint::unserialize(), gem5::PciBridge::writeConfig(), and gem5::PciEndpoint::writeConfig().

◆ msicap

|

protected |

Definition at line 303 of file device.hh.

Referenced by PciDevice(), serialize(), and unserialize().

◆ MSICAP_BASE

|

protected |

Definition at line 302 of file device.hh.

Referenced by PciDevice().

◆ msix_pba

|

protected |

Definition at line 322 of file device.hh.

Referenced by PciDevice(), serialize(), and unserialize().

◆ MSIX_PBA_END

|

protected |

Definition at line 313 of file device.hh.

Referenced by PciDevice().

◆ MSIX_PBA_OFFSET

|

protected |

Definition at line 312 of file device.hh.

Referenced by PciDevice().

◆ msix_table

|

protected |

MSIX Table and PBA Structures.

Definition at line 321 of file device.hh.

Referenced by PciDevice(), serialize(), and unserialize().

◆ MSIX_TABLE_END

|

protected |

Definition at line 311 of file device.hh.

Referenced by PciDevice().

◆ MSIX_TABLE_OFFSET

|

protected |

Definition at line 310 of file device.hh.

Referenced by PciDevice().

◆ msixcap

|

protected |

Definition at line 314 of file device.hh.

Referenced by PciDevice(), serialize(), and unserialize().

◆ MSIXCAP_BASE

|

protected |

Definition at line 305 of file device.hh.

Referenced by PciDevice(), serialize(), and unserialize().

◆ MSIXCAP_ID_OFFSET

|

protected |

Definition at line 306 of file device.hh.

Referenced by PciDevice().

◆ MSIXCAP_MPBA_OFFSET

|

protected |

Definition at line 309 of file device.hh.

Referenced by PciDevice().

◆ MSIXCAP_MTAB_OFFSET

|

protected |

Definition at line 308 of file device.hh.

Referenced by PciDevice().

◆ MSIXCAP_MXC_OFFSET

|

protected |

Definition at line 307 of file device.hh.

Referenced by PciDevice().

◆ PciBridge

◆ PciEndpoint

◆ pioDelay

|

protected |

Definition at line 370 of file device.hh.

Referenced by PciDevice(), gem5::AMDGPUDevice::read(), gem5::CopyEngine::read(), gem5::IdeController::read(), gem5::NSGigE::read(), gem5::sinic::Device::read(), gem5::AMDGPUDevice::write(), gem5::CopyEngine::write(), gem5::IdeController::write(), gem5::IGbE::write(), gem5::NSGigE::write(), and gem5::sinic::Device::write().

◆ pmcap

|

protected |

Definition at line 300 of file device.hh.

Referenced by PciDevice(), serialize(), and unserialize().

◆ PMCAP_BASE

|

protected |

The capability list structures and base addresses.

Definition at line 296 of file device.hh.

Referenced by PciDevice().

◆ PMCAP_ID_OFFSET

|

protected |

Definition at line 297 of file device.hh.

Referenced by PciDevice().

◆ PMCAP_PC_OFFSET

|

protected |

Definition at line 298 of file device.hh.

Referenced by PciDevice().

◆ PMCAP_PMCS_OFFSET

|

protected |

Definition at line 299 of file device.hh.

Referenced by PciDevice().

◆ pxcap

|

protected |

Definition at line 317 of file device.hh.

Referenced by PciDevice(), gem5::AMDGPUDevice::readConfig(), serialize(), unserialize(), and gem5::AMDGPUDevice::writeConfig().

◆ PXCAP_BASE

|

protected |

Definition at line 316 of file device.hh.

Referenced by PciDevice(), gem5::AMDGPUDevice::readConfig(), and gem5::AMDGPUDevice::writeConfig().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:53 for gem5 by doxygen 1.14.0