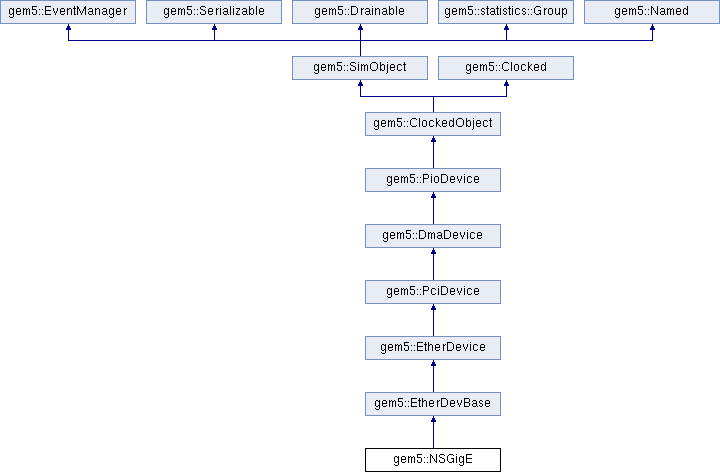

NS DP83820 Ethernet device model. More...

#include <ns_gige.hh>

Public Types | |

| enum | TxState { txIdle , txDescRefr , txDescRead , txFifoBlock , txFragRead , txDescWrite , txAdvance } |

| Transmit State Machine states. More... | |

| enum | RxState { rxIdle , rxDescRefr , rxDescRead , rxFifoBlock , rxFragWrite , rxDescWrite , rxAdvance } |

| Receive State Machine States. More... | |

| enum | DmaState { dmaIdle , dmaReading , dmaWriting , dmaReadWaiting , dmaWriteWaiting } |

| enum | EEPROMState { eepromStart , eepromGetOpcode , eepromGetAddress , eepromRead } |

| EEPROM State Machine States. More... | |

| Public Types inherited from gem5::EtherDevBase | |

| using | Params = EtherDevBaseParams |

| Public Types inherited from gem5::EtherDevice | |

| using | Params = EtherDeviceParams |

| Public Types inherited from gem5::DmaDevice | |

| typedef DmaDeviceParams | Params |

| Public Types inherited from gem5::PioDevice | |

| using | Params = PioDeviceParams |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| PARAMS (NSGigE) | |

| NSGigE (const Params ¶ms) | |

| ~NSGigE () | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Tick | writeConfig (PacketPtr pkt) override |

| This is to write to the PCI general configuration registers. | |

| Tick | read (PacketPtr pkt) override |

| This reads the device registers, which are detailed in the NS83820 spec sheet. | |

| Tick | write (PacketPtr pkt) override |

| Pure virtual function that the device must implement. | |

| bool | cpuIntrPending () const |

| void | cpuIntrAck () |

| bool | recvPacket (EthPacketPtr packet) |

| void | transferDone () |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| void | drainResume () override |

| Resume execution after a successful drain. | |

| Public Member Functions inherited from gem5::EtherDevBase | |

| EtherDevBase (const Params ¶ms) | |

| Public Member Functions inherited from gem5::EtherDevice | |

| EtherDevice (const Params ¶ms) | |

| Public Member Functions inherited from gem5::PciEndpoint | |

| PciEndpoint (const PciEndpointParams ¶ms) | |

| Constructor for PCI Dev. | |

| Tick | writeConfig (PacketPtr pkt) override |

| Write to the PCI config space data that is stored locally. | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. | |

| Public Member Functions inherited from gem5::PciDevice | |

| virtual Tick | readConfig (PacketPtr pkt) |

| Read from the PCI config space data that is stored locally. | |

| Addr | pciToDma (Addr pci_addr) const |

| void | intrPost () |

| void | intrClear () |

| uint8_t | interruptLine () const |

| AddrRangeList | getAddrRanges () const override |

| Determine the address ranges that this device responds to. | |

| PciDevice (const PciDeviceParams ¶ms, std::initializer_list< PciBar * > BARs_init) | |

| Constructor for PCI Dev. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. | |

| const PciBusAddr & | busAddr () const |

| Public Member Functions inherited from gem5::DmaDevice | |

| DmaDevice (const Params &p) | |

| virtual | ~DmaDevice ()=default |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| bool | dmaPending () const |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Addr | cacheBlockSize () const |

| Public Member Functions inherited from gem5::PioDevice | |

| PioDevice (const Params &p) | |

| virtual | ~PioDevice () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| bool | doRxDmaRead () |

| bool | doRxDmaWrite () |

| bool | doTxDmaRead () |

| bool | doTxDmaWrite () |

| void | rxDmaReadDone () |

| void | rxDmaWriteDone () |

| void | txDmaReadDone () |

| void | txDmaWriteDone () |

| void | txReset () |

| void | rxReset () |

| void | regsReset () |

| void | rxKick () |

| void | txKick () |

| void | eepromKick () |

| Advance the EEPROM state machine Called on rising edge of EEPROM clock bit in MEAR. | |

| void | transmit () |

| Retransmit event. | |

| void | txEventTransmit () |

| void | txDump () const |

| void | rxDump () const |

| bool | rxFilter (const EthPacketPtr &packet) |

| void | devIntrPost (uint32_t interrupts) |

| Interrupt management. | |

| void | devIntrClear (uint32_t interrupts) |

| void | devIntrChangeMask () |

| void | cpuIntrPost (Tick when) |

| void | cpuInterrupt () |

| void | cpuIntrClear () |

| Protected Member Functions inherited from gem5::PciEndpoint | |

| PCIConfigType0 & | config () |

| Protected Member Functions inherited from gem5::PciDevice | |

| bool | getBAR (Addr addr, int &num, Addr &offs) |

| Which base address register (if any) maps the given address? | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Detailed Description

NS DP83820 Ethernet device model.

Definition at line 123 of file ns_gige.hh.

Member Enumeration Documentation

◆ DmaState

| Enumerator | |

|---|---|

| dmaIdle | |

| dmaReading | |

| dmaWriting | |

| dmaReadWaiting | |

| dmaWriteWaiting | |

Definition at line 150 of file ns_gige.hh.

◆ EEPROMState

EEPROM State Machine States.

| Enumerator | |

|---|---|

| eepromStart | |

| eepromGetOpcode | |

| eepromGetAddress | |

| eepromRead | |

Definition at line 160 of file ns_gige.hh.

◆ RxState

Receive State Machine States.

| Enumerator | |

|---|---|

| rxIdle | |

| rxDescRefr | |

| rxDescRead | |

| rxFifoBlock | |

| rxFragWrite | |

| rxDescWrite | |

| rxAdvance | |

Definition at line 139 of file ns_gige.hh.

◆ TxState

Transmit State Machine states.

| Enumerator | |

|---|---|

| txIdle | |

| txDescRefr | |

| txDescRead | |

| txFifoBlock | |

| txFragRead | |

| txDescWrite | |

| txAdvance | |

Definition at line 127 of file ns_gige.hh.

Constructor & Destructor Documentation

◆ NSGigE()

| gem5::NSGigE::NSGigE | ( | const Params & | params | ) |

Definition at line 97 of file ns_gige.cc.

References CRDD, CTDD, dmaIdle, dmaReadDelay, dmaReadFactor, dmaWriteDelay, dmaWriteFactor, eepromAddress, eepromBitsToRx, eepromClk, eepromData, eepromOpcode, eepromStart, eepromState, gem5::EtherDevBase::EtherDevBase(), extstsEnable, ioEnable, gem5::MipsISA::p, rxDescCnt, rxDmaAddr, rxDmaData, rxDmaFree, rxDmaLen, rxDmaReadDone(), rxDmaReadEvent, rxDmaState, rxEnable, rxFifo, rxFragPtr, rxHalt, rxIdle, rxPacket, rxPacketBufPtr, rxPktBytes, rxState, rxXferLen, txDescCnt, txDmaAddr, txDmaData, txDmaFree, txDmaLen, txDmaState, txEnable, txFifo, txFragPtr, txHalt, txIdle, txPacket, txPacketBufPtr, txState, and txXferLen.

Referenced by PARAMS().

◆ ~NSGigE()

| gem5::NSGigE::~NSGigE | ( | ) |

Definition at line 142 of file ns_gige.cc.

References interface.

Member Function Documentation

◆ cpuInterrupt()

|

protected |

Definition at line 880 of file ns_gige.cc.

References cpuPendingIntr, gem5::curTick(), DPRINTF, intrEvent, gem5::PciDevice::intrPost(), and intrTick.

Referenced by cpuIntrPost(), and unserialize().

◆ cpuIntrAck()

|

inline |

Definition at line 348 of file ns_gige.hh.

References cpuIntrClear().

◆ cpuIntrClear()

|

protected |

Definition at line 903 of file ns_gige.cc.

References cpuPendingIntr, DPRINTF, gem5::PciDevice::intrClear(), intrEvent, and intrTick.

Referenced by cpuIntrAck(), devIntrChangeMask(), and devIntrClear().

◆ cpuIntrPending()

| bool gem5::NSGigE::cpuIntrPending | ( | ) | const |

Definition at line 922 of file ns_gige.cc.

References cpuPendingIntr.

◆ cpuIntrPost()

|

protected |

- Todo

- this warning should be removed and the intrTick code should be fixed.

Definition at line 844 of file ns_gige.cc.

References cpuInterrupt(), gem5::curTick(), DPRINTF, intrEvent, intrTick, name(), and gem5::EventManager::schedule().

Referenced by devIntrChangeMask(), and devIntrPost().

◆ devIntrChangeMask()

|

protected |

Definition at line 832 of file ns_gige.cc.

References cpuIntrClear(), cpuIntrPost(), gem5::curTick(), DPRINTF, and regs.

Referenced by write().

◆ devIntrClear()

|

protected |

Definition at line 790 of file ns_gige.cc.

References cpuIntrClear(), DPRINTF, gem5::EtherDevice::etherDeviceStats, gem5::ISR_NOIMPL, gem5::ISR_RESERVE, gem5::ISR_RXDESC, gem5::ISR_RXIDLE, gem5::ISR_RXOK, gem5::ISR_RXORN, gem5::ISR_SWI, gem5::ISR_TXDESC, gem5::ISR_TXIDLE, gem5::ISR_TXOK, panic, and regs.

Referenced by read().

◆ devIntrPost()

|

protected |

Interrupt management.

Definition at line 733 of file ns_gige.cc.

References cpuIntrPost(), gem5::curTick(), DPRINTF, gem5::EtherDevice::etherDeviceStats, intrDelay, gem5::ISR_IMPL, gem5::ISR_NODELAY, gem5::ISR_NOIMPL, gem5::ISR_RESERVE, gem5::ISR_RXDESC, gem5::ISR_RXIDLE, gem5::ISR_RXOK, gem5::ISR_RXORN, gem5::ISR_SWI, gem5::ISR_TXDESC, gem5::ISR_TXIDLE, gem5::ISR_TXOK, panic, regs, and warn.

Referenced by recvPacket(), rxKick(), transmit(), txKick(), and write().

◆ doRxDmaRead()

|

protected |

Definition at line 979 of file ns_gige.cc.

References dmaIdle, gem5::DmaDevice::dmaPending(), gem5::DmaDevice::dmaRead(), dmaReading, dmaReadWaiting, gem5::Drainable::drainState(), gem5::Running, rxDmaAddr, rxDmaData, rxDmaLen, rxDmaReadEvent, and rxDmaState.

Referenced by rxKick().

◆ doRxDmaWrite()

|

protected |

Definition at line 1010 of file ns_gige.cc.

References dmaIdle, gem5::DmaDevice::dmaPending(), gem5::DmaDevice::dmaWrite(), dmaWriteWaiting, dmaWriting, gem5::Drainable::drainState(), gem5::Running, rxDmaAddr, rxDmaData, rxDmaLen, rxDmaState, and rxDmaWriteEvent.

Referenced by rxKick().

◆ doTxDmaRead()

|

protected |

Definition at line 1406 of file ns_gige.cc.

References dmaIdle, gem5::DmaDevice::dmaPending(), gem5::DmaDevice::dmaRead(), dmaReading, dmaReadWaiting, gem5::Drainable::drainState(), gem5::Running, txDmaAddr, txDmaData, txDmaLen, txDmaReadEvent, and txDmaState.

Referenced by txKick().

◆ doTxDmaWrite()

|

protected |

Definition at line 1437 of file ns_gige.cc.

References dmaIdle, gem5::DmaDevice::dmaPending(), gem5::DmaDevice::dmaWrite(), dmaWriteWaiting, dmaWriting, gem5::Drainable::drainState(), gem5::Running, txDmaAddr, txDmaData, txDmaLen, txDmaState, and txDmaWriteEvent.

Referenced by txKick().

◆ drainResume()

|

overridevirtual |

Resume execution after a successful drain.

Reimplemented from gem5::Drainable.

Definition at line 2002 of file ns_gige.cc.

References gem5::Drainable::drainResume(), rxKick(), and txKick().

◆ eepromKick()

|

protected |

Advance the EEPROM state machine Called on rising edge of EEPROM clock bit in MEAR.

Definition at line 1799 of file ns_gige.cc.

References gem5::EEPROM_PMATCH0_ADDR, gem5::EEPROM_PMATCH1_ADDR, gem5::EEPROM_PMATCH2_ADDR, gem5::EEPROM_READ, gem5::igbreg::EEPROM_SIZE, eepromAddress, eepromBitsToRx, eepromData, eepromGetAddress, eepromGetOpcode, eepromOpcode, eepromRead, eepromStart, eepromState, gem5::MEAR_EEDI, gem5::MEAR_EEDO, panic, regs, and rom.

Referenced by write().

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

gem5 has a request and response port interface. All memory objects are connected together via ports. These ports provide a rigid interface between these memory objects. These ports implement three different memory system modes: timing, atomic, and functional. The most important mode is the timing mode and here timing mode is used for conducting cycle-level timing experiments. The other modes are only used in special circumstances and should not be used to conduct cycle-level timing experiments. The other modes are only used in special circumstances. These ports allow SimObjects to communicate with each other.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from gem5::DmaDevice.

Definition at line 175 of file ns_gige.cc.

References gem5::DmaDevice::getPort(), and interface.

◆ PARAMS()

| gem5::NSGigE::PARAMS | ( | NSGigE | ) |

References gem5::InvalidPortID, NSGigE(), and gem5::SimObject::params().

◆ read()

This reads the device registers, which are detailed in the NS83820 spec sheet.

Implements gem5::PioDevice.

Definition at line 187 of file ns_gige.cc.

References gem5::CCSR, gem5::CFGR, gem5::CR, gem5::CR_RXD, gem5::CR_RXR, gem5::CR_TXD, gem5::CR_TXR, devIntrClear(), DPRINTF, gem5::FHASH_ADDR, gem5::FHASH_SIZE, gem5::Packet::getAddr(), gem5::Packet::getPtr(), gem5::Packet::getSize(), gem5::GPIOR, gem5::IER, gem5::IHR, gem5::IMR, ioEnable, gem5::ISR, gem5::ISR_ALL, gem5::LAST, gem5::M5REG, gem5::M5REG_RSS, gem5::M5REG_RX_THREAD, gem5::M5REG_TX_THREAD, gem5::Packet::makeAtomicResponse(), gem5::MEAR, gem5::MIB_END, gem5::MIB_START, gem5::MIBC, gem5::MIBC_ACLR, gem5::MIBC_MIBS, panic, gem5::SimObject::params(), gem5::PCR, gem5::PciDevice::pioDelay, gem5::PQCR, gem5::PTSCR, gem5::PciDevice::readConfig(), gem5::X86ISA::reg, regs, gem5::RESERVED, gem5::RFCR, gem5::RFCR_RFADDR, gem5::RFDR, rom, gem5::RX_CFG, gem5::RXDP, gem5::RXDP_HI, gem5::Packet::setLE(), gem5::SRR, gem5::TANAR, gem5::TANER, gem5::TANLPAR, gem5::TBICR, gem5::TBISR, gem5::TESR, gem5::TX_CFG, gem5::TXDP, gem5::TXDP_HI, gem5::VDR, gem5::VRCR, gem5::VTCR, and gem5::WCSR.

◆ recvPacket()

| bool gem5::NSGigE::recvPacket | ( | EthPacketPtr | packet | ) |

Definition at line 1952 of file ns_gige.cc.

References devIntrPost(), DPRINTF, gem5::EtherDevice::etherDeviceStats, gem5::ISR_RXORN, rxEnable, rxFifo, rxFilter(), rxFilterEnable, and rxKick().

◆ regsReset()

|

protected |

Definition at line 956 of file ns_gige.cc.

References acceptArp, acceptBroadcast, acceptMulticast, acceptPerfect, acceptUnicast, gem5::CFGR_LNKSTS, gem5::CFGR_MODE_1000, gem5::CFGR_TBI_EN, extstsEnable, gem5::MIBC_FRZ, and regs.

Referenced by write().

◆ rxDmaReadDone()

|

protected |

Definition at line 993 of file ns_gige.cc.

References DDUMP, dmaIdle, dmaReading, dmaReadWaiting, dmaWriteWaiting, DPRINTF, rxDmaAddr, rxDmaData, rxDmaLen, rxDmaState, rxKick(), txDmaState, and txKick().

Referenced by NSGigE().

◆ rxDmaWriteDone()

|

protected |

Definition at line 1023 of file ns_gige.cc.

References DDUMP, dmaIdle, dmaReadWaiting, dmaWriteWaiting, dmaWriting, DPRINTF, rxDmaAddr, rxDmaData, rxDmaLen, rxDmaState, rxKick(), txDmaState, and txKick().

◆ rxDump()

|

protected |

◆ rxFilter()

|

protected |

Definition at line 1909 of file ns_gige.cc.

References acceptArp, acceptBroadcast, acceptMulticast, acceptPerfect, acceptUnicast, gem5::networking::EthAddr::broadcast(), DDUMP, DPRINTF, gem5::networking::EthHdr::dst(), gem5::networking::EthAddr::multicast(), multicastHashEnable, rom, gem5::networking::EthHdr::type(), and gem5::networking::EthAddr::unicast().

Referenced by recvPacket().

◆ rxKick()

|

protected |

- Todo

- in reality, we should be able to start processing the packet as it arrives, and not have to wait for the full packet ot be in the receive fifo.

- Todo

- do we want to schedule a future kick?

Definition at line 1040 of file ns_gige.cc.

References gem5::CFGR_M64ADDR, gem5::networking::cksum(), gem5::Clocked::clockEdge(), gem5::CMDSTS_INTR, gem5::CMDSTS_LEN_MASK, gem5::CMDSTS_MORE, gem5::CMDSTS_OK, gem5::CMDSTS_OWN, CRDD, gem5::curTick(), devIntrPost(), dmaDataFree, dmaDescFree, dmaIdle, dmaReadWaiting, dmaWriteWaiting, doRxDmaRead(), doRxDmaWrite(), DPRINTF, gem5::EtherDevice::etherDeviceStats, gem5::X86ISA::exit, gem5::EXTSTS_IPERR, gem5::EXTSTS_IPPKT, gem5::EXTSTS_TCPERR, gem5::EXTSTS_TCPPKT, gem5::EXTSTS_UDPERR, gem5::EXTSTS_UDPPKT, extstsEnable, gem5::ISR_RXDESC, gem5::ISR_RXIDLE, gem5::ISR_RXOK, gem5::NsRxStateStrings, panic, regs, rxAdvance, rxDesc32, rxDesc64, rxDescCnt, rxDescRead, rxDescRefr, rxDescWrite, rxDmaAddr, rxDmaData, rxDmaFree, rxDmaLen, rxDmaState, rxEnable, rxFifo, rxFifoBlock, rxFragPtr, rxFragWrite, rxIdle, rxKickEvent, rxKickTick, rxPacket, rxPacketBufPtr, rxPktBytes, rxState, rxXferLen, and gem5::EventManager::schedule().

Referenced by drainResume(), recvPacket(), rxDmaReadDone(), rxDmaWriteDone(), txDmaReadDone(), txDmaWriteDone(), and write().

◆ rxReset()

|

protected |

Definition at line 941 of file ns_gige.cc.

References CRDD, dmaIdle, DPRINTF, rxDescCnt, rxDmaState, rxEnable, rxFifo, rxFragPtr, rxIdle, rxPktBytes, and rxState.

Referenced by write().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 2018 of file ns_gige.cc.

References acceptArp, acceptBroadcast, acceptMulticast, acceptPerfect, acceptUnicast, cpuPendingIntr, CRDD, CTDD, gem5::curTick(), eepromAddress, eepromBitsToRx, eepromClk, eepromData, eepromOpcode, eepromState, extstsEnable, gem5::FHASH_SIZE, intrEvent, intrTick, ioEnable, multicastHashEnable, regs, rom, rxDesc32, rxDesc64, rxDescCnt, rxDmaState, rxEnable, rxFifo, rxFilterEnable, rxFragPtr, rxKickTick, rxPacket, rxPacketBufPtr, rxPktBytes, rxState, rxXferLen, gem5::PciDevice::serialize(), SERIALIZE_ARRAY, SERIALIZE_SCALAR, txDesc32, txDesc64, txDescCnt, txDmaState, txEnable, txEvent, txFifo, txFragPtr, txKickTick, txPacket, txPacketBufPtr, txState, and txXferLen.

◆ transferDone()

| void gem5::NSGigE::transferDone | ( | ) |

Definition at line 1896 of file ns_gige.cc.

References gem5::Clocked::clockEdge(), DPRINTF, gem5::EventManager::reschedule(), txEvent, and txFifo.

◆ transmit()

|

protected |

Retransmit event.

Definition at line 1355 of file ns_gige.cc.

References gem5::curTick(), DDUMP, devIntrPost(), DPRINTF, gem5::EtherDevice::etherDeviceStats, interface, gem5::ISR_TXOK, gem5::sim_clock::as_int::ns, gem5::EventManager::schedule(), txEvent, and txFifo.

Referenced by txEventTransmit(), and txKick().

◆ txDmaReadDone()

|

protected |

Definition at line 1420 of file ns_gige.cc.

References DDUMP, dmaIdle, dmaReading, dmaReadWaiting, dmaWriteWaiting, DPRINTF, rxDmaState, rxKick(), txDmaAddr, txDmaData, txDmaLen, txDmaState, and txKick().

◆ txDmaWriteDone()

|

protected |

Definition at line 1450 of file ns_gige.cc.

References DDUMP, dmaIdle, dmaReadWaiting, dmaWriteWaiting, dmaWriting, DPRINTF, rxDmaState, rxKick(), txDmaAddr, txDmaData, txDmaLen, txDmaState, and txKick().

◆ txDump()

|

protected |

◆ txEventTransmit()

|

inlineprotected |

Definition at line 293 of file ns_gige.hh.

References transmit(), txFifoBlock, txKick(), and txState.

◆ txKick()

|

protected |

- Todo

- do we want to schedule a future kick?

Definition at line 1467 of file ns_gige.cc.

References gem5::debug::breakpoint(), gem5::CFGR_M64ADDR, gem5::networking::cksum(), gem5::Clocked::clockEdge(), gem5::CMDSTS_INTR, gem5::CMDSTS_LEN_MASK, gem5::CMDSTS_MORE, gem5::CMDSTS_OK, gem5::CMDSTS_OWN, CTDD, gem5::curTick(), devIntrPost(), dmaDataFree, dmaDescFree, dmaIdle, dmaReadWaiting, dmaWriteWaiting, doTxDmaRead(), doTxDmaWrite(), DPRINTF, gem5::EtherDevice::etherDeviceStats, gem5::X86ISA::exit, gem5::EXTSTS_IPPKT, gem5::EXTSTS_TCPPKT, gem5::EXTSTS_UDPPKT, extstsEnable, gem5::ISR_TXDESC, gem5::ISR_TXIDLE, gem5::NsTxStateStrings, panic, regs, gem5::EventManager::schedule(), gem5::networking::UdpHdr::sum(), transmit(), txAdvance, txDesc32, txDesc64, txDescCnt, txDescRead, txDescRefr, txDescWrite, txDmaAddr, txDmaData, txDmaFree, txDmaLen, txDmaState, txEnable, txFifo, txFifoBlock, txFragPtr, txFragRead, txIdle, txKickEvent, txKickTick, txPacket, txPacketBufPtr, txState, txXferLen, gem5::VTCR_PPCHK, and warn_once.

Referenced by drainResume(), rxDmaReadDone(), rxDmaWriteDone(), txDmaReadDone(), txDmaWriteDone(), txEventTransmit(), and write().

◆ txReset()

|

protected |

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 2191 of file ns_gige.cc.

References acceptArp, acceptBroadcast, acceptMulticast, acceptPerfect, acceptUnicast, cpuInterrupt(), cpuPendingIntr, CRDD, CTDD, gem5::curTick(), eepromAddress, eepromBitsToRx, eepromClk, eepromData, eepromOpcode, eepromState, extstsEnable, gem5::FHASH_SIZE, intrEvent, intrTick, ioEnable, multicastHashEnable, name(), regs, rom, rxDesc32, rxDesc64, rxDescCnt, rxDmaState, rxEnable, rxFifo, rxFilterEnable, rxFragPtr, rxKickEvent, rxKickTick, rxPacket, rxPacketBufPtr, rxPktBytes, rxState, rxXferLen, gem5::EventManager::schedule(), txDesc32, txDesc64, txDescCnt, txDmaState, txEnable, txEvent, txFifo, txFragPtr, txKickEvent, txKickTick, txPacket, txPacketBufPtr, txState, txXferLen, gem5::PciEndpoint::unserialize(), UNSERIALIZE_ARRAY, and UNSERIALIZE_SCALAR.

◆ write()

Pure virtual function that the device must implement.

Called when a write command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 409 of file ns_gige.cc.

References acceptArp, acceptBroadcast, acceptMulticast, acceptPerfect, acceptUnicast, gem5::BRAR, gem5::BRDR, gem5::CCSR, gem5::CFGR, gem5::CFGR_AUTO_1000, gem5::CFGR_DUPSTS, gem5::CFGR_EXTSTS_EN, gem5::CFGR_LNKSTS, gem5::CFGR_PCI64_DET, gem5::CFGR_RESERVED, gem5::CFGR_SPDSTS, gem5::CFGR_T64ADDR, gem5::CR, gem5::CR_RST, gem5::CR_RXD, gem5::CR_RXE, gem5::CR_RXR, gem5::CR_SWI, gem5::CR_TXD, gem5::CR_TXE, gem5::CR_TXR, CRDD, CTDD, devIntrChangeMask(), devIntrPost(), DPRINTF, eepromClk, eepromKick(), eepromStart, eepromState, extstsEnable, gem5::FHASH_ADDR, gem5::FHASH_SIZE, gem5::Packet::getAddr(), gem5::Packet::getLE(), gem5::Packet::getSize(), gem5::GPIOR, gem5::GPIOR_GP1_IN, gem5::GPIOR_GP2_IN, gem5::GPIOR_GP3_IN, gem5::GPIOR_GP4_IN, gem5::GPIOR_GP5_IN, gem5::GPIOR_UNUSED, gem5::IER, gem5::IHR, gem5::IMR, ioEnable, gem5::ISR, gem5::ISR_SWI, gem5::LAST, gem5::Packet::makeAtomicResponse(), gem5::MEAR, gem5::MEAR_EECLK, gem5::MEAR_EEDI, gem5::MEAR_EEDO, gem5::MEAR_EESEL, gem5::MIBC, multicastHashEnable, panic, gem5::PCR, gem5::PciDevice::pioDelay, gem5::PQCR, gem5::PTSCR, gem5::PTSCR_EEBIST_EN, gem5::PTSCR_EELOAD_EN, gem5::PTSCR_RBIST_DONE, gem5::PTSCR_RBIST_EN, gem5::PTSCR_RBIST_RDONLY, gem5::X86ISA::reg, regs, regsReset(), gem5::RESERVED, gem5::RFCR, gem5::RFCR_AAB, gem5::RFCR_AAM, gem5::RFCR_AARP, gem5::RFCR_AAU, gem5::RFCR_APM, gem5::RFCR_MHEN, gem5::RFCR_RFADDR, gem5::RFCR_RFEN, gem5::RFCR_UHEN, gem5::RFCR_ULM, gem5::RFDR, rom, gem5::RX_CFG, gem5::RXDP, gem5::RXDP_HI, rxEnable, rxFilterEnable, rxIdle, rxKick(), rxReset(), rxState, gem5::SRR, gem5::TANAR, gem5::TANAR_RF1, gem5::TANAR_RF2, gem5::TANAR_UNUSED, gem5::TANER, gem5::TANLPAR, gem5::TBICR, gem5::TBICR_MR_AN_ENABLE, gem5::TBICR_MR_LOOPBACK, gem5::TBISR, gem5::TBISR_MR_AN_COMPLETE, gem5::TBISR_MR_LINK_STATUS, gem5::TESR, gem5::TX_CFG, gem5::TXDP, gem5::TXDP_HI, txEnable, txIdle, txKick(), txReset(), txState, gem5::VDR, gem5::VRCR, gem5::VTCR, gem5::WCSR, and writeConfig().

◆ writeConfig()

This is to write to the PCI general configuration registers.

Reimplemented from gem5::PciDevice.

Definition at line 151 of file ns_gige.cc.

References gem5::PciEndpoint::config(), gem5::PciDevice::configDelay, gem5::Packet::getAddr(), ioEnable, gem5::ArmISA::offset, panic, PCI_CMD_IOSE, PCI_COMMAND, PCI_CONFIG_SIZE, PCI_DEVICE_SPECIFIC, and gem5::PciEndpoint::writeConfig().

Referenced by write().

Member Data Documentation

◆ acceptArp

|

protected |

Definition at line 313 of file ns_gige.hh.

Referenced by regsReset(), rxFilter(), serialize(), unserialize(), and write().

◆ acceptBroadcast

|

protected |

Definition at line 309 of file ns_gige.hh.

Referenced by regsReset(), rxFilter(), serialize(), unserialize(), and write().

◆ acceptMulticast

|

protected |

Definition at line 310 of file ns_gige.hh.

Referenced by regsReset(), rxFilter(), serialize(), unserialize(), and write().

◆ acceptPerfect

|

protected |

Definition at line 312 of file ns_gige.hh.

Referenced by regsReset(), rxFilter(), serialize(), unserialize(), and write().

◆ acceptUnicast

|

protected |

Definition at line 311 of file ns_gige.hh.

Referenced by regsReset(), rxFilter(), serialize(), unserialize(), and write().

◆ cpuPendingIntr

|

protected |

Definition at line 325 of file ns_gige.hh.

Referenced by cpuInterrupt(), cpuIntrClear(), cpuIntrPending(), serialize(), and unserialize().

◆ CRDD

|

protected |

Current Receive Descriptor Done.

Definition at line 216 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), rxReset(), serialize(), unserialize(), and write().

◆ CTDD

|

protected |

Current Transmit Descriptor Done.

Definition at line 202 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txKick(), txReset(), unserialize(), and write().

◆ dmaDataFree

|

protected |

Definition at line 269 of file ns_gige.hh.

◆ dmaDescFree

|

protected |

Definition at line 268 of file ns_gige.hh.

◆ dmaReadDelay

|

protected |

Definition at line 238 of file ns_gige.hh.

Referenced by NSGigE().

◆ dmaReadFactor

|

protected |

Definition at line 241 of file ns_gige.hh.

Referenced by NSGigE().

◆ dmaWriteDelay

|

protected |

Definition at line 239 of file ns_gige.hh.

Referenced by NSGigE().

◆ dmaWriteFactor

|

protected |

Definition at line 242 of file ns_gige.hh.

Referenced by NSGigE().

◆ eepromAddress

|

protected |

Definition at line 234 of file ns_gige.hh.

Referenced by eepromKick(), NSGigE(), serialize(), and unserialize().

◆ eepromBitsToRx

|

protected |

Definition at line 232 of file ns_gige.hh.

Referenced by eepromKick(), NSGigE(), serialize(), and unserialize().

◆ eepromClk

|

protected |

Definition at line 231 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), unserialize(), and write().

◆ eepromData

|

protected |

Definition at line 235 of file ns_gige.hh.

Referenced by eepromKick(), NSGigE(), serialize(), and unserialize().

◆ eepromOpcode

|

protected |

Definition at line 233 of file ns_gige.hh.

Referenced by eepromKick(), NSGigE(), serialize(), and unserialize().

◆ eepromState

|

protected |

EEPROM State Machine.

Definition at line 230 of file ns_gige.hh.

Referenced by eepromKick(), NSGigE(), serialize(), unserialize(), and write().

◆ extstsEnable

|

protected |

Definition at line 227 of file ns_gige.hh.

Referenced by NSGigE(), regsReset(), rxKick(), serialize(), txKick(), unserialize(), and write().

◆ interface

|

protected |

Definition at line 331 of file ns_gige.hh.

Referenced by getPort(), transmit(), and ~NSGigE().

◆ intrDelay

|

protected |

Definition at line 323 of file ns_gige.hh.

Referenced by devIntrPost().

◆ intrEvent

|

protected |

Definition at line 330 of file ns_gige.hh.

Referenced by cpuInterrupt(), cpuIntrClear(), cpuIntrPost(), serialize(), and unserialize().

◆ intrTick

|

protected |

Definition at line 324 of file ns_gige.hh.

Referenced by cpuInterrupt(), cpuIntrClear(), cpuIntrPost(), serialize(), and unserialize().

◆ ioEnable

|

protected |

pci settings

Definition at line 174 of file ns_gige.hh.

Referenced by NSGigE(), read(), serialize(), unserialize(), write(), and writeConfig().

◆ multicastHashEnable

|

protected |

Definition at line 314 of file ns_gige.hh.

Referenced by rxFilter(), serialize(), unserialize(), and write().

◆ regs

|

protected |

device register file

Definition at line 170 of file ns_gige.hh.

Referenced by devIntrChangeMask(), devIntrClear(), devIntrPost(), eepromKick(), read(), regsReset(), rxKick(), serialize(), txKick(), unserialize(), and write().

◆ rom

|

protected |

Definition at line 171 of file ns_gige.hh.

Referenced by eepromKick(), read(), rxFilter(), serialize(), unserialize(), and write().

◆ rxDelay

|

protected |

Definition at line 273 of file ns_gige.hh.

◆ rxDesc32

|

protected |

Definition at line 193 of file ns_gige.hh.

Referenced by rxKick(), serialize(), and unserialize().

◆ rxDesc64

|

protected |

Definition at line 195 of file ns_gige.hh.

Referenced by rxKick(), serialize(), and unserialize().

◆ rxDescCnt

|

protected |

count of bytes remaining in the current descriptor

Definition at line 224 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), rxReset(), serialize(), and unserialize().

◆ rxDmaAddr

|

protected |

Definition at line 245 of file ns_gige.hh.

Referenced by doRxDmaRead(), doRxDmaWrite(), NSGigE(), rxDmaReadDone(), rxDmaWriteDone(), and rxKick().

◆ rxDmaData

|

protected |

Definition at line 244 of file ns_gige.hh.

Referenced by doRxDmaRead(), doRxDmaWrite(), NSGigE(), rxDmaReadDone(), rxDmaWriteDone(), and rxKick().

◆ rxDmaFree

|

protected |

Definition at line 188 of file ns_gige.hh.

◆ rxDmaLen

|

protected |

Definition at line 246 of file ns_gige.hh.

Referenced by doRxDmaRead(), doRxDmaWrite(), NSGigE(), rxDmaReadDone(), rxDmaWriteDone(), and rxKick().

◆ rxDmaReadEvent

|

protected |

Definition at line 257 of file ns_gige.hh.

Referenced by doRxDmaRead(), and NSGigE().

◆ rxDmaState

|

protected |

Definition at line 225 of file ns_gige.hh.

Referenced by doRxDmaRead(), doRxDmaWrite(), NSGigE(), rxDmaReadDone(), rxDmaWriteDone(), rxKick(), rxReset(), serialize(), txDmaReadDone(), txDmaWriteDone(), and unserialize().

◆ rxDmaWriteEvent

|

protected |

Definition at line 260 of file ns_gige.hh.

Referenced by doRxDmaWrite().

◆ rxEnable

|

protected |

Definition at line 213 of file ns_gige.hh.

Referenced by NSGigE(), recvPacket(), rxKick(), rxReset(), serialize(), unserialize(), and write().

◆ rxFifo

|

protected |

Definition at line 179 of file ns_gige.hh.

Referenced by NSGigE(), recvPacket(), rxKick(), rxReset(), serialize(), and unserialize().

◆ rxFilterEnable

|

protected |

receive address filter

Definition at line 307 of file ns_gige.hh.

Referenced by recvPacket(), serialize(), unserialize(), and write().

◆ rxFragPtr

|

protected |

ptr to the next byte in current fragment

Definition at line 222 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), rxReset(), serialize(), and unserialize().

◆ rxHalt

|

protected |

halt the rx state machine after current packet

Definition at line 220 of file ns_gige.hh.

Referenced by NSGigE().

◆ rxKickEvent

|

protected |

Definition at line 281 of file ns_gige.hh.

Referenced by rxKick(), and unserialize().

◆ rxKickTick

|

protected |

Definition at line 280 of file ns_gige.hh.

Referenced by rxKick(), serialize(), and unserialize().

◆ rxPacket

|

protected |

Definition at line 183 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), serialize(), and unserialize().

◆ rxPacketBufPtr

|

protected |

Definition at line 185 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), serialize(), and unserialize().

◆ rxPktBytes

|

protected |

num of bytes in the current packet being drained from rxDataFifo

Definition at line 218 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), rxReset(), serialize(), and unserialize().

◆ rxState

|

protected |

rx State Machine

Definition at line 212 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), rxReset(), serialize(), unserialize(), and write().

◆ rxXferLen

|

protected |

Definition at line 187 of file ns_gige.hh.

Referenced by NSGigE(), rxKick(), serialize(), and unserialize().

◆ txDelay

|

protected |

Definition at line 272 of file ns_gige.hh.

◆ txDesc32

|

protected |

DescCaches.

Definition at line 192 of file ns_gige.hh.

Referenced by serialize(), txKick(), and unserialize().

◆ txDesc64

|

protected |

Definition at line 194 of file ns_gige.hh.

Referenced by serialize(), txKick(), and unserialize().

◆ txDescCnt

|

protected |

count of bytes remaining in the current descriptor

Definition at line 208 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txKick(), txReset(), and unserialize().

◆ txDmaAddr

|

protected |

Definition at line 251 of file ns_gige.hh.

Referenced by doTxDmaRead(), doTxDmaWrite(), NSGigE(), txDmaReadDone(), txDmaWriteDone(), and txKick().

◆ txDmaData

|

protected |

Definition at line 250 of file ns_gige.hh.

Referenced by doTxDmaRead(), doTxDmaWrite(), NSGigE(), txDmaReadDone(), txDmaWriteDone(), and txKick().

◆ txDmaFree

|

protected |

Definition at line 189 of file ns_gige.hh.

◆ txDmaLen

|

protected |

Definition at line 252 of file ns_gige.hh.

Referenced by doTxDmaRead(), doTxDmaWrite(), NSGigE(), txDmaReadDone(), txDmaWriteDone(), and txKick().

◆ txDmaReadEvent

|

protected |

Definition at line 263 of file ns_gige.hh.

Referenced by doTxDmaRead().

◆ txDmaState

|

protected |

Definition at line 209 of file ns_gige.hh.

Referenced by doTxDmaRead(), doTxDmaWrite(), NSGigE(), rxDmaReadDone(), rxDmaWriteDone(), serialize(), txDmaReadDone(), txDmaWriteDone(), txKick(), txReset(), and unserialize().

◆ txDmaWriteEvent

|

protected |

Definition at line 266 of file ns_gige.hh.

Referenced by doTxDmaWrite().

◆ txEnable

|

protected |

Definition at line 199 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txKick(), txReset(), unserialize(), and write().

◆ txEvent

|

protected |

Definition at line 299 of file ns_gige.hh.

Referenced by serialize(), transferDone(), transmit(), and unserialize().

◆ txFifo

|

protected |

Definition at line 178 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), transferDone(), transmit(), txKick(), txReset(), and unserialize().

◆ txFragPtr

|

protected |

ptr to the next byte in the current fragment

Definition at line 206 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txKick(), txReset(), and unserialize().

◆ txHalt

|

protected |

halt the tx state machine after next packet

Definition at line 204 of file ns_gige.hh.

Referenced by NSGigE().

◆ txKickEvent

|

protected |

Definition at line 285 of file ns_gige.hh.

Referenced by txKick(), and unserialize().

◆ txKickTick

|

protected |

Definition at line 284 of file ns_gige.hh.

Referenced by serialize(), txKick(), and unserialize().

◆ txPacket

|

protected |

various helper vars

Definition at line 182 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txKick(), and unserialize().

◆ txPacketBufPtr

|

protected |

Definition at line 184 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txKick(), and unserialize().

◆ txState

|

protected |

Definition at line 198 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txEventTransmit(), txKick(), txReset(), unserialize(), and write().

◆ txXferLen

|

protected |

Definition at line 186 of file ns_gige.hh.

Referenced by NSGigE(), serialize(), txKick(), and unserialize().

The documentation for this class was generated from the following files:

- dev/net/ns_gige.hh

- dev/net/ns_gige.cc

Generated on Sat Oct 18 2025 08:06:52 for gem5 by doxygen 1.14.0