#include <uart8250.hh>

Classes | |

| class | Registers |

Public Types | |

| using | Params = Uart8250Params |

| Public Types inherited from gem5::Uart | |

| using | Params = UartParams |

| Public Types inherited from gem5::PioDevice | |

| using | Params = PioDeviceParams |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| Uart8250 (const Params &p) | |

| Tick | read (PacketPtr pkt) override |

| Pure virtual function that the device must implement. | |

| Tick | write (PacketPtr pkt) override |

| Pure virtual function that the device must implement. | |

| AddrRangeList | getAddrRanges () const override |

| Determine the address ranges that this device responds to. | |

| void | dataAvailable () override |

| Inform the uart that there is data available. | |

| virtual bool | intStatus () |

| Return if we have an interrupt pending. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::Uart | |

| Uart (const Params &p, Addr pio_size) | |

| bool | intStatus () |

| Return if we have an interrupt pending. | |

| Public Member Functions inherited from gem5::BasicPioDevice | |

| PARAMS (BasicPioDevice) | |

| BasicPioDevice (const Params &p, Addr size) | |

| Public Member Functions inherited from gem5::PioDevice | |

| PioDevice (const Params &p) | |

| virtual | ~PioDevice () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Types | |

| using | Register8 = Registers::Register8 |

| template<class T> | |

| using | Register = Registers::Register<T> |

Protected Member Functions | |

| BitUnion8 (Ier) Bitfield< 0 > rdi | |

| EndBitUnion (Ier) BitUnion8(Iir) Bitfield< 0 > pending | |

| EndBitUnion (Iir) BitUnion8(Lcr) Bitfield< 1 | |

| EndBitUnion (Lcr) BitUnion8(Lsr) Bitfield< 0 > rdr | |

| EndBitUnion (Lsr) enum class InterruptIds | |

| uint8_t | readRbr (Register8 ®) |

| void | writeThr (Register8 ®, const uint8_t &data) |

| void | writeIer (Register< Ier > ®, const Ier &ier) |

| Iir | readIir (Register< Iir > ®) |

| void | processIntrEvent (int intrBit) |

| void | scheduleIntr (Event *event) |

| void | clearIntr (int intrBit) |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| Bitfield< 1 > | thri |

| Bitfield< 2 > | rlsi |

| Bitfield< 3 > | msi |

| Bitfield< 2, 1 > | id |

| Bitfield< 7, 3 > | zeroes |

| wordSize | |

| Bitfield< 2 > | stopBits |

| Bitfield< 5, 3 > | parity |

| Bitfield< 6 > | breakCont |

| Bitfield< 7 > | dlab |

| Bitfield< 1 > | overrunError |

| Bitfield< 2 > | parityError |

| Bitfield< 3 > | framingError |

| Bitfield< 4 > | breakCond |

| Bitfield< 5 > | tbe |

| Bitfield< 6 > | txEmpty |

| Bitfield< 7 > | unused |

| Registers | registers |

| Tick | lastTxInt |

| EventFunctionWrapper | txIntrEvent |

| EventFunctionWrapper | rxIntrEvent |

| Protected Attributes inherited from gem5::Uart | |

| int | status |

| Platform * | platform |

| SerialDevice * | device |

| Protected Attributes inherited from gem5::BasicPioDevice | |

| Addr | pioAddr |

| Address that the device listens to. | |

| Addr | pioSize |

| Size that the device's address range. | |

| Tick | pioDelay |

| Delay that the device experinces on an access. | |

| Protected Attributes inherited from gem5::PioDevice | |

| System * | sys |

| PioPort< PioDevice > | pioPort |

| The pioPort that handles the requests for us and provides us requests that it sees. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Detailed Description

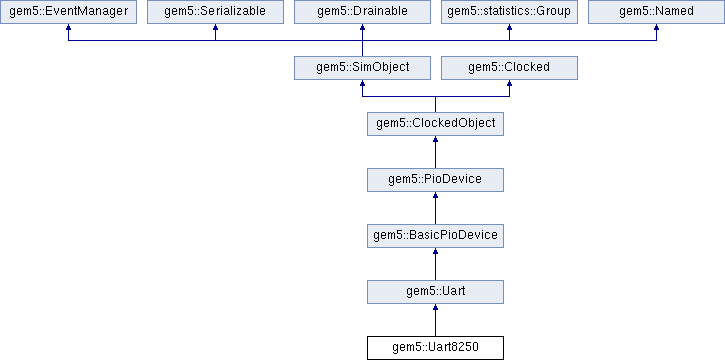

Definition at line 51 of file uart8250.hh.

Member Typedef Documentation

◆ Params

| using gem5::Uart8250::Params = Uart8250Params |

Definition at line 224 of file uart8250.hh.

◆ Register

|

protected |

Definition at line 205 of file uart8250.hh.

◆ Register8

|

protected |

Definition at line 203 of file uart8250.hh.

Constructor & Destructor Documentation

◆ Uart8250()

| gem5::Uart8250::Uart8250 | ( | const Params & | p | ) |

Definition at line 101 of file uart8250.cc.

References lastTxInt, name(), gem5::MipsISA::p, processIntrEvent(), registers, gem5::TX_INT, txIntrEvent, and gem5::Uart::Uart().

Referenced by gem5::Uart8250::Registers::Registers().

Member Function Documentation

◆ BitUnion8()

|

protected |

Referenced by EndBitUnion().

◆ clearIntr()

|

protected |

Definition at line 88 of file uart8250.cc.

References gem5::Uart::platform, and gem5::Uart::status.

Referenced by readIir(), readRbr(), writeIer(), and writeThr().

◆ dataAvailable()

|

overridevirtual |

Inform the uart that there is data available.

Implements gem5::Uart.

Definition at line 265 of file uart8250.cc.

References gem5::Uart::platform, registers, gem5::RX_INT, and gem5::Uart::status.

◆ EndBitUnion() [1/4]

|

protected |

Referenced by EndBitUnion(), and EndBitUnion().

◆ EndBitUnion() [2/4]

|

protected |

◆ EndBitUnion() [3/4]

|

protected |

References BitUnion8(), and EndBitUnion().

◆ EndBitUnion() [4/4]

|

inlineprotected |

Definition at line 84 of file uart8250.hh.

References EndBitUnion().

◆ getAddrRanges()

|

overridevirtual |

Determine the address ranges that this device responds to.

- Returns

- a list of non-overlapping address ranges

Reimplemented from gem5::BasicPioDevice.

Definition at line 275 of file uart8250.cc.

References gem5::BasicPioDevice::pioAddr, gem5::BasicPioDevice::pioSize, and gem5::RangeSize().

◆ intStatus()

|

inlinevirtual |

Return if we have an interrupt pending.

- Returns

- interrupt status

Definition at line 241 of file uart8250.hh.

References gem5::Uart::status.

◆ processIntrEvent()

|

protected |

Definition at line 50 of file uart8250.cc.

References gem5::curTick(), DPRINTF, lastTxInt, gem5::Uart::platform, registers, gem5::Uart::status, and gem5::Uart::Uart().

Referenced by Uart8250().

◆ read()

Pure virtual function that the device must implement.

Called when a read command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 238 of file uart8250.cc.

References DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getPtr(), gem5::Packet::getSize(), gem5::Packet::makeAtomicResponse(), gem5::BasicPioDevice::pioAddr, gem5::BasicPioDevice::pioDelay, registers, and gem5::Uart::Uart().

◆ readIir()

|

protected |

Definition at line 180 of file uart8250.cc.

References clearIntr(), gem5::EventManager::deschedule(), DPRINTF, gem5::X86ISA::reg, gem5::RX_INT, gem5::Uart::status, gem5::TX_INT, txIntrEvent, and gem5::Uart::Uart().

Referenced by gem5::Uart8250::Registers::Registers().

◆ readRbr()

|

protected |

Definition at line 145 of file uart8250.cc.

References clearIntr(), data, gem5::EventManager::deschedule(), gem5::Uart::device, DPRINTF, gem5::X86ISA::reg, registers, gem5::RX_INT, rxIntrEvent, scheduleIntr(), and gem5::Uart::Uart().

Referenced by gem5::Uart8250::Registers::Registers().

◆ scheduleIntr()

|

protected |

Definition at line 75 of file uart8250.cc.

References gem5::curTick(), DPRINTF, gem5::MipsISA::event, gem5::sim_clock::as_int::ns, gem5::EventManager::reschedule(), gem5::EventManager::schedule(), and gem5::Uart::Uart().

Referenced by readRbr(), writeIer(), and writeThr().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 283 of file uart8250.cc.

References gem5::paramOut(), registers, rxIntrEvent, SERIALIZE_SCALAR, gem5::Uart::status, and txIntrEvent.

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 306 of file uart8250.cc.

References gem5::paramIn(), registers, rxIntrEvent, gem5::EventManager::schedule(), gem5::Uart::status, txIntrEvent, and UNSERIALIZE_SCALAR.

◆ write()

Pure virtual function that the device must implement.

Called when a write command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 251 of file uart8250.cc.

References DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getPtr(), gem5::Packet::getRaw(), gem5::Packet::getSize(), gem5::Packet::makeAtomicResponse(), gem5::BasicPioDevice::pioAddr, gem5::BasicPioDevice::pioDelay, registers, and gem5::Uart::Uart().

◆ writeIer()

|

protected |

Definition at line 202 of file uart8250.cc.

References clearIntr(), gem5::curTick(), gem5::EventManager::deschedule(), gem5::Uart::device, DPRINTF, lastTxInt, gem5::sim_clock::as_int::ns, gem5::X86ISA::reg, gem5::RX_INT, rxIntrEvent, scheduleIntr(), gem5::TX_INT, txIntrEvent, and gem5::Uart::Uart().

Referenced by gem5::Uart8250::Registers::Registers().

◆ writeThr()

|

protected |

Definition at line 168 of file uart8250.cc.

References clearIntr(), data, gem5::EventManager::deschedule(), gem5::Uart::device, gem5::X86ISA::reg, registers, scheduleIntr(), gem5::TX_INT, and txIntrEvent.

Referenced by gem5::Uart8250::Registers::Registers().

Member Data Documentation

◆ breakCond

|

protected |

Definition at line 80 of file uart8250.hh.

◆ breakCont

|

protected |

Definition at line 71 of file uart8250.hh.

◆ dlab

|

protected |

Definition at line 72 of file uart8250.hh.

◆ framingError

|

protected |

Definition at line 79 of file uart8250.hh.

◆ id

|

protected |

Definition at line 63 of file uart8250.hh.

◆ lastTxInt

|

protected |

Definition at line 214 of file uart8250.hh.

Referenced by processIntrEvent(), Uart8250(), and writeIer().

◆ msi

|

protected |

Definition at line 58 of file uart8250.hh.

◆ overrunError

|

protected |

Definition at line 77 of file uart8250.hh.

◆ parity

|

protected |

Definition at line 70 of file uart8250.hh.

◆ parityError

|

protected |

Definition at line 78 of file uart8250.hh.

◆ registers

|

protected |

Definition at line 207 of file uart8250.hh.

Referenced by dataAvailable(), processIntrEvent(), read(), readRbr(), serialize(), Uart8250(), unserialize(), write(), and writeThr().

◆ rlsi

|

protected |

Definition at line 57 of file uart8250.hh.

◆ rxIntrEvent

|

protected |

Definition at line 221 of file uart8250.hh.

Referenced by readRbr(), serialize(), unserialize(), and writeIer().

◆ stopBits

|

protected |

Definition at line 69 of file uart8250.hh.

◆ tbe

|

protected |

Definition at line 81 of file uart8250.hh.

◆ thri

|

protected |

Definition at line 56 of file uart8250.hh.

◆ txEmpty

|

protected |

Definition at line 82 of file uart8250.hh.

◆ txIntrEvent

|

protected |

Definition at line 220 of file uart8250.hh.

Referenced by readIir(), serialize(), Uart8250(), unserialize(), writeIer(), and writeThr().

◆ unused

|

protected |

Definition at line 83 of file uart8250.hh.

◆ wordSize

|

protected |

Definition at line 68 of file uart8250.hh.

◆ zeroes

|

protected |

Definition at line 64 of file uart8250.hh.

The documentation for this class was generated from the following files:

- dev/serial/uart8250.hh

- dev/serial/uart8250.cc

Generated on Sat Oct 18 2025 08:06:55 for gem5 by doxygen 1.14.0