#include <thread_context.hh>

Public Member Functions | |

| CortexA76TC (gem5::BaseCPU *cpu, int id, System *system, gem5::BaseMMU *mmu, gem5::BaseISA *isa, iris::IrisConnectionInterface *iris_if, const std::string &iris_path) | |

| bool | translateAddress (Addr &paddr, Addr vaddr) override |

| void | initFromIrisInstance (const ResourceMap &resources) override |

| RegVal | readIntRegFlat (RegIndex idx) const override |

| void | setIntRegFlat (RegIndex idx, RegVal val) override |

| RegVal | readCCRegFlat (RegIndex idx) const override |

| void | setCCRegFlat (RegIndex idx, RegVal val) override |

| const std::vector< iris::MemorySpaceId > & | getBpSpaceIds () const override |

| Public Member Functions inherited from gem5::Iris::ThreadContext | |

| ThreadContext (gem5::BaseCPU *cpu, int id, System *system, gem5::BaseMMU *mmu, gem5::BaseISA *isa, iris::IrisConnectionInterface *iris_if, const std::string &iris_path) | |

| virtual | ~ThreadContext () |

| bool | schedule (PCEvent *e) override |

| bool | remove (PCEvent *e) override |

| void | scheduleInstCountEvent (Event *event, Tick count) override |

| void | descheduleInstCountEvent (Event *event) override |

| Tick | getCurrentInstCount () override |

| gem5::BaseCPU * | getCpuPtr () override |

| int | cpuId () const override |

| uint32_t | socketId () const override |

| int | threadId () const override |

| void | setThreadId (int id) override |

| int | contextId () const override |

| void | setContextId (int id) override |

| BaseMMU * | getMMUPtr () override |

| CheckerCPU * | getCheckerCpuPtr () override |

| InstDecoder * | getDecoderPtr () override |

| System * | getSystemPtr () override |

| BaseISA * | getIsaPtr () const override |

| void | sendFunctional (PacketPtr pkt) override |

| Process * | getProcessPtr () override |

| void | setProcessPtr (Process *p) override |

| Status | status () const override |

| void | setStatus (Status new_status) override |

| void | activate () override |

| Set the status to Active. | |

| void | suspend () override |

| Set the status to Suspended. | |

| void | halt () override |

| Set the status to Halted. | |

| void | takeOverFrom (gem5::ThreadContext *old_context) override |

| void | regStats (const std::string &name) override |

| Tick | readLastActivate () override |

| Tick | readLastSuspend () override |

| void | copyArchRegs (gem5::ThreadContext *tc) override |

| void | clearArchRegs () override |

| RegVal | getReg (const RegId ®) const override |

| void | getReg (const RegId ®, void *val) const override |

| void * | getWritableReg (const RegId ®) override |

| void | setReg (const RegId ®, RegVal val) override |

| void | setReg (const RegId ®, const void *val) override |

| iris::ResourceId | getIntRegRscId (RegIndex int_reg) const |

| virtual RegVal | readIntReg (RegIndex reg_idx) const |

| iris::ResourceId | getVecRegRscId (RegIndex vec_reg) const |

| virtual const ArmISA::VecRegContainer & | readVecReg (const RegId ®) const |

| virtual ArmISA::VecRegContainer & | getWritableVecReg (const RegId ®) |

| virtual RegVal | readVecElem (const RegId ®) const |

| iris::ResourceId | getVecPredRegRscId (RegIndex vec_reg) const |

| virtual const ArmISA::VecPredRegContainer & | readVecPredReg (const RegId ®) const |

| virtual ArmISA::VecPredRegContainer & | getWritableVecPredReg (const RegId ®) |

| virtual RegVal | readCCReg (RegIndex reg_idx) const |

| virtual void | setIntReg (RegIndex reg_idx, RegVal val) |

| virtual void | setVecReg (const RegId ®, const ArmISA::VecRegContainer &val) |

| virtual void | setVecElem (const RegId ®, RegVal val) |

| virtual void | setVecPredReg (const RegId ®, const ArmISA::VecPredRegContainer &val) |

| virtual void | setCCReg (RegIndex reg_idx, RegVal val) |

| void | pcStateNoRecord (const PCStateBase &val) override |

| const PCStateBase & | pcState () const override |

| void | pcState (const PCStateBase &val) override |

| iris::ResourceId | getMiscRegRscId (RegIndex misc_reg) const |

| RegVal | readMiscRegNoEffect (RegIndex misc_reg) const override |

| RegVal | readMiscReg (RegIndex misc_reg) override |

| void | setMiscRegNoEffect (RegIndex misc_reg, const RegVal val) override |

| void | setMiscReg (RegIndex misc_reg, const RegVal val) override |

| unsigned | readStCondFailures () const override |

| void | setStCondFailures (unsigned sc_failures) override |

| void | htmAbortTransaction (uint64_t htm_uid, HtmFailureFaultCause cause) override |

| BaseHTMCheckpointPtr & | getHtmCheckpointPtr () override |

| void | setHtmCheckpointPtr (BaseHTMCheckpointPtr cpt) override |

| void | readMemWithCurrentMsn (Addr vaddr, size_t size, char *data) |

| void | writeMemWithCurrentMsn (Addr vaddr, size_t size, const char *data) |

| iris::ResourceId | getIntRegFlatRscId (RegIndex int_reg) const |

| Flat register interfaces. | |

| virtual const ArmISA::VecRegContainer & | readVecRegFlat (RegIndex idx) const |

| virtual ArmISA::VecRegContainer & | getWritableVecRegFlat (RegIndex idx) |

| virtual void | setVecRegFlat (RegIndex idx, const ArmISA::VecRegContainer &val) |

| virtual RegVal | readVecElemFlat (RegIndex idx) const |

| virtual void | setVecElemFlat (RegIndex idx, RegVal val) |

| virtual ArmISA::VecPredRegContainer | readVecPredRegFlat (RegIndex idx) const |

| virtual ArmISA::VecPredRegContainer & | getWritableVecPredRegFlat (RegIndex idx) |

| virtual void | setVecPredRegFlat (RegIndex idx, const ArmISA::VecPredRegContainer &val) |

| iris::ResourceId | getCCRegFlatRscId (RegIndex cc_reg) const |

| Public Member Functions inherited from gem5::ThreadContext | |

| bool | getUseForClone () |

| void | setUseForClone (bool new_val) |

| void | quiesce () |

| Quiesce thread context. | |

| void | quiesceTick (Tick resume) |

| Quiesce, suspend, and schedule activate at resume. | |

| void | pcState (Addr addr) |

| virtual int | exit () |

Static Protected Attributes | |

| static IdxNameMap | miscRegIdxNameMap |

| static IdxNameMap | intReg32IdxNameMap |

| static IdxNameMap | intReg64IdxNameMap |

| static IdxNameMap | flattenedIntIdxNameMap |

| static IdxNameMap | ccRegIdxNameMap |

| static IdxNameMap | vecRegIdxNameMap |

| static std::vector< iris::MemorySpaceId > | bpSpaceIds |

Additional Inherited Members | |

| Public Types inherited from gem5::Iris::ThreadContext | |

| typedef std::map< std::string, iris::ResourceInfo > | ResourceMap |

| typedef std::vector< iris::ResourceId > | ResourceIds |

| typedef std::map< int, std::string > | IdxNameMap |

| typedef std::unordered_map< Iris::CanonicalMsn, iris::MemorySpaceId > | MemorySpaceMap |

| Public Types inherited from gem5::ThreadContext | |

| enum | Status { Active , Suspended , Halting , Halted } |

| Static Public Member Functions inherited from gem5::ThreadContext | |

| static void | compare (ThreadContext *one, ThreadContext *two) |

| function to compare two thread contexts (for debugging) | |

| Public Attributes inherited from gem5::ThreadContext | |

| int | intResult = DefaultIntResult |

| double | floatResult = DefaultFloatResult |

| int | intOffset = 0 |

| Static Public Attributes inherited from gem5::ThreadContext | |

| static const int | ints [] |

| static const double | floats [] |

| static const int | DefaultIntResult = 0 |

| static const double | DefaultFloatResult = 0.0 |

| Protected Types inherited from gem5::Iris::ThreadContext | |

| using | BpId = uint64_t |

| using | BpInfoPtr = std::unique_ptr<BpInfo> |

| using | BpInfoMap = std::map<Addr, BpInfoPtr> |

| using | BpInfoIt = BpInfoMap::iterator |

| Protected Member Functions inherited from gem5::Iris::ThreadContext | |

| iris::ResourceId | extractResourceId (const ResourceMap &resources, const std::string &name) |

| void | extractResourceMap (ResourceIds &ids, const ResourceMap &resources, const IdxNameMap &idx_names) |

| iris::MemorySpaceId | getMemorySpaceId (const Iris::CanonicalMsn &msn) const |

| void | maintainStepping () |

| BpInfoIt | getOrAllocBp (Addr pc) |

| void | installBp (BpInfoIt it) |

| void | uninstallBp (BpInfoIt it) |

| void | delBp (BpInfoIt it) |

| iris::IrisErrorCode | instanceRegistryChanged (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | phaseInitLeave (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | simulationTimeEvent (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | breakpointHit (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | semihostingEvent (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisCppAdapter & | call () const |

| iris::IrisCppAdapter & | noThrow () const |

| void | readMem (iris::MemorySpaceId space, Addr addr, void *p, size_t size) |

| void | writeMem (iris::MemorySpaceId space, Addr addr, const void *p, size_t size) |

| bool | translateAddress (Addr &paddr, iris::MemorySpaceId p_space, Addr vaddr, iris::MemorySpaceId v_space) |

| Protected Attributes inherited from gem5::Iris::ThreadContext | |

| gem5::BaseCPU * | _cpu |

| int | _threadId |

| ContextID | _contextId |

| System * | _system |

| gem5::BaseMMU * | _mmu |

| gem5::BaseISA * | _isa |

| std::string | _irisPath |

| iris::InstanceId | _instId = iris::IRIS_UINT64_MAX |

| std::vector< ArmISA::VecRegContainer > | vecRegs |

| std::vector< ArmISA::VecPredRegContainer > | vecPredRegs |

| Status | _status = Active |

| Event * | enableAfterPseudoEvent |

| ResourceIds | miscRegIds |

| ResourceIds | intReg32Ids |

| ResourceIds | intReg64Ids |

| ResourceIds | flattenedIntIds |

| ResourceIds | ccRegIds |

| iris::ResourceId | pcRscId = iris::IRIS_UINT64_MAX |

| iris::ResourceId | icountRscId |

| ResourceIds | vecRegIds |

| ResourceIds | vecPredRegIds |

| std::vector< iris::MemorySpaceInfo > | memorySpaces |

| std::vector< iris::MemorySupportedAddressTranslationResult > | translations |

| MemorySpaceMap | memorySpaceIds |

| EventQueue | comInstEventQueue |

| BpInfoMap | bps |

| std::optional< Addr > | bpAddr |

| iris::EventStreamId | regEventStreamId |

| iris::EventStreamId | initEventStreamId |

| iris::EventStreamId | timeEventStreamId |

| iris::EventStreamId | breakpointEventStreamId |

| iris::EventStreamId | semihostingEventStreamId |

| iris::IrisInstance | client |

| ArmISA::PCState | pc |

| Protected Attributes inherited from gem5::ThreadContext | |

| bool | useForClone = false |

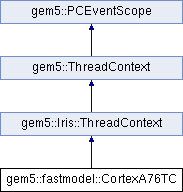

Detailed Description

Definition at line 41 of file thread_context.hh.

Constructor & Destructor Documentation

◆ CortexA76TC()

| gem5::fastmodel::CortexA76TC::CortexA76TC | ( | gem5::BaseCPU * | cpu, |

| int | id, | ||

| System * | system, | ||

| gem5::BaseMMU * | mmu, | ||

| gem5::BaseISA * | isa, | ||

| iris::IrisConnectionInterface * | iris_if, | ||

| const std::string & | iris_path ) |

Definition at line 41 of file thread_context.cc.

References gem5::ArmISA::id, gem5::X86ISA::system, and gem5::Iris::ThreadContext::ThreadContext().

Referenced by readIntRegFlat().

Member Function Documentation

◆ getBpSpaceIds()

|

overridevirtual |

Implements gem5::Iris::ThreadContext.

Definition at line 180 of file thread_context.cc.

References bpSpaceIds, gem5::Iris::ThreadContext::getMemorySpaceId(), gem5::Iris::GuestMsn, gem5::Iris::HypAppMsn, gem5::Iris::NsHypMsn, panic_if, and gem5::Iris::SecureMonitorMsn.

◆ initFromIrisInstance()

|

overridevirtual |

Reimplemented from gem5::Iris::ThreadContext.

Definition at line 79 of file thread_context.cc.

References gem5::Iris::ThreadContext::ccRegIds, ccRegIdxNameMap, gem5::Iris::ThreadContext::extractResourceId(), gem5::Iris::ThreadContext::extractResourceMap(), gem5::Iris::ThreadContext::flattenedIntIds, flattenedIntIdxNameMap, gem5::Iris::ThreadContext::intReg32Ids, intReg32IdxNameMap, gem5::Iris::ThreadContext::intReg64Ids, intReg64IdxNameMap, gem5::Iris::ThreadContext::miscRegIds, miscRegIdxNameMap, gem5::Iris::ThreadContext::pcRscId, gem5::Iris::ThreadContext::vecRegIds, and vecRegIdxNameMap.

◆ readCCRegFlat()

Reimplemented from gem5::Iris::ThreadContext.

Definition at line 140 of file thread_context.cc.

References gem5::bits(), gem5::ArmISA::cc_reg::Fp, gem5::ArmISA::cc_reg::Nz, gem5::ArmISA::nz, and gem5::Iris::ThreadContext::readCCRegFlat().

◆ readIntRegFlat()

Reimplemented from gem5::Iris::ThreadContext.

Definition at line 98 of file thread_context.cc.

References CortexA76TC(), gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MODE_MON, gem5::ArmISA::int_reg::R13Mon, gem5::ArmISA::int_reg::R14Mon, gem5::Iris::ThreadContext::readMiscRegNoEffect(), and gem5::X86ISA::val.

◆ setCCRegFlat()

Reimplemented from gem5::Iris::ThreadContext.

Definition at line 157 of file thread_context.cc.

References gem5::ArmISA::cc_reg::Fp, gem5::insertBits(), gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MISCREG_FPSCR, gem5::ArmISA::cc_reg::Nz, gem5::Iris::ThreadContext::readMiscRegNoEffect(), gem5::Iris::ThreadContext::setCCRegFlat(), and gem5::X86ISA::val.

◆ setIntRegFlat()

Reimplemented from gem5::Iris::ThreadContext.

Definition at line 121 of file thread_context.cc.

References gem5::ArmISA::MISCREG_CPSR, gem5::ArmISA::MODE_MON, gem5::ArmISA::int_reg::R13Mon, gem5::ArmISA::int_reg::R14Mon, gem5::Iris::ThreadContext::readMiscRegNoEffect(), gem5::Iris::ThreadContext::setMiscReg(), and gem5::X86ISA::val.

◆ translateAddress()

Implements gem5::Iris::ThreadContext.

Definition at line 49 of file thread_context.cc.

References gem5::ArmISA::currEL(), gem5::ArmISA::EL2, gem5::ArmISA::EL3, gem5::Iris::ThreadContext::getMemorySpaceId(), gem5::Iris::GuestMsn, gem5::ArmISA::isSecure(), gem5::Iris::NsHypMsn, panic_if, gem5::Iris::PhysicalMemoryNonSecureMsn, gem5::Iris::PhysicalMemorySecureMsn, gem5::Iris::SecureMonitorMsn, and gem5::MipsISA::vaddr.

Member Data Documentation

◆ bpSpaceIds

|

staticprotected |

Definition at line 50 of file thread_context.hh.

Referenced by getBpSpaceIds().

◆ ccRegIdxNameMap

|

staticprotected |

Definition at line 48 of file thread_context.hh.

Referenced by initFromIrisInstance().

◆ flattenedIntIdxNameMap

|

staticprotected |

Definition at line 47 of file thread_context.hh.

Referenced by initFromIrisInstance().

◆ intReg32IdxNameMap

|

staticprotected |

Definition at line 45 of file thread_context.hh.

Referenced by initFromIrisInstance().

◆ intReg64IdxNameMap

|

staticprotected |

Definition at line 46 of file thread_context.hh.

Referenced by initFromIrisInstance().

◆ miscRegIdxNameMap

|

staticprotected |

Definition at line 44 of file thread_context.hh.

Referenced by initFromIrisInstance().

◆ vecRegIdxNameMap

|

staticprotected |

Definition at line 49 of file thread_context.hh.

Referenced by initFromIrisInstance().

The documentation for this class was generated from the following files:

- arch/arm/fastmodel/CortexA76/thread_context.hh

- arch/arm/fastmodel/CortexA76/thread_context.cc

Generated on Sat Oct 18 2025 08:06:58 for gem5 by doxygen 1.14.0