#include <isa.hh>

Public Types | |

| typedef std::vector< const RegClass * > | RegClasses |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| virtual PCStateBase * | newPCState (Addr new_inst_addr=0) const =0 |

| virtual void | clear () |

| virtual RegVal | readMiscRegNoEffect (RegIndex idx) const =0 |

| virtual RegVal | readMiscReg (RegIndex idx)=0 |

| virtual void | setMiscRegNoEffect (RegIndex idx, RegVal val)=0 |

| virtual void | setMiscReg (RegIndex idx, RegVal val)=0 |

| virtual void | takeOverFrom (ThreadContext *new_tc, ThreadContext *old_tc) |

| virtual void | setThreadContext (ThreadContext *_tc) |

| virtual uint64_t | getExecutingAsid () const |

| virtual bool | inUserMode () const =0 |

| virtual void | copyRegsFrom (ThreadContext *src)=0 |

| virtual void | resetThread () |

| const RegClasses & | regClasses () const |

| const std::string & | getIsaName () const |

| virtual void | handleLockedRead (const RequestPtr &req) |

| virtual void | handleLockedRead (ExecContext *xc, const RequestPtr &req) |

| virtual bool | handleLockedWrite (const RequestPtr &req, Addr cacheBlockMask) |

| virtual bool | handleLockedWrite (ExecContext *xc, const RequestPtr &req, Addr cacheBlockMask) |

| virtual void | handleLockedSnoop (PacketPtr pkt, Addr cacheBlockMask) |

| virtual void | handleLockedSnoop (ExecContext *xc, PacketPtr pkt, Addr cacheBlockMask) |

| virtual void | handleLockedSnoopHit () |

| virtual void | handleLockedSnoopHit (ExecContext *xc) |

| virtual void | globalClearExclusive () |

| virtual void | globalClearExclusive (ExecContext *xc) |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| virtual int64_t | getVectorLengthInBytes () const |

| This function returns the vector length of the Vector Length Agnostic extension of the ISA. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Protected Member Functions | |

| BaseISA (const SimObjectParams &p, const std::string &name) | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

Protected Attributes | |

| ThreadContext * | tc = nullptr |

| RegClasses | _regClasses |

| std::string | isaName |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

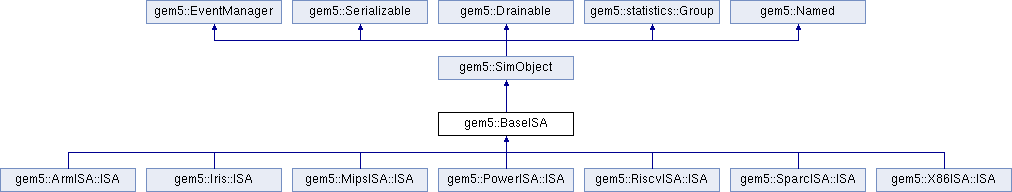

Detailed Description

Member Typedef Documentation

◆ RegClasses

| typedef std::vector<const RegClass *> gem5::BaseISA::RegClasses |

Constructor & Destructor Documentation

◆ BaseISA()

|

inlineprotected |

Definition at line 64 of file isa.hh.

References isaName, gem5::Named::name(), gem5::MipsISA::p, and gem5::SimObject::SimObject().

Referenced by gem5::ArmISA::ISA::ISA(), gem5::Iris::ISA::ISA(), gem5::MipsISA::ISA::ISA(), gem5::PowerISA::ISA::ISA(), gem5::RiscvISA::ISA::ISA(), gem5::SparcISA::ISA::ISA(), and gem5::X86ISA::ISA::ISA().

Member Function Documentation

◆ clear()

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA, gem5::MipsISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

Definition at line 76 of file isa.hh.

Referenced by gem5::PowerISA::ISA::ISA().

◆ copyRegsFrom()

|

pure virtual |

Implemented in gem5::ArmISA::ISA, gem5::MipsISA::ISA, gem5::PowerISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

Referenced by gem5::ArmLinux::archClone(), gem5::PowerLinux::archClone(), gem5::RiscvLinux32::archClone(), gem5::RiscvLinux64::archClone(), gem5::SparcLinux::archClone(), gem5::X86Linux::archClone(), gem5::o3::ThreadContext::copyArchRegs(), and gem5::SimpleThread::copyArchRegs().

◆ getExecutingAsid()

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA, and gem5::SparcISA::ISA.

◆ getIsaName()

|

inline |

◆ getVectorLengthInBytes()

|

inlinevirtual |

This function returns the vector length of the Vector Length Agnostic extension of the ISA.

For ARM ISA, this function returns the SVE/SVE2 vector length. For RISC-V ISA, this function returns the RVV vector length. For other ISAs, this function returns -1.

Reimplemented in gem5::ArmISA::ISA, and gem5::RiscvISA::ISA.

◆ globalClearExclusive() [1/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA, and gem5::RiscvISA::ISA.

Definition at line 128 of file isa.hh.

Referenced by gem5::memory::AbstractMemory::checkLockedAddrList(), globalClearExclusive(), and gem5::GenericHtmFailureFault::invoke().

◆ globalClearExclusive() [2/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA.

Definition at line 130 of file isa.hh.

References globalClearExclusive().

◆ handleLockedRead() [1/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA, and gem5::RiscvISA::ISA.

Definition at line 97 of file isa.hh.

Referenced by handleLockedRead(), gem5::TimingSimpleCPU::handleReadPacket(), gem5::AtomicSimpleCPU::readMem(), and gem5::minor::LSQ::tryToSendToTransfers().

◆ handleLockedRead() [2/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA.

Definition at line 99 of file isa.hh.

References handleLockedRead().

◆ handleLockedSnoop() [1/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA.

Definition at line 117 of file isa.hh.

References handleLockedSnoop().

◆ handleLockedSnoop() [2/2]

Reimplemented in gem5::ArmISA::ISA, and gem5::RiscvISA::ISA.

Definition at line 115 of file isa.hh.

Referenced by gem5::o3::LSQUnit::checkSnoop(), and handleLockedSnoop().

◆ handleLockedSnoopHit() [1/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA.

Definition at line 121 of file isa.hh.

Referenced by handleLockedSnoopHit().

◆ handleLockedSnoopHit() [2/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA.

Definition at line 123 of file isa.hh.

References handleLockedSnoopHit().

◆ handleLockedWrite() [1/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA, and gem5::RiscvISA::ISA.

Definition at line 104 of file isa.hh.

Referenced by handleLockedWrite(), gem5::TimingSimpleCPU::sendData(), gem5::minor::LSQ::tryToSendToTransfers(), and gem5::AtomicSimpleCPU::writeMem().

◆ handleLockedWrite() [2/2]

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA.

Definition at line 109 of file isa.hh.

References handleLockedWrite().

◆ inUserMode()

|

pure virtual |

Implemented in gem5::ArmISA::ISA, gem5::Iris::ISA, gem5::MipsISA::ISA, gem5::PowerISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

Referenced by gem5::LooppointAnalysis::checkPc().

◆ newPCState()

|

pure virtual |

Implemented in gem5::ArmISA::ISA, gem5::Iris::ISA, gem5::MipsISA::ISA, gem5::PowerISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

Referenced by gem5::RiscvISA::Reset::invoke().

◆ readMiscReg()

Implemented in gem5::ArmISA::ISA, gem5::Iris::ISA, gem5::MipsISA::ISA, gem5::PowerISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

◆ readMiscRegNoEffect()

Implemented in gem5::ArmISA::ISA, gem5::Iris::ISA, gem5::MipsISA::ISA, gem5::PowerISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

◆ regClasses()

|

inline |

Definition at line 93 of file isa.hh.

References _regClasses.

Referenced by gem5::serialize(), gem5::SimpleThread::SimpleThread(), and gem5::unserialize().

◆ resetThread()

|

inlinevirtual |

◆ serialize()

|

inlineoverridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Reimplemented in gem5::ArmISA::ISA, gem5::Iris::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

Definition at line 136 of file isa.hh.

References isaName, and SERIALIZE_SCALAR.

Referenced by gem5::ArmISA::ISA::serialize(), gem5::RiscvISA::ISA::serialize(), gem5::SparcISA::ISA::serialize(), and gem5::X86ISA::ISA::serialize().

◆ setMiscReg()

Implemented in gem5::ArmISA::ISA, gem5::Iris::ISA, gem5::MipsISA::ISA, gem5::PowerISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

References gem5::X86ISA::val.

◆ setMiscRegNoEffect()

Implemented in gem5::ArmISA::ISA, gem5::Iris::ISA, gem5::MipsISA::ISA, gem5::PowerISA::ISA, gem5::RiscvISA::ISA, gem5::SparcISA::ISA, and gem5::X86ISA::ISA.

References gem5::X86ISA::val.

◆ setThreadContext()

|

inlinevirtual |

Reimplemented in gem5::X86ISA::ISA.

Definition at line 85 of file isa.hh.

References tc.

Referenced by gem5::BaseCPU::registerThreadContexts(), gem5::X86ISA::ISA::setThreadContext(), and gem5::BaseCPU::takeOverFrom().

◆ takeOverFrom()

|

inlinevirtual |

Reimplemented in gem5::ArmISA::ISA.

Definition at line 84 of file isa.hh.

Referenced by gem5::o3::ThreadContext::takeOverFrom().

Member Data Documentation

◆ _regClasses

|

protected |

Definition at line 70 of file isa.hh.

Referenced by gem5::ArmISA::ISA::ISA(), gem5::MipsISA::ISA::ISA(), gem5::PowerISA::ISA::ISA(), gem5::RiscvISA::ISA::ISA(), gem5::SparcISA::ISA::ISA(), gem5::X86ISA::ISA::ISA(), and regClasses().

◆ isaName

|

protected |

Definition at line 72 of file isa.hh.

Referenced by BaseISA(), getIsaName(), and serialize().

◆ tc

|

protected |

Definition at line 68 of file isa.hh.

Referenced by gem5::ArmISA::ISA::addressTranslation(), gem5::SparcISA::ISA::checkSoftInt(), gem5::ArmISA::ISA::clear(), gem5::ArmISA::ISA::copyRegsFrom(), gem5::MipsISA::ISA::copyRegsFrom(), gem5::PowerISA::ISA::copyRegsFrom(), gem5::RiscvISA::ISA::copyRegsFrom(), gem5::SparcISA::ISA::copyRegsFrom(), gem5::X86ISA::ISA::copyRegsFrom(), gem5::ArmISA::ISA::getCurSmeVecLenInBits(), gem5::ArmISA::ISA::getCurSveVecLenInBits(), gem5::RiscvISA::ISA::getFaultHandlerAddr(), gem5::ArmISA::ISA::getGenericTimer(), gem5::ArmISA::ISA::getGICv3CPUInterface(), gem5::ArmISA::ISA::getGICv3CPUInterface(), gem5::ArmISA::ISA::getSelfDebug(), gem5::ArmISA::ISA::globalClearExclusive(), gem5::RiscvISA::ISA::globalClearExclusive(), gem5::ArmISA::ISA::handleLockedRead(), gem5::RiscvISA::ISA::handleLockedRead(), gem5::ArmISA::ISA::handleLockedSnoop(), gem5::RiscvISA::ISA::handleLockedSnoop(), gem5::ArmISA::ISA::handleLockedSnoopHit(), gem5::ArmISA::ISA::handleLockedWrite(), gem5::RiscvISA::ISA::handleLockedWrite(), gem5::Iris::ISA::inUserMode(), gem5::SparcISA::ISA::processHSTickCompare(), gem5::SparcISA::ISA::processSTickCompare(), gem5::SparcISA::ISA::readFSReg(), gem5::ArmISA::ISA::readMiscReg(), gem5::RiscvISA::ISA::readMiscReg(), gem5::SparcISA::ISA::readMiscReg(), gem5::X86ISA::ISA::readMiscReg(), gem5::ArmISA::ISA::redirectRegVHE(), gem5::RiscvISA::ISA::resetThread(), gem5::Iris::ISA::serialize(), gem5::SparcISA::ISA::setFSReg(), gem5::ArmISA::ISA::setMiscReg(), gem5::MipsISA::ISA::setMiscReg(), gem5::RiscvISA::ISA::setMiscReg(), gem5::SparcISA::ISA::setMiscReg(), gem5::X86ISA::ISA::setMiscReg(), setThreadContext(), gem5::X86ISA::ISA::setThreadContext(), gem5::ArmISA::ISA::setupThreadContext(), gem5::ArmISA::ISA::startup(), gem5::ArmISA::ISA::takeOverFrom(), and gem5::X86ISA::ISA::updateHandyM5Reg().

The documentation for this class was generated from the following file:

- arch/generic/isa.hh

Generated on Sat Oct 18 2025 08:06:49 for gem5 by doxygen 1.14.0