#include <thread_context.hh>

Classes | |

| struct | BpInfo |

Public Types | |

| typedef std::map< std::string, iris::ResourceInfo > | ResourceMap |

| typedef std::vector< iris::ResourceId > | ResourceIds |

| typedef std::map< int, std::string > | IdxNameMap |

| typedef std::unordered_map< Iris::CanonicalMsn, iris::MemorySpaceId > | MemorySpaceMap |

| Public Types inherited from gem5::ThreadContext | |

| enum | Status { Active , Suspended , Halting , Halted } |

Public Member Functions | |

| ThreadContext (gem5::BaseCPU *cpu, int id, System *system, gem5::BaseMMU *mmu, gem5::BaseISA *isa, iris::IrisConnectionInterface *iris_if, const std::string &iris_path) | |

| virtual | ~ThreadContext () |

| virtual bool | translateAddress (Addr &paddr, Addr vaddr)=0 |

| bool | schedule (PCEvent *e) override |

| bool | remove (PCEvent *e) override |

| void | scheduleInstCountEvent (Event *event, Tick count) override |

| void | descheduleInstCountEvent (Event *event) override |

| Tick | getCurrentInstCount () override |

| gem5::BaseCPU * | getCpuPtr () override |

| int | cpuId () const override |

| uint32_t | socketId () const override |

| int | threadId () const override |

| void | setThreadId (int id) override |

| int | contextId () const override |

| void | setContextId (int id) override |

| BaseMMU * | getMMUPtr () override |

| CheckerCPU * | getCheckerCpuPtr () override |

| InstDecoder * | getDecoderPtr () override |

| System * | getSystemPtr () override |

| BaseISA * | getIsaPtr () const override |

| void | sendFunctional (PacketPtr pkt) override |

| Process * | getProcessPtr () override |

| void | setProcessPtr (Process *p) override |

| Status | status () const override |

| void | setStatus (Status new_status) override |

| void | activate () override |

| Set the status to Active. | |

| void | suspend () override |

| Set the status to Suspended. | |

| void | halt () override |

| Set the status to Halted. | |

| void | takeOverFrom (gem5::ThreadContext *old_context) override |

| void | regStats (const std::string &name) override |

| Tick | readLastActivate () override |

| Tick | readLastSuspend () override |

| void | copyArchRegs (gem5::ThreadContext *tc) override |

| void | clearArchRegs () override |

| RegVal | getReg (const RegId ®) const override |

| void | getReg (const RegId ®, void *val) const override |

| void * | getWritableReg (const RegId ®) override |

| void | setReg (const RegId ®, RegVal val) override |

| void | setReg (const RegId ®, const void *val) override |

| iris::ResourceId | getIntRegRscId (RegIndex int_reg) const |

| virtual RegVal | readIntReg (RegIndex reg_idx) const |

| iris::ResourceId | getVecRegRscId (RegIndex vec_reg) const |

| virtual const ArmISA::VecRegContainer & | readVecReg (const RegId ®) const |

| virtual ArmISA::VecRegContainer & | getWritableVecReg (const RegId ®) |

| virtual RegVal | readVecElem (const RegId ®) const |

| iris::ResourceId | getVecPredRegRscId (RegIndex vec_reg) const |

| virtual const ArmISA::VecPredRegContainer & | readVecPredReg (const RegId ®) const |

| virtual ArmISA::VecPredRegContainer & | getWritableVecPredReg (const RegId ®) |

| virtual RegVal | readCCReg (RegIndex reg_idx) const |

| virtual void | setIntReg (RegIndex reg_idx, RegVal val) |

| virtual void | setVecReg (const RegId ®, const ArmISA::VecRegContainer &val) |

| virtual void | setVecElem (const RegId ®, RegVal val) |

| virtual void | setVecPredReg (const RegId ®, const ArmISA::VecPredRegContainer &val) |

| virtual void | setCCReg (RegIndex reg_idx, RegVal val) |

| void | pcStateNoRecord (const PCStateBase &val) override |

| const PCStateBase & | pcState () const override |

| void | pcState (const PCStateBase &val) override |

| iris::ResourceId | getMiscRegRscId (RegIndex misc_reg) const |

| RegVal | readMiscRegNoEffect (RegIndex misc_reg) const override |

| RegVal | readMiscReg (RegIndex misc_reg) override |

| void | setMiscRegNoEffect (RegIndex misc_reg, const RegVal val) override |

| void | setMiscReg (RegIndex misc_reg, const RegVal val) override |

| unsigned | readStCondFailures () const override |

| void | setStCondFailures (unsigned sc_failures) override |

| void | htmAbortTransaction (uint64_t htm_uid, HtmFailureFaultCause cause) override |

| BaseHTMCheckpointPtr & | getHtmCheckpointPtr () override |

| void | setHtmCheckpointPtr (BaseHTMCheckpointPtr cpt) override |

| void | readMemWithCurrentMsn (Addr vaddr, size_t size, char *data) |

| void | writeMemWithCurrentMsn (Addr vaddr, size_t size, const char *data) |

| iris::ResourceId | getIntRegFlatRscId (RegIndex int_reg) const |

| Flat register interfaces. | |

| virtual RegVal | readIntRegFlat (RegIndex idx) const |

| virtual void | setIntRegFlat (RegIndex idx, uint64_t val) |

| virtual const ArmISA::VecRegContainer & | readVecRegFlat (RegIndex idx) const |

| virtual ArmISA::VecRegContainer & | getWritableVecRegFlat (RegIndex idx) |

| virtual void | setVecRegFlat (RegIndex idx, const ArmISA::VecRegContainer &val) |

| virtual RegVal | readVecElemFlat (RegIndex idx) const |

| virtual void | setVecElemFlat (RegIndex idx, RegVal val) |

| virtual ArmISA::VecPredRegContainer | readVecPredRegFlat (RegIndex idx) const |

| virtual ArmISA::VecPredRegContainer & | getWritableVecPredRegFlat (RegIndex idx) |

| virtual void | setVecPredRegFlat (RegIndex idx, const ArmISA::VecPredRegContainer &val) |

| iris::ResourceId | getCCRegFlatRscId (RegIndex cc_reg) const |

| virtual RegVal | readCCRegFlat (RegIndex idx) const |

| virtual void | setCCRegFlat (RegIndex idx, RegVal val) |

| Public Member Functions inherited from gem5::ThreadContext | |

| bool | getUseForClone () |

| void | setUseForClone (bool new_val) |

| void | quiesce () |

| Quiesce thread context. | |

| void | quiesceTick (Tick resume) |

| Quiesce, suspend, and schedule activate at resume. | |

| void | pcState (Addr addr) |

| virtual int | exit () |

Protected Types | |

| using | BpId = uint64_t |

| using | BpInfoPtr = std::unique_ptr<BpInfo> |

| using | BpInfoMap = std::map<Addr, BpInfoPtr> |

| using | BpInfoIt = BpInfoMap::iterator |

Protected Member Functions | |

| virtual void | initFromIrisInstance (const ResourceMap &resources) |

| iris::ResourceId | extractResourceId (const ResourceMap &resources, const std::string &name) |

| void | extractResourceMap (ResourceIds &ids, const ResourceMap &resources, const IdxNameMap &idx_names) |

| iris::MemorySpaceId | getMemorySpaceId (const Iris::CanonicalMsn &msn) const |

| void | maintainStepping () |

| BpInfoIt | getOrAllocBp (Addr pc) |

| void | installBp (BpInfoIt it) |

| void | uninstallBp (BpInfoIt it) |

| void | delBp (BpInfoIt it) |

| virtual const std::vector< iris::MemorySpaceId > & | getBpSpaceIds () const =0 |

| iris::IrisErrorCode | instanceRegistryChanged (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | phaseInitLeave (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | simulationTimeEvent (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | breakpointHit (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisErrorCode | semihostingEvent (uint64_t esId, const iris::IrisValueMap &fields, uint64_t time, uint64_t sInstId, bool syncEc, std::string &error_message_out) |

| iris::IrisCppAdapter & | call () const |

| iris::IrisCppAdapter & | noThrow () const |

| void | readMem (iris::MemorySpaceId space, Addr addr, void *p, size_t size) |

| void | writeMem (iris::MemorySpaceId space, Addr addr, const void *p, size_t size) |

| bool | translateAddress (Addr &paddr, iris::MemorySpaceId p_space, Addr vaddr, iris::MemorySpaceId v_space) |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::ThreadContext | |

| static void | compare (ThreadContext *one, ThreadContext *two) |

| function to compare two thread contexts (for debugging) | |

| Public Attributes inherited from gem5::ThreadContext | |

| int | intResult = DefaultIntResult |

| double | floatResult = DefaultFloatResult |

| int | intOffset = 0 |

| Static Public Attributes inherited from gem5::ThreadContext | |

| static const int | ints [] |

| static const double | floats [] |

| static const int | DefaultIntResult = 0 |

| static const double | DefaultFloatResult = 0.0 |

Detailed Description

Definition at line 54 of file thread_context.hh.

Member Typedef Documentation

◆ BpId

|

protected |

Definition at line 117 of file thread_context.hh.

◆ BpInfoIt

|

protected |

Definition at line 134 of file thread_context.hh.

◆ BpInfoMap

|

protected |

Definition at line 133 of file thread_context.hh.

◆ BpInfoPtr

|

protected |

Definition at line 132 of file thread_context.hh.

◆ IdxNameMap

| typedef std::map<int, std::string> gem5::Iris::ThreadContext::IdxNameMap |

Definition at line 60 of file thread_context.hh.

◆ MemorySpaceMap

| typedef std::unordered_map<Iris::CanonicalMsn, iris::MemorySpaceId> gem5::Iris::ThreadContext::MemorySpaceMap |

Definition at line 63 of file thread_context.hh.

◆ ResourceIds

| typedef std::vector<iris::ResourceId> gem5::Iris::ThreadContext::ResourceIds |

Definition at line 59 of file thread_context.hh.

◆ ResourceMap

| typedef std::map<std::string, iris::ResourceInfo> gem5::Iris::ThreadContext::ResourceMap |

Definition at line 57 of file thread_context.hh.

Constructor & Destructor Documentation

◆ ThreadContext()

| gem5::Iris::ThreadContext::ThreadContext | ( | gem5::BaseCPU * | cpu, |

| int | id, | ||

| System * | system, | ||

| gem5::BaseMMU * | mmu, | ||

| gem5::BaseISA * | isa, | ||

| iris::IrisConnectionInterface * | iris_if, | ||

| const std::string & | iris_path ) |

Definition at line 334 of file thread_context.cc.

References _cpu, _instId, _irisPath, _isa, _mmu, _system, _threadId, breakpointEventStreamId, call(), client, comInstEventQueue, enableAfterPseudoEvent, gem5::ArmISA::id, initEventStreamId, noThrow(), gem5::ArmISA::NumVecPredRegs, gem5::ArmISA::NumVecRegs, regEventStreamId, semihostingEventStreamId, gem5::EventBase::Sim_Exit_Pri, gem5::X86ISA::system, ThreadContext(), timeEventStreamId, vecPredRegs, and vecRegs.

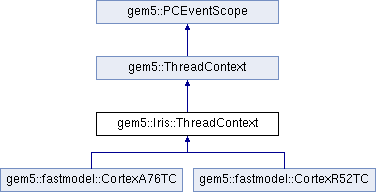

Referenced by gem5::fastmodel::CortexA76TC::CortexA76TC(), gem5::fastmodel::CortexR52TC::CortexR52TC(), initFromIrisInstance(), and ThreadContext().

◆ ~ThreadContext()

|

virtual |

Reimplemented from gem5::ThreadContext.

Definition at line 401 of file thread_context.cc.

References call(), client, gem5::EventManager::deschedule(), enableAfterPseudoEvent, getCpuPtr(), initEventStreamId, regEventStreamId, and timeEventStreamId.

Member Function Documentation

◆ activate()

|

inlineoverridevirtual |

Set the status to Active.

Implements gem5::ThreadContext.

Definition at line 245 of file thread_context.hh.

References gem5::ThreadContext::Active, and setStatus().

◆ breakpointHit()

|

protected |

Definition at line 301 of file thread_context.cc.

◆ call()

|

inlineprotected |

Definition at line 171 of file thread_context.hh.

References client.

Referenced by getCurrentInstCount(), initFromIrisInstance(), installBp(), maintainStepping(), pcState(), pcState(), phaseInitLeave(), readCCRegFlat(), gem5::fastmodel::CortexR52TC::readIntReg(), readIntReg(), readIntRegFlat(), readMem(), readMiscRegNoEffect(), readVecPredReg(), readVecReg(), scheduleInstCountEvent(), semihostingEvent(), setCCRegFlat(), gem5::fastmodel::CortexR52TC::setIntReg(), setIntReg(), setIntRegFlat(), setMiscRegNoEffect(), setStatus(), simulationTimeEvent(), ThreadContext(), uninstallBp(), writeMem(), and ~ThreadContext().

◆ clearArchRegs()

|

inlineoverridevirtual |

◆ contextId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 206 of file thread_context.hh.

References _contextId.

◆ copyArchRegs()

|

inlineoverridevirtual |

◆ cpuId()

|

inlineoverridevirtual |

◆ delBp()

|

protected |

Definition at line 199 of file thread_context.cc.

References bps, panic_if, and uninstallBp().

Referenced by remove().

◆ descheduleInstCountEvent()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 510 of file thread_context.cc.

References comInstEventQueue, gem5::MipsISA::event, and maintainStepping().

◆ extractResourceId()

|

protected |

Definition at line 107 of file thread_context.cc.

References name().

Referenced by extractResourceMap(), gem5::fastmodel::CortexA76TC::initFromIrisInstance(), and gem5::fastmodel::CortexR52TC::initFromIrisInstance().

◆ extractResourceMap()

|

protected |

Definition at line 114 of file thread_context.cc.

References extractResourceId(), gem5::ArmISA::ids, and name().

Referenced by gem5::fastmodel::CortexA76TC::initFromIrisInstance(), and gem5::fastmodel::CortexR52TC::initFromIrisInstance().

◆ getBpSpaceIds()

|

protectedpure virtual |

Implemented in gem5::fastmodel::CortexA76TC, and gem5::fastmodel::CortexR52TC.

Referenced by installBp().

◆ getCCRegFlatRscId()

| iris::ResourceId gem5::Iris::ThreadContext::getCCRegFlatRscId | ( | RegIndex | cc_reg | ) | const |

Definition at line 853 of file thread_context.cc.

References ccRegIds.

Referenced by readCCRegFlat(), and setCCRegFlat().

◆ getCheckerCpuPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 215 of file thread_context.hh.

◆ getCpuPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 199 of file thread_context.hh.

References _cpu.

Referenced by semihostingEvent(), setStatus(), and ~ThreadContext().

◆ getCurrentInstCount()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 517 of file thread_context.cc.

References _instId, call(), gem5::X86ISA::count, and panic_if.

Referenced by maintainStepping(), and scheduleInstCountEvent().

◆ getDecoderPtr()

|

inlineoverridevirtual |

◆ getHtmCheckpointPtr()

|

inlineoverridevirtual |

◆ getIntRegFlatRscId()

| iris::ResourceId gem5::Iris::ThreadContext::getIntRegFlatRscId | ( | RegIndex | int_reg | ) | const |

Flat register interfaces.

Some architectures have different registers visible in different modes. Such architectures "flatten" a register (see flattenRegId()) to map it into the gem5 register file. This interface provides a flat interface to the underlying register file, which allows for example serialization code to access all registers.

Definition at line 818 of file thread_context.cc.

References flattenedIntIds.

Referenced by readIntRegFlat(), and setIntRegFlat().

◆ getIntRegRscId()

| iris::ResourceId gem5::Iris::ThreadContext::getIntRegRscId | ( | RegIndex | int_reg | ) | const |

Definition at line 788 of file thread_context.cc.

References intReg32Ids, intReg64Ids, gem5::ArmISA::intRegClass, gem5::ArmISA::MISCREG_CPSR, panic_if, and readMiscRegNoEffect().

Referenced by readIntReg(), and setIntReg().

◆ getIsaPtr()

|

inlineoverridevirtual |

◆ getMemorySpaceId()

|

protected |

Definition at line 130 of file thread_context.cc.

References memorySpaceIds.

Referenced by gem5::fastmodel::CortexA76TC::getBpSpaceIds(), gem5::fastmodel::CortexR52TC::getBpSpaceIds(), readMemWithCurrentMsn(), gem5::fastmodel::CortexR52TC::sendFunctional(), sendFunctional(), gem5::fastmodel::CortexA76TC::translateAddress(), and writeMemWithCurrentMsn().

◆ getMiscRegRscId()

| iris::ResourceId gem5::Iris::ThreadContext::getMiscRegRscId | ( | RegIndex | misc_reg | ) | const |

Definition at line 613 of file thread_context.cc.

References gem5::ArmISA::miscRegClass, miscRegIds, and panic_if.

Referenced by readMiscRegNoEffect(), and setMiscRegNoEffect().

◆ getMMUPtr()

|

inlineoverridevirtual |

◆ getOrAllocBp()

|

protected |

Definition at line 166 of file thread_context.cc.

References bps, panic_if, and pc.

Referenced by remove(), schedule(), and simulationTimeEvent().

◆ getProcessPtr()

|

inlineoverridevirtual |

◆ getReg() [1/2]

Reimplemented from gem5::ThreadContext.

Definition at line 641 of file thread_context.cc.

References getReg(), gem5::X86ISA::reg, and gem5::X86ISA::val.

Referenced by getReg().

◆ getReg() [2/2]

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 655 of file thread_context.cc.

References gem5::CCRegClass, gem5::IntRegClass, gem5::MiscRegClass, panic, readCCReg(), readCCRegFlat(), readIntReg(), readIntRegFlat(), readVecElem(), readVecElemFlat(), readVecPredReg(), readVecPredRegFlat(), readVecReg(), readVecRegFlat(), gem5::X86ISA::reg, gem5::X86ISA::val, gem5::VecElemClass, gem5::VecPredRegClass, and gem5::VecRegClass.

◆ getSystemPtr()

|

inlineoverridevirtual |

◆ getVecPredRegRscId()

| iris::ResourceId gem5::Iris::ThreadContext::getVecPredRegRscId | ( | RegIndex | vec_reg | ) | const |

Definition at line 922 of file thread_context.cc.

References vecPredRegIds.

Referenced by readVecPredReg().

◆ getVecRegRscId()

| iris::ResourceId gem5::Iris::ThreadContext::getVecRegRscId | ( | RegIndex | vec_reg | ) | const |

◆ getWritableReg()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 761 of file thread_context.cc.

References getWritableVecPredReg(), getWritableVecPredRegFlat(), getWritableVecReg(), getWritableVecRegFlat(), panic, gem5::X86ISA::reg, gem5::VecPredRegClass, and gem5::VecRegClass.

◆ getWritableVecPredReg()

|

inlinevirtual |

Definition at line 312 of file thread_context.hh.

References panic, and gem5::X86ISA::reg.

Referenced by getWritableReg().

◆ getWritableVecPredRegFlat()

|

inlinevirtual |

◆ getWritableVecReg()

|

inlinevirtual |

Definition at line 297 of file thread_context.hh.

References panic, and gem5::X86ISA::reg.

Referenced by getWritableReg().

◆ getWritableVecRegFlat()

|

inlinevirtual |

◆ halt()

|

inlineoverridevirtual |

Set the status to Halted.

Implements gem5::ThreadContext.

Definition at line 247 of file thread_context.hh.

References gem5::ThreadContext::Halted, and setStatus().

◆ htmAbortTransaction()

|

inlineoverridevirtual |

◆ initFromIrisInstance()

|

protectedvirtual |

Reimplemented in gem5::fastmodel::CortexA76TC, and gem5::fastmodel::CortexR52TC.

Definition at line 66 of file thread_context.cc.

References _instId, _status, gem5::ThreadContext::Active, bps, breakpointEventStreamId, call(), client, gem5::statistics::enabled(), installBp(), memorySpaceIds, memorySpaces, semihostingEventStreamId, suspend(), gem5::ThreadContext::Suspended, ThreadContext(), and translations.

Referenced by phaseInitLeave().

◆ installBp()

|

protected |

Definition at line 179 of file thread_context.cc.

References _instId, call(), getBpSpaceIds(), gem5::ArmISA::id, and pc.

Referenced by initFromIrisInstance(), and schedule().

◆ instanceRegistryChanged()

|

protected |

Definition at line 211 of file thread_context.cc.

References _instId, _irisPath, gem5::MipsISA::event, gem5::ArmISA::id, name(), and panic.

◆ maintainStepping()

|

protected |

Definition at line 137 of file thread_context.cc.

References _instId, call(), comInstEventQueue, and getCurrentInstCount().

Referenced by descheduleInstCountEvent(), scheduleInstCountEvent(), and simulationTimeEvent().

◆ noThrow()

|

inlineprotected |

Definition at line 172 of file thread_context.hh.

References client.

Referenced by ThreadContext(), and translateAddress().

◆ pcState() [1/2]

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 578 of file thread_context.cc.

References _instId, gem5::X86ISA::addr, call(), gem5::ArmISA::itState(), gem5::ArmISA::MISCREG_CPSR, pc, pcRscId, and readMiscRegNoEffect().

Referenced by pcStateNoRecord().

◆ pcState() [2/2]

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 600 of file thread_context.cc.

References _instId, call(), gem5::ArmISA::MISCREG_CPSR, pc, pcRscId, readMiscRegNoEffect(), and gem5::X86ISA::val.

◆ pcStateNoRecord()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 350 of file thread_context.hh.

References pcState(), and gem5::X86ISA::val.

◆ phaseInitLeave()

|

protected |

Definition at line 233 of file thread_context.cc.

References _instId, call(), initFromIrisInstance(), and name().

◆ readCCReg()

Definition at line 318 of file thread_context.hh.

References readCCRegFlat().

Referenced by getReg().

◆ readCCRegFlat()

Reimplemented in gem5::fastmodel::CortexA76TC, and gem5::fastmodel::CortexR52TC.

Definition at line 862 of file thread_context.cc.

References _instId, call(), and getCCRegFlatRscId().

Referenced by getReg(), readCCReg(), gem5::fastmodel::CortexA76TC::readCCRegFlat(), and gem5::fastmodel::CortexR52TC::readCCRegFlat().

◆ readIntReg()

Reimplemented in gem5::fastmodel::CortexR52TC.

Definition at line 803 of file thread_context.cc.

References _instId, call(), and getIntRegRscId().

Referenced by getReg(), and semihostingEvent().

◆ readIntRegFlat()

Reimplemented in gem5::fastmodel::CortexA76TC, and gem5::fastmodel::CortexR52TC.

Definition at line 831 of file thread_context.cc.

References _instId, call(), and getIntRegFlatRscId().

Referenced by getReg().

◆ readLastActivate()

|

inlineoverridevirtual |

◆ readLastSuspend()

|

inlineoverridevirtual |

◆ readMem()

|

protected |

Definition at line 448 of file thread_context.cc.

References _instId, gem5::X86ISA::addr, call(), gem5::ArmISA::err, gem5::MipsISA::p, panic_if, and gem5::MipsISA::r.

Referenced by readMemWithCurrentMsn(), gem5::fastmodel::CortexR52TC::sendFunctional(), and sendFunctional().

◆ readMemWithCurrentMsn()

| void gem5::Iris::ThreadContext::readMemWithCurrentMsn | ( | Addr | vaddr, |

| size_t | size, | ||

| char * | data ) |

Definition at line 544 of file thread_context.cc.

References gem5::Iris::CurrentMsn, data, getMemorySpaceId(), readMem(), and gem5::MipsISA::vaddr.

◆ readMiscReg()

Implements gem5::ThreadContext.

Definition at line 358 of file thread_context.hh.

References readMiscRegNoEffect().

◆ readMiscRegNoEffect()

Implements gem5::ThreadContext.

Definition at line 626 of file thread_context.cc.

References _instId, call(), and getMiscRegRscId().

Referenced by getIntRegRscId(), pcState(), pcState(), gem5::fastmodel::CortexA76TC::readIntRegFlat(), readMiscReg(), gem5::fastmodel::CortexR52TC::readMiscRegNoEffect(), gem5::fastmodel::CortexA76TC::setCCRegFlat(), and gem5::fastmodel::CortexA76TC::setIntRegFlat().

◆ readStCondFailures()

|

inlineoverridevirtual |

◆ readVecElem()

Definition at line 303 of file thread_context.hh.

References panic, and gem5::X86ISA::reg.

Referenced by getReg().

◆ readVecElemFlat()

◆ readVecPredReg()

|

virtual |

Definition at line 931 of file thread_context.cc.

References _instId, call(), getVecPredRegRscId(), gem5::RegId::index(), gem5::ArmISA::offset, gem5::X86ISA::reg, and vecPredRegs.

Referenced by getReg(), and readVecPredRegFlat().

◆ readVecPredRegFlat()

|

virtual |

Definition at line 961 of file thread_context.cc.

References readVecPredReg(), and gem5::ArmISA::vecPredRegClass.

Referenced by getReg().

◆ readVecReg()

|

virtual |

Reimplemented in gem5::fastmodel::CortexR52TC.

Definition at line 893 of file thread_context.cc.

References _instId, call(), getVecRegRscId(), gem5::RegId::index(), gem5::X86ISA::reg, and vecRegs.

Referenced by getReg(), and readVecRegFlat().

◆ readVecRegFlat()

|

virtual |

Definition at line 916 of file thread_context.cc.

References readVecReg(), and gem5::ArmISA::vecRegClass.

Referenced by getReg().

◆ regStats()

|

inlineoverridevirtual |

Reimplemented from gem5::ThreadContext.

Definition at line 255 of file thread_context.hh.

References name().

◆ remove()

|

overridevirtual |

Implements gem5::PCEventScope.

Definition at line 436 of file thread_context.cc.

References delBp(), gem5::ArmISA::e, and getOrAllocBp().

◆ schedule()

|

overridevirtual |

Implements gem5::PCEventScope.

Definition at line 424 of file thread_context.cc.

References _instId, gem5::ArmISA::e, getOrAllocBp(), and installBp().

◆ scheduleInstCountEvent()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 499 of file thread_context.cc.

References call(), comInstEventQueue, gem5::X86ISA::count, gem5::MipsISA::event, getCurrentInstCount(), and maintainStepping().

◆ semihostingEvent()

|

protected |

Definition at line 313 of file thread_context.cc.

References _instId, call(), gem5::ArmSystem::callSemihosting(), gem5::curTick(), enableAfterPseudoEvent, getCpuPtr(), readIntReg(), and gem5::EventManager::schedule().

◆ sendFunctional()

|

overridevirtual |

Reimplemented from gem5::ThreadContext.

Definition at line 526 of file thread_context.cc.

References gem5::X86ISA::addr, data, gem5::Packet::getAddr(), getMemorySpaceId(), gem5::Packet::getPtr(), gem5::Packet::getSize(), gem5::Packet::isRead(), gem5::ArmISA::isSecure(), gem5::Packet::makeResponse(), gem5::Iris::PhysicalMemoryNonSecureMsn, gem5::Iris::PhysicalMemorySecureMsn, readMem(), and writeMem().

◆ setCCReg()

Definition at line 345 of file thread_context.hh.

References setCCRegFlat(), and gem5::X86ISA::val.

Referenced by setReg().

◆ setCCRegFlat()

Reimplemented in gem5::fastmodel::CortexA76TC, and gem5::fastmodel::CortexR52TC.

Definition at line 873 of file thread_context.cc.

References _instId, call(), gem5::ArmISA::ccRegClass, getCCRegFlatRscId(), panic_if, and gem5::X86ISA::val.

Referenced by setCCReg(), gem5::fastmodel::CortexA76TC::setCCRegFlat(), gem5::fastmodel::CortexR52TC::setCCRegFlat(), and setReg().

◆ setContextId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 207 of file thread_context.hh.

References _contextId, and gem5::ArmISA::id.

◆ setHtmCheckpointPtr()

|

inlineoverridevirtual |

◆ setIntReg()

Reimplemented in gem5::fastmodel::CortexR52TC.

Definition at line 811 of file thread_context.cc.

References _instId, call(), getIntRegRscId(), and gem5::X86ISA::val.

Referenced by setReg().

◆ setIntRegFlat()

|

virtual |

Reimplemented in gem5::fastmodel::CortexA76TC, and gem5::fastmodel::CortexR52TC.

Definition at line 842 of file thread_context.cc.

References _instId, call(), getIntRegFlatRscId(), gem5::ArmISA::intRegClass, panic_if, and gem5::X86ISA::val.

Referenced by setReg().

◆ setMiscReg()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 365 of file thread_context.hh.

References setMiscRegNoEffect(), and gem5::X86ISA::val.

Referenced by gem5::fastmodel::CortexA76TC::setIntRegFlat().

◆ setMiscRegNoEffect()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 634 of file thread_context.cc.

References _instId, call(), getMiscRegRscId(), and gem5::X86ISA::val.

Referenced by setMiscReg(), and gem5::fastmodel::CortexR52TC::setMiscRegNoEffect().

◆ setProcessPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 238 of file thread_context.hh.

References gem5::MipsISA::p, and panic.

◆ setReg() [1/2]

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 708 of file thread_context.cc.

References gem5::CCRegClass, gem5::IntRegClass, gem5::MiscRegClass, panic, gem5::X86ISA::reg, setCCReg(), setCCRegFlat(), setIntReg(), setIntRegFlat(), setVecElem(), setVecElemFlat(), setVecPredReg(), setVecPredRegFlat(), setVecReg(), setVecRegFlat(), gem5::X86ISA::val, gem5::VecElemClass, gem5::VecPredRegClass, and gem5::VecRegClass.

◆ setReg() [2/2]

Reimplemented from gem5::ThreadContext.

Definition at line 649 of file thread_context.cc.

References gem5::X86ISA::reg, setReg(), and gem5::X86ISA::val.

Referenced by setReg().

◆ setStatus()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 563 of file thread_context.cc.

References _instId, _status, gem5::ThreadContext::Active, call(), gem5::EventManager::deschedule(), enableAfterPseudoEvent, and getCpuPtr().

Referenced by activate(), halt(), and suspend().

◆ setStCondFailures()

|

inlineoverridevirtual |

◆ setThreadId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 204 of file thread_context.hh.

References _threadId, and gem5::ArmISA::id.

◆ setVecElem()

Definition at line 332 of file thread_context.hh.

References panic, gem5::X86ISA::reg, and gem5::X86ISA::val.

Referenced by setReg().

◆ setVecElemFlat()

Definition at line 418 of file thread_context.hh.

References panic, and gem5::X86ISA::val.

Referenced by setReg().

◆ setVecPredReg()

|

inlinevirtual |

Definition at line 338 of file thread_context.hh.

References panic, gem5::X86ISA::reg, and gem5::X86ISA::val.

Referenced by setReg().

◆ setVecPredRegFlat()

|

inlinevirtual |

Definition at line 430 of file thread_context.hh.

References panic, and gem5::X86ISA::val.

Referenced by setReg().

◆ setVecReg()

|

inlinevirtual |

Definition at line 326 of file thread_context.hh.

References panic, gem5::X86ISA::reg, and gem5::X86ISA::val.

Referenced by setReg().

◆ setVecRegFlat()

|

inlinevirtual |

Definition at line 407 of file thread_context.hh.

References panic, and gem5::X86ISA::val.

Referenced by setReg().

◆ simulationTimeEvent()

|

protected |

Definition at line 263 of file thread_context.cc.

References bpAddr, call(), gem5::ArmISA::e, getOrAllocBp(), and maintainStepping().

◆ socketId()

|

inlineoverridevirtual |

◆ status()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 557 of file thread_context.cc.

References _status.

◆ suspend()

|

inlineoverridevirtual |

Set the status to Suspended.

Implements gem5::ThreadContext.

Definition at line 246 of file thread_context.hh.

References setStatus(), and gem5::ThreadContext::Suspended.

Referenced by initFromIrisInstance().

◆ takeOverFrom()

|

inlineoverridevirtual |

◆ threadId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 203 of file thread_context.hh.

References _threadId.

◆ translateAddress() [1/2]

Implemented in gem5::fastmodel::CortexA76TC, and gem5::fastmodel::CortexR52TC.

References gem5::X86ISA::count, gem5::ArmISA::e, gem5::MipsISA::event, and gem5::MipsISA::vaddr.

◆ translateAddress() [2/2]

|

protected |

Definition at line 469 of file thread_context.cc.

References _instId, noThrow(), panic, translations, gem5::MipsISA::vaddr, and warn.

◆ uninstallBp()

|

protected |

Definition at line 191 of file thread_context.cc.

References _instId, and call().

Referenced by delBp().

◆ writeMem()

|

protected |

Definition at line 458 of file thread_context.cc.

References _instId, gem5::X86ISA::addr, call(), data, gem5::ArmISA::err, gem5::MipsISA::p, panic_if, and gem5::MipsISA::r.

Referenced by gem5::fastmodel::CortexR52TC::sendFunctional(), sendFunctional(), and writeMemWithCurrentMsn().

◆ writeMemWithCurrentMsn()

| void gem5::Iris::ThreadContext::writeMemWithCurrentMsn | ( | Addr | vaddr, |

| size_t | size, | ||

| const char * | data ) |

Definition at line 550 of file thread_context.cc.

References gem5::Iris::CurrentMsn, data, getMemorySpaceId(), gem5::MipsISA::vaddr, and writeMem().

Member Data Documentation

◆ _contextId

|

protected |

Definition at line 68 of file thread_context.hh.

Referenced by contextId(), and setContextId().

◆ _cpu

|

protected |

Definition at line 66 of file thread_context.hh.

Referenced by cpuId(), getCpuPtr(), getSystemPtr(), socketId(), and ThreadContext().

◆ _instId

|

protected |

Definition at line 74 of file thread_context.hh.

Referenced by getCurrentInstCount(), initFromIrisInstance(), installBp(), instanceRegistryChanged(), maintainStepping(), pcState(), pcState(), phaseInitLeave(), readCCRegFlat(), gem5::fastmodel::CortexR52TC::readIntReg(), readIntReg(), readIntRegFlat(), readMem(), readMiscRegNoEffect(), readVecPredReg(), readVecReg(), schedule(), semihostingEvent(), setCCRegFlat(), gem5::fastmodel::CortexR52TC::setIntReg(), setIntReg(), setIntRegFlat(), setMiscRegNoEffect(), setStatus(), ThreadContext(), translateAddress(), uninstallBp(), and writeMem().

◆ _irisPath

|

protected |

Definition at line 73 of file thread_context.hh.

Referenced by instanceRegistryChanged(), and ThreadContext().

◆ _isa

|

protected |

Definition at line 71 of file thread_context.hh.

Referenced by getIsaPtr(), and ThreadContext().

◆ _mmu

|

protected |

Definition at line 70 of file thread_context.hh.

Referenced by getMMUPtr(), and ThreadContext().

◆ _status

Definition at line 81 of file thread_context.hh.

Referenced by initFromIrisInstance(), setStatus(), and status().

◆ _system

|

protected |

Definition at line 69 of file thread_context.hh.

Referenced by ThreadContext().

◆ _threadId

|

protected |

Definition at line 67 of file thread_context.hh.

Referenced by setThreadId(), ThreadContext(), and threadId().

◆ bpAddr

|

protected |

Definition at line 137 of file thread_context.hh.

Referenced by breakpointHit(), and simulationTimeEvent().

◆ bps

|

protected |

Definition at line 136 of file thread_context.hh.

Referenced by delBp(), getOrAllocBp(), and initFromIrisInstance().

◆ breakpointEventStreamId

|

protected |

Definition at line 167 of file thread_context.hh.

Referenced by initFromIrisInstance(), and ThreadContext().

◆ ccRegIds

|

protected |

Definition at line 97 of file thread_context.hh.

Referenced by getCCRegFlatRscId(), gem5::fastmodel::CortexA76TC::initFromIrisInstance(), and gem5::fastmodel::CortexR52TC::initFromIrisInstance().

◆ client

|

mutableprotected |

Definition at line 170 of file thread_context.hh.

Referenced by call(), initFromIrisInstance(), noThrow(), ThreadContext(), and ~ThreadContext().

◆ comInstEventQueue

|

protected |

Definition at line 110 of file thread_context.hh.

Referenced by descheduleInstCountEvent(), maintainStepping(), scheduleInstCountEvent(), and ThreadContext().

◆ enableAfterPseudoEvent

|

protected |

Definition at line 82 of file thread_context.hh.

Referenced by semihostingEvent(), setStatus(), ThreadContext(), and ~ThreadContext().

◆ flattenedIntIds

|

protected |

Definition at line 96 of file thread_context.hh.

Referenced by getIntRegFlatRscId(), and gem5::fastmodel::CortexA76TC::initFromIrisInstance().

◆ icountRscId

|

protected |

Definition at line 100 of file thread_context.hh.

◆ initEventStreamId

|

protected |

Definition at line 165 of file thread_context.hh.

Referenced by ThreadContext(), and ~ThreadContext().

◆ intReg32Ids

|

protected |

Definition at line 94 of file thread_context.hh.

Referenced by getIntRegRscId(), gem5::fastmodel::CortexA76TC::initFromIrisInstance(), gem5::fastmodel::CortexR52TC::initFromIrisInstance(), gem5::fastmodel::CortexR52TC::readIntReg(), and gem5::fastmodel::CortexR52TC::setIntReg().

◆ intReg64Ids

|

protected |

Definition at line 95 of file thread_context.hh.

Referenced by getIntRegRscId(), and gem5::fastmodel::CortexA76TC::initFromIrisInstance().

◆ memorySpaceIds

|

protected |

Definition at line 107 of file thread_context.hh.

Referenced by getMemorySpaceId(), and initFromIrisInstance().

◆ memorySpaces

|

protected |

Definition at line 105 of file thread_context.hh.

Referenced by initFromIrisInstance().

◆ miscRegIds

|

protected |

Definition at line 93 of file thread_context.hh.

Referenced by getMiscRegRscId(), gem5::fastmodel::CortexA76TC::initFromIrisInstance(), and gem5::fastmodel::CortexR52TC::initFromIrisInstance().

◆ pc

|

mutableprotected |

Definition at line 174 of file thread_context.hh.

Referenced by breakpointHit(), getOrAllocBp(), installBp(), pcState(), and pcState().

◆ pcRscId

|

protected |

Definition at line 99 of file thread_context.hh.

Referenced by gem5::fastmodel::CortexA76TC::initFromIrisInstance(), gem5::fastmodel::CortexR52TC::initFromIrisInstance(), pcState(), and pcState().

◆ regEventStreamId

|

protected |

Definition at line 164 of file thread_context.hh.

Referenced by ThreadContext(), and ~ThreadContext().

◆ semihostingEventStreamId

|

protected |

Definition at line 168 of file thread_context.hh.

Referenced by initFromIrisInstance(), and ThreadContext().

◆ timeEventStreamId

|

protected |

Definition at line 166 of file thread_context.hh.

Referenced by ThreadContext(), and ~ThreadContext().

◆ translations

|

protected |

Definition at line 106 of file thread_context.hh.

Referenced by initFromIrisInstance(), and translateAddress().

◆ vecPredRegIds

|

protected |

Definition at line 103 of file thread_context.hh.

Referenced by getVecPredRegRscId().

◆ vecPredRegs

|

mutableprotected |

Definition at line 79 of file thread_context.hh.

Referenced by readVecPredReg(), and ThreadContext().

◆ vecRegIds

|

protected |

Definition at line 102 of file thread_context.hh.

Referenced by getVecRegRscId(), and gem5::fastmodel::CortexA76TC::initFromIrisInstance().

◆ vecRegs

|

mutableprotected |

Definition at line 78 of file thread_context.hh.

Referenced by readVecReg(), and ThreadContext().

The documentation for this class was generated from the following files:

- arch/arm/fastmodel/iris/thread_context.hh

- arch/arm/fastmodel/iris/thread_context.cc

Generated on Sat Oct 18 2025 08:06:59 for gem5 by doxygen 1.14.0