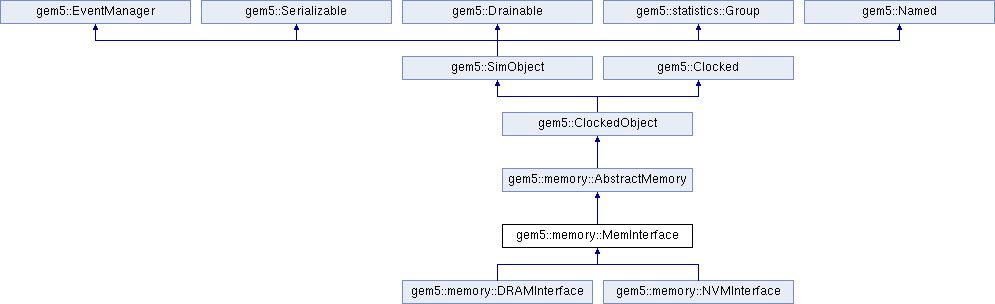

General interface to memory device Includes functions and parameters shared across media types. More...

#include <mem_interface.hh>

Classes | |

| class | Bank |

| A basic class to track the bank state, i.e. More... | |

Public Types | |

| typedef MemInterfaceParams | Params |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| void | setCtrl (MemCtrl *_ctrl, unsigned int command_window, uint8_t pseudo_channel=0) |

| Set a pointer to the controller and initialize interface based on controller parameters. | |

| Addr | getCtrlAddr (Addr addr) |

| Get an address in a dense range which starts from 0. | |

| virtual void | setupRank (const uint8_t rank, const bool is_read)=0 |

| Setup the rank based on packet received. | |

| virtual bool | allRanksDrained () const =0 |

| Check drain state of interface. | |

| virtual std::pair< MemPacketQueue::iterator, Tick > | chooseNextFRFCFS (MemPacketQueue &queue, Tick min_col_at) const =0 |

| For FR-FCFS policy, find first command that can issue Function will be overriden by interface to select based on media characteristics, used to determine when read or write can issue. | |

| virtual Tick | accessLatency () const =0 |

| uint32_t | bytesPerBurst () const |

| virtual Tick | commandOffset () const =0 |

| virtual bool | burstReady (MemPacket *pkt) const =0 |

| Check if a burst operation can be issued to the interface. | |

| Tick | rankDelay () const |

| Determine the required delay for an access to a different rank. | |

| Tick | minReadToWriteDataGap () const |

| Tick | minWriteToReadDataGap () const |

| virtual MemPacket * | decodePacket (const PacketPtr pkt, Addr pkt_addr, unsigned int size, bool is_read, uint8_t pseudo_channel=0) |

| Address decoder to figure out physical mapping onto ranks, banks, and rows. | |

| virtual void | addRankToRankDelay (Tick cmd_at)=0 |

| Add rank to rank delay to bus timing to all banks in all ranks when access to an alternate interface is issued. | |

| virtual bool | isBusy (bool read_queue_empty, bool all_writes_nvm)=0 |

| This function checks if ranks are busy. | |

| virtual std::pair< Tick, Tick > | doBurstAccess (MemPacket *mem_pkt, Tick next_burst_at, const std::vector< MemPacketQueue > &queue)=0 |

| This function performs the burst and update stats. | |

| virtual void | respondEvent (uint8_t rank) |

| This function is DRAM specific. | |

| virtual void | checkRefreshState (uint8_t rank) |

| This function is DRAM specific. | |

| virtual void | drainRanks () |

| This function is DRAM specific. | |

| virtual void | suspend () |

| This function is DRAM specific. | |

| virtual bool | readsWaitingToIssue () const |

| This function is NVM specific. | |

| virtual void | chooseRead (MemPacketQueue &queue) |

| This function is NVM specific. | |

| virtual bool | writeRespQueueFull () const |

| This function is NVM specific. | |

| MemInterface (const Params &_p) | |

| Public Member Functions inherited from gem5::memory::AbstractMemory | |

| PARAMS (AbstractMemory) | |

| AbstractMemory (const Params &p) | |

| virtual | ~AbstractMemory () |

| void | initState () override |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| bool | isNull () const |

| See if this is a null memory that should never store data and always return zero. | |

| void | setBackingStore (uint8_t *pmem_addr) |

| Set the host memory backing store to be used by this memory controller. | |

| void | getBackdoor (MemBackdoorPtr &bd_ptr) |

| const std::list< LockedAddr > & | getLockedAddrList () const |

| Get the list of locked addresses to allow checkpointing. | |

| void | addLockedAddr (LockedAddr addr) |

| Add a locked address to allow for checkpointing. | |

| System * | system () const |

| read the system pointer Implemented for completeness with the setter | |

| void | system (System *sys) |

| Set the system pointer on this memory This can't be done via a python parameter because the system needs pointers to all the memories and the reverse would create a cycle in the object graph. | |

| AddrRange | getAddrRange () const |

| Get the address range. | |

| uint8_t * | toHostAddr (Addr addr) const |

| Transform a gem5 address space address into its physical counterpart in the host address space. | |

| uint64_t | size () const |

| Get the memory size. | |

| Addr | start () const |

| Get the start address. | |

| bool | isConfReported () const |

| Should this memory be passed to the kernel and part of the OS physical memory layout. | |

| bool | isInAddrMap () const |

| Some memories are used as shadow memories or should for other reasons not be part of the global address map. | |

| bool | isKvmMap () const |

| When shadow memories are in use, KVM may want to make one or the other, but cannot map both into the guest address space. | |

| void | access (PacketPtr pkt) |

| Perform an untimed memory access and update all the state (e.g. | |

| void | functionalAccess (PacketPtr pkt) |

| Perform an untimed memory read or write without changing anything but the memory itself. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Public Attributes | |

| const uint32_t | readBufferSize |

| Buffer sizes for read and write queues in the controller These are passed to the controller on instantiation Defining them here allows for buffers to be resized based on memory type / configuration. | |

| const uint32_t | writeBufferSize |

| uint32_t | numWritesQueued |

| NVM specific variable, but declaring it here allows treating different interfaces in a more genral way at the memory controller's end. | |

| Tick | nextBurstAt = 0 |

| Till when the controller must wait before issuing next RD/WR burst? | |

| Tick | nextReqTime = 0 |

| uint32_t | readsThisTime = 0 |

| Reads/writes performed by the controller for this interface before bus direction is switched. | |

| uint32_t | writesThisTime = 0 |

| uint32_t | readQueueSize = 0 |

| Read/write packets in the read/write queue for this interface qos/mem_ctrl.hh has similar counters, but they track all packets in the controller for all memory interfaces connected to the controller. | |

| uint32_t | writeQueueSize = 0 |

| MemCtrl::BusState | busState = MemCtrl::READ |

| MemCtrl::BusState | busStateNext = MemCtrl::READ |

| bus state for next request event triggered | |

| uint8_t | pseudoChannel |

| pseudo channel number used for HBM modeling | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Protected Member Functions | |

| virtual Tick | writeToReadDelay () const |

| Tick | readToWriteDelay () const |

| Tick | rankToRankDelay () const |

| Protected Member Functions inherited from gem5::memory::AbstractMemory | |

| bool | checkLockedAddrList (PacketPtr pkt) |

| void | trackLoadLocked (PacketPtr pkt) |

| bool | writeOK (PacketPtr pkt) |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| MemCtrl * | ctrl |

| A pointer to the parent memory controller instance. | |

| unsigned int | maxCommandsPerWindow |

| Number of commands that can issue in the defined controller command window, used to verify command bandwidth. | |

| enums::AddrMap | addrMapping |

| Memory controller configuration initialized based on parameter values. | |

| const uint32_t | burstSize |

| General device and channel characteristics The rowsPerBank is determined based on the capacity, number of ranks and banks, the burst size, and the row buffer size. | |

| const uint64_t | deviceSize |

| const uint32_t | deviceRowBufferSize |

| const uint32_t | devicesPerRank |

| const uint32_t | rowBufferSize |

| const uint32_t | burstsPerRowBuffer |

| const uint32_t | burstsPerStripe |

| const uint32_t | ranksPerChannel |

| const uint32_t | banksPerRank |

| uint32_t | rowsPerBank |

| GEM5_CLASS_VAR_USED const Tick | tCK |

| General timing requirements. | |

| const Tick | tCS |

| const Tick | tBURST |

| const Tick | tRTW |

| const Tick | tWTR |

| Protected Attributes inherited from gem5::memory::AbstractMemory | |

| AddrRange | range |

| uint8_t * | pmemAddr |

| MemBackdoor | backdoor |

| const bool | confTableReported |

| const bool | inAddrMap |

| const bool | kvmMap |

| const bool | writeable |

| const bool | collectStats |

| std::list< LockedAddr > | lockedAddrList |

| System * | _system |

| Pointer to the System object. | |

| gem5::memory::AbstractMemory::MemStats | stats |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

Detailed Description

General interface to memory device Includes functions and parameters shared across media types.

Definition at line 74 of file mem_interface.hh.

Member Typedef Documentation

◆ Params

| typedef MemInterfaceParams gem5::memory::MemInterface::Params |

Definition at line 415 of file mem_interface.hh.

Constructor & Destructor Documentation

◆ MemInterface()

| gem5::memory::MemInterface::MemInterface | ( | const Params & | _p | ) |

Definition at line 54 of file mem_interface.cc.

References gem5::memory::AbstractMemory::AbstractMemory(), addrMapping, banksPerRank, burstSize, burstsPerRowBuffer, burstsPerStripe, deviceRowBufferSize, deviceSize, devicesPerRank, gem5::X86ISA::granularity, numWritesQueued, gem5::memory::AbstractMemory::range, ranksPerChannel, readBufferSize, rowBufferSize, rowsPerBank, tBURST, tCK, tCS, tRTW, tWTR, and writeBufferSize.

Referenced by gem5::memory::DRAMInterface::DRAMInterface(), and gem5::memory::NVMInterface::NVMInterface().

Member Function Documentation

◆ accessLatency()

|

pure virtual |

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Referenced by gem5::memory::MemCtrl::recvAtomicLogic().

◆ addRankToRankDelay()

|

pure virtual |

Add rank to rank delay to bus timing to all banks in all ranks when access to an alternate interface is issued.

param cmd_at Time of current command used as starting point for addition of rank-to-rank delay

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

◆ allRanksDrained()

|

pure virtual |

Check drain state of interface.

- Returns

- true if all ranks are drained and idle

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

◆ burstReady()

|

pure virtual |

Check if a burst operation can be issued to the interface.

- Parameters

-

Return true if RD/WR can issue

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Referenced by gem5::memory::MemCtrl::packetReady().

◆ bytesPerBurst()

|

inline |

- Returns

- number of bytes in a burst for this interface

Definition at line 278 of file mem_interface.hh.

References burstSize.

Referenced by gem5::memory::MemCtrl::addToReadQueue(), gem5::memory::MemCtrl::addToWriteQueue(), gem5::memory::HeteroMemCtrl::burstAlign(), gem5::memory::MemCtrl::burstAlign(), gem5::memory::HeteroMemCtrl::pktSizeCheck(), and gem5::memory::MemCtrl::pktSizeCheck().

◆ checkRefreshState()

|

inlinevirtual |

This function is DRAM specific.

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 364 of file mem_interface.hh.

References panic.

Referenced by gem5::memory::MemCtrl::processRespondEvent().

◆ chooseNextFRFCFS()

|

pure virtual |

For FR-FCFS policy, find first command that can issue Function will be overriden by interface to select based on media characteristics, used to determine when read or write can issue.

- Parameters

-

queue Queued requests to consider min_col_at Minimum tick for 'seamless' issue

- Returns

- an iterator to the selected packet, else queue.end()

- the tick when the packet selected will issue

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Referenced by gem5::memory::MemCtrl::chooseNextFRFCFS().

◆ chooseRead()

|

inlinevirtual |

This function is NVM specific.

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 400 of file mem_interface.hh.

References panic.

Referenced by gem5::memory::MemCtrl::nonDetermReads().

◆ commandOffset()

|

pure virtual |

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Referenced by gem5::memory::MemCtrl::doBurstAccess().

◆ decodePacket()

|

inlinevirtual |

Address decoder to figure out physical mapping onto ranks, banks, and rows.

This function is called multiple times on the same system packet if the pakcet is larger than burst of the memory. The pkt_addr is used for the offset within the packet.

- Parameters

-

pkt The packet from the outside world pkt_addr The starting address of the packet size The size of the packet in bytes is_read Is the request for a read or a write to memory pseudo_channel pseudo channel number of the packet

- Returns

- A MemPacket pointer with the decoded information

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 324 of file mem_interface.hh.

References panic, and gem5::memory::AbstractMemory::size().

Referenced by gem5::memory::MemCtrl::addToReadQueue(), and gem5::memory::MemCtrl::addToWriteQueue().

◆ doBurstAccess()

|

pure virtual |

This function performs the burst and update stats.

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Referenced by gem5::memory::MemCtrl::doBurstAccess().

◆ drainRanks()

|

inlinevirtual |

This function is DRAM specific.

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 373 of file mem_interface.hh.

References panic.

◆ getCtrlAddr()

Get an address in a dense range which starts from 0.

The input address is the physical address of the request in an address space that contains other SimObjects apart from this controller.

- Parameters

-

addr The intput address which should be in the addrRange

- Returns

- An address in the continues range [0, max)

Definition at line 238 of file mem_interface.hh.

References gem5::X86ISA::addr, and gem5::memory::AbstractMemory::range.

Referenced by gem5::memory::DRAMInterface::decodePacket(), and gem5::memory::NVMInterface::decodePacket().

◆ isBusy()

|

pure virtual |

This function checks if ranks are busy.

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Referenced by gem5::memory::HeteroMemCtrl::memBusy(), and gem5::memory::MemCtrl::memBusy().

◆ minReadToWriteDataGap()

|

inline |

- Returns

- minimum additional bus turnaround required for read-to-write

Definition at line 303 of file mem_interface.hh.

◆ minWriteToReadDataGap()

|

inline |

- Returns

- minimum additional bus turnaround required for write-to-read

Definition at line 309 of file mem_interface.hh.

◆ rankDelay()

|

inline |

Determine the required delay for an access to a different rank.

- Returns

- required rank to rank delay

Definition at line 297 of file mem_interface.hh.

References tCS.

◆ rankToRankDelay()

|

inlineprotected |

Definition at line 166 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::addRankToRankDelay(), gem5::memory::NVMInterface::addRankToRankDelay(), gem5::memory::DRAMInterface::doBurstAccess(), and gem5::memory::NVMInterface::doBurstAccess().

◆ readsWaitingToIssue()

|

inlinevirtual |

This function is NVM specific.

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 391 of file mem_interface.hh.

References panic.

Referenced by gem5::memory::MemCtrl::nonDetermReads().

◆ readToWriteDelay()

|

inlineprotected |

Definition at line 161 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::doBurstAccess(), and gem5::memory::NVMInterface::doBurstAccess().

◆ respondEvent()

|

inlinevirtual |

This function is DRAM specific.

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 356 of file mem_interface.hh.

References panic.

Referenced by gem5::memory::MemCtrl::processRespondEvent().

◆ setCtrl()

| void gem5::memory::MemInterface::setCtrl | ( | MemCtrl * | _ctrl, |

| unsigned int | command_window, | ||

| uint8_t | pseudo_channel = 0 ) |

Set a pointer to the controller and initialize interface based on controller parameters.

- Parameters

-

_ctrl pointer to the parent controller command_window size of command window used to check command bandwidth pseudo_channel pseudo channel number

Definition at line 77 of file mem_interface.cc.

References ctrl, maxCommandsPerWindow, pseudoChannel, and tCK.

◆ setupRank()

|

pure virtual |

Setup the rank based on packet received.

- Parameters

-

integer value of rank to be setup. used to index ranks vector are we setting up rank for read or write packet?

Implemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Referenced by gem5::memory::MemCtrl::addToReadQueue(), and gem5::memory::MemCtrl::addToWriteQueue().

◆ suspend()

|

inlinevirtual |

This function is DRAM specific.

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 382 of file mem_interface.hh.

References panic.

◆ writeRespQueueFull()

|

inlinevirtual |

This function is NVM specific.

Reimplemented in gem5::memory::DRAMInterface, and gem5::memory::NVMInterface.

Definition at line 409 of file mem_interface.hh.

References panic.

Referenced by gem5::memory::MemCtrl::nvmWriteBlock().

◆ writeToReadDelay()

|

inlineprotectedvirtual |

Reimplemented in gem5::memory::DRAMInterface.

Definition at line 156 of file mem_interface.hh.

Referenced by gem5::memory::NVMInterface::doBurstAccess().

Member Data Documentation

◆ addrMapping

|

protected |

Memory controller configuration initialized based on parameter values.

Definition at line 126 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::decodePacket(), gem5::memory::NVMInterface::decodePacket(), gem5::memory::DRAMInterface::init(), and MemInterface().

◆ banksPerRank

|

protected |

Definition at line 141 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::activateBank(), gem5::memory::DRAMInterface::addRankToRankDelay(), gem5::memory::NVMInterface::addRankToRankDelay(), gem5::memory::DRAMInterface::decodePacket(), gem5::memory::NVMInterface::decodePacket(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::NVMInterface::doBurstAccess(), gem5::memory::DRAMInterface::DRAMInterface(), MemInterface(), gem5::memory::DRAMInterface::minBankPrep(), and gem5::memory::DRAMInterface::prechargeBank().

◆ burstSize

|

protected |

General device and channel characteristics The rowsPerBank is determined based on the capacity, number of ranks and banks, the burst size, and the row buffer size.

Definition at line 133 of file mem_interface.hh.

Referenced by bytesPerBurst(), gem5::memory::NVMInterface::chooseRead(), gem5::memory::DRAMInterface::decodePacket(), gem5::memory::NVMInterface::decodePacket(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::NVMInterface::doBurstAccess(), gem5::memory::DRAMInterface::DRAMInterface(), and MemInterface().

◆ burstsPerRowBuffer

|

protected |

Definition at line 138 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::decodePacket(), gem5::memory::NVMInterface::decodePacket(), gem5::memory::DRAMInterface::DRAMInterface(), gem5::memory::DRAMInterface::init(), and MemInterface().

◆ burstsPerStripe

|

protected |

Definition at line 139 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::decodePacket(), gem5::memory::NVMInterface::decodePacket(), gem5::memory::DRAMInterface::init(), and MemInterface().

◆ busState

| MemCtrl::BusState gem5::memory::MemInterface::busState = MemCtrl::READ |

Definition at line 209 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::inReadBusState(), gem5::memory::MemCtrl::inWriteBusState(), and gem5::memory::MemCtrl::processNextReqEvent().

◆ busStateNext

| MemCtrl::BusState gem5::memory::MemInterface::busStateNext = MemCtrl::READ |

bus state for next request event triggered

Definition at line 212 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::inReadBusState(), gem5::memory::MemCtrl::inWriteBusState(), and gem5::memory::MemCtrl::processNextReqEvent().

◆ ctrl

|

protected |

A pointer to the parent memory controller instance.

Definition at line 114 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::activateBank(), gem5::memory::NVMInterface::burstReady(), gem5::memory::NVMInterface::chooseRead(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::NVMInterface::doBurstAccess(), gem5::memory::NVMInterface::isBusy(), gem5::memory::DRAMInterface::minBankPrep(), gem5::memory::DRAMInterface::prechargeBank(), gem5::memory::NVMInterface::processReadReadyEvent(), gem5::memory::NVMInterface::processWriteRespondEvent(), and setCtrl().

◆ deviceRowBufferSize

|

protected |

Definition at line 135 of file mem_interface.hh.

Referenced by MemInterface().

◆ deviceSize

|

protected |

Definition at line 134 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::DRAMInterface(), and MemInterface().

◆ devicesPerRank

|

protected |

Definition at line 136 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::DRAMInterface(), and MemInterface().

◆ maxCommandsPerWindow

|

protected |

Number of commands that can issue in the defined controller command window, used to verify command bandwidth.

Definition at line 120 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::activateBank(), gem5::memory::NVMInterface::chooseRead(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::NVMInterface::doBurstAccess(), gem5::memory::DRAMInterface::prechargeBank(), and setCtrl().

◆ nextBurstAt

| Tick gem5::memory::MemInterface::nextBurstAt = 0 |

Till when the controller must wait before issuing next RD/WR burst?

Definition at line 189 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::chooseNextFRFCFS(), and gem5::memory::MemCtrl::doBurstAccess().

◆ nextReqTime

| Tick gem5::memory::MemInterface::nextReqTime = 0 |

Definition at line 190 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::doBurstAccess(), and gem5::memory::MemCtrl::processNextReqEvent().

◆ numWritesQueued

| uint32_t gem5::memory::MemInterface::numWritesQueued |

NVM specific variable, but declaring it here allows treating different interfaces in a more genral way at the memory controller's end.

Definition at line 184 of file mem_interface.hh.

Referenced by gem5::memory::NVMInterface::doBurstAccess(), gem5::memory::MemCtrl::memBusy(), MemInterface(), gem5::memory::MemCtrl::nvmWriteBlock(), and gem5::memory::NVMInterface::setupRank().

◆ pseudoChannel

| uint8_t gem5::memory::MemInterface::pseudoChannel |

pseudo channel number used for HBM modeling

Definition at line 217 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::addToReadQueue(), gem5::memory::MemCtrl::addToWriteQueue(), gem5::memory::MemCtrl::chooseNext(), gem5::memory::DRAMInterface::chooseNextFRFCFS(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::DRAMInterface::minBankPrep(), and setCtrl().

◆ ranksPerChannel

|

protected |

Definition at line 140 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::chooseNextFRFCFS(), gem5::memory::DRAMInterface::decodePacket(), gem5::memory::NVMInterface::decodePacket(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::DRAMInterface::DRAMInterface(), gem5::memory::DRAMInterface::isBusy(), MemInterface(), and gem5::memory::DRAMInterface::minBankPrep().

◆ readBufferSize

| const uint32_t gem5::memory::MemInterface::readBufferSize |

Buffer sizes for read and write queues in the controller These are passed to the controller on instantiation Defining them here allows for buffers to be resized based on memory type / configuration.

Definition at line 176 of file mem_interface.hh.

Referenced by MemInterface().

◆ readQueueSize

| uint32_t gem5::memory::MemInterface::readQueueSize = 0 |

Read/write packets in the read/write queue for this interface qos/mem_ctrl.hh has similar counters, but they track all packets in the controller for all memory interfaces connected to the controller.

Definition at line 205 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::addToReadQueue(), gem5::memory::MemCtrl::memBusy(), and gem5::memory::MemCtrl::processNextReqEvent().

◆ readsThisTime

| uint32_t gem5::memory::MemInterface::readsThisTime = 0 |

Reads/writes performed by the controller for this interface before bus direction is switched.

Definition at line 196 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::doBurstAccess(), and gem5::memory::MemCtrl::processNextReqEvent().

◆ rowBufferSize

|

protected |

Definition at line 137 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::DRAMInterface(), gem5::memory::DRAMInterface::init(), and MemInterface().

◆ rowsPerBank

|

protected |

Definition at line 142 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::decodePacket(), gem5::memory::NVMInterface::decodePacket(), gem5::memory::DRAMInterface::DRAMInterface(), and MemInterface().

◆ tBURST

|

protected |

Definition at line 149 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::burstDelay(), gem5::memory::NVMInterface::commandOffset(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::NVMInterface::doBurstAccess(), gem5::memory::DRAMInterface::DRAMInterface(), MemInterface(), rankToRankDelay(), readToWriteDelay(), gem5::memory::DRAMInterface::writeToReadDelay(), and writeToReadDelay().

◆ tCK

|

protected |

General timing requirements.

Definition at line 147 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::activateBank(), gem5::memory::NVMInterface::chooseRead(), gem5::memory::DRAMInterface::doBurstAccess(), gem5::memory::NVMInterface::doBurstAccess(), MemInterface(), gem5::memory::DRAMInterface::prechargeBank(), setCtrl(), and gem5::memory::DRAMInterface::startup().

◆ tCS

|

protected |

Definition at line 148 of file mem_interface.hh.

Referenced by MemInterface(), minReadToWriteDataGap(), minWriteToReadDataGap(), rankDelay(), and rankToRankDelay().

◆ tRTW

|

protected |

Definition at line 150 of file mem_interface.hh.

Referenced by gem5::memory::DRAMInterface::DRAMInterface(), MemInterface(), minReadToWriteDataGap(), and readToWriteDelay().

◆ tWTR

|

protected |

Definition at line 151 of file mem_interface.hh.

Referenced by MemInterface(), minWriteToReadDataGap(), gem5::memory::DRAMInterface::writeToReadDelay(), and writeToReadDelay().

◆ writeBufferSize

| const uint32_t gem5::memory::MemInterface::writeBufferSize |

Definition at line 177 of file mem_interface.hh.

Referenced by MemInterface().

◆ writeQueueSize

| uint32_t gem5::memory::MemInterface::writeQueueSize = 0 |

Definition at line 206 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::addToWriteQueue(), gem5::memory::MemCtrl::memBusy(), and gem5::memory::MemCtrl::processNextReqEvent().

◆ writesThisTime

| uint32_t gem5::memory::MemInterface::writesThisTime = 0 |

Definition at line 197 of file mem_interface.hh.

Referenced by gem5::memory::MemCtrl::doBurstAccess(), and gem5::memory::MemCtrl::processNextReqEvent().

The documentation for this class was generated from the following files:

- mem/mem_interface.hh

- mem/mem_interface.cc

Generated on Sat Oct 18 2025 08:06:59 for gem5 by doxygen 1.14.0