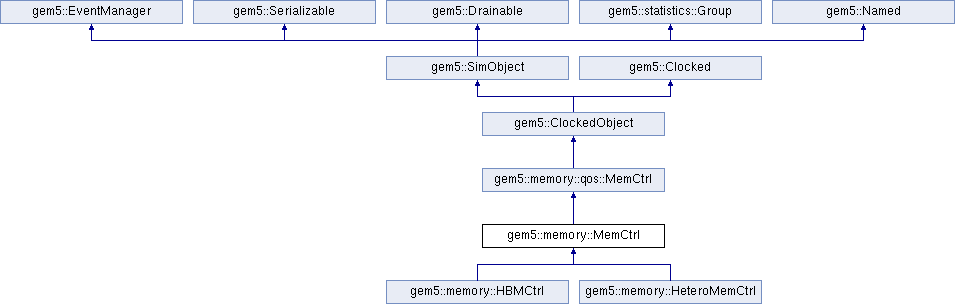

The memory controller is a single-channel memory controller capturing the most important timing constraints associated with a contemporary controller. More...

#include <mem_ctrl.hh>

Classes | |

| struct | CtrlStats |

| class | MemoryPort |

Public Member Functions | |

| MemCtrl (const MemCtrlParams &p) | |

| virtual bool | allIntfDrained () const |

| Ensure that all interfaced have drained commands. | |

| DrainState | drain () override |

| Draining is the process of clearing out the states of SimObjects.These are the SimObjects that are partially executed or are partially in flight. | |

| virtual Tick | verifySingleCmd (Tick cmd_tick, Tick max_cmds_per_burst, bool row_cmd) |

| Check for command bus contention for single cycle command. | |

| virtual Tick | verifyMultiCmd (Tick cmd_tick, Tick max_cmds_per_burst, Tick max_multi_cmd_split=0) |

| Check for command bus contention for multi-cycle (2 currently) command. | |

| virtual bool | respondEventScheduled (uint8_t pseudo_channel=0) const |

| Is there a respondEvent scheduled? | |

| virtual bool | requestEventScheduled (uint8_t pseudo_channel=0) const |

| Is there a read/write burst Event scheduled? | |

| virtual void | restartScheduler (Tick tick, uint8_t pseudo_channel=0) |

| restart the controller This can be used by interfaces to restart the scheduler after maintainence commands complete | |

| bool | inReadBusState (bool next_state, const MemInterface *mem_intr) const |

| Check the current direction of the memory channel. | |

| bool | inWriteBusState (bool next_state, const MemInterface *mem_intr) const |

| Check the current direction of the memory channel. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| virtual void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | startup () override |

| startup() is the final initialization call before simulation. | |

| virtual void | drainResume () override |

| Resume execution after a successful drain. | |

| Public Member Functions inherited from gem5::memory::qos::MemCtrl | |

| MemCtrl (const QoSMemCtrlParams &) | |

| QoS Memory base class. | |

| virtual | ~MemCtrl () |

| BusState | getBusState () const |

| Gets the current bus state. | |

| BusState | getBusStateNext () const |

| Gets the next bus state. | |

| bool | hasRequestor (RequestorID id) const |

| hasRequestor returns true if the selected requestor(ID) has been registered in the memory controller, which happens if the memory controller has received at least a packet from that requestor. | |

| uint64_t | getReadQueueSize (const uint8_t prio) const |

| Gets a READ queue size. | |

| uint64_t | getWriteQueueSize (const uint8_t prio) const |

| Gets a WRITE queue size. | |

| uint64_t | getTotalReadQueueSize () const |

| Gets the total combined READ queues size. | |

| uint64_t | getTotalWriteQueueSize () const |

| Gets the total combined WRITE queues size. | |

| Tick | getServiceTick (const uint8_t prio) const |

| Gets the last service tick related to a QoS Priority. | |

| uint8_t | numPriorities () const |

| Gets the total number of priority levels in the QoS memory controller. | |

| System * | system () const |

| read the system pointer | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Protected Member Functions | |

| virtual void | processNextReqEvent (MemInterface *mem_intr, MemPacketQueue &resp_queue, EventFunctionWrapper &resp_event, EventFunctionWrapper &next_req_event, bool &retry_wr_req) |

| Bunch of things requires to setup "events" in gem5 When event "respondEvent" occurs for example, the method processRespondEvent is called; no parameters are allowed in these methods. | |

| virtual void | processRespondEvent (MemInterface *mem_intr, MemPacketQueue &queue, EventFunctionWrapper &resp_event, bool &retry_rd_req) |

| bool | readQueueFull (unsigned int pkt_count) const |

| Check if the read queue has room for more entries. | |

| bool | writeQueueFull (unsigned int pkt_count) const |

| Check if the write queue has room for more entries. | |

| bool | addToReadQueue (PacketPtr pkt, unsigned int pkt_count, MemInterface *mem_intr) |

| When a new read comes in, first check if the write q has a pending request to the same address. If not, decode the address to populate rank/bank/row, create one or mutliple "mem_pkt", and push them to the back of the read queue. | |

| void | addToWriteQueue (PacketPtr pkt, unsigned int pkt_count, MemInterface *mem_intr) |

| Decode the incoming pkt, create a mem_pkt and push to the back of the write queue. | |

| virtual Tick | doBurstAccess (MemPacket *mem_pkt, MemInterface *mem_intr) |

| Actually do the burst based on media specific access function. | |

| virtual void | accessAndRespond (PacketPtr pkt, Tick static_latency, MemInterface *mem_intr) |

| When a packet reaches its "readyTime" in the response Q, use the "access()" method in AbstractMemory to actually create the response packet, and send it back to the outside world requestor. | |

| virtual bool | packetReady (MemPacket *pkt, MemInterface *mem_intr) |

| Determine if there is a packet that can issue. | |

| virtual Tick | minReadToWriteDataGap () |

| Calculate the minimum delay used when scheduling a read-to-write transision. | |

| virtual Tick | minWriteToReadDataGap () |

| Calculate the minimum delay used when scheduling a write-to-read transision. | |

| virtual MemPacketQueue::iterator | chooseNext (MemPacketQueue &queue, Tick extra_col_delay, MemInterface *mem_intr) |

| The memory schduler/arbiter - picks which request needs to go next, based on the specified policy such as FCFS or FR-FCFS and moves it to the head of the queue. | |

| virtual std::pair< MemPacketQueue::iterator, Tick > | chooseNextFRFCFS (MemPacketQueue &queue, Tick extra_col_delay, MemInterface *mem_intr) |

| For FR-FCFS policy reorder the read/write queue depending on row buffer hits and earliest bursts available in memory. | |

| Tick | getBurstWindow (Tick cmd_tick) |

| Calculate burst window aligned tick. | |

| void | printQs () const |

| Used for debugging to observe the contents of the queues. | |

| virtual Addr | burstAlign (Addr addr, MemInterface *mem_intr) const |

| Burst-align an address. | |

| virtual bool | pktSizeCheck (MemPacket *mem_pkt, MemInterface *mem_intr) const |

| Check if mem pkt's size is sane. | |

| virtual AddrRangeList | getAddrRanges () |

| std::vector< MemPacketQueue > & | selQueue (bool is_read) |

| Select either the read or write queue. | |

| virtual bool | respQEmpty () |

| virtual bool | memBusy (MemInterface *mem_intr) |

| Checks if the memory interface is already busy. | |

| virtual void | nonDetermReads (MemInterface *mem_intr) |

| Will access memory interface and select non-deterministic reads to issue. | |

| virtual bool | nvmWriteBlock (MemInterface *mem_intr) |

| Will check if all writes are for nvm interface and nvm's write resp queue is full. | |

| virtual void | pruneBurstTick () |

| Remove commands that have already issued from burstTicks. | |

| virtual Tick | recvAtomic (PacketPtr pkt) |

| virtual Tick | recvAtomicBackdoor (PacketPtr pkt, MemBackdoorPtr &backdoor) |

| virtual void | recvFunctional (PacketPtr pkt) |

| virtual void | recvMemBackdoorReq (const MemBackdoorReq &req, MemBackdoorPtr &backdoor) |

| virtual bool | recvTimingReq (PacketPtr pkt) |

| bool | recvFunctionalLogic (PacketPtr pkt, MemInterface *mem_intr) |

| Tick | recvAtomicLogic (PacketPtr pkt, MemInterface *mem_intr) |

| Protected Member Functions inherited from gem5::memory::qos::MemCtrl | |

| void | addRequestor (const RequestorID id) |

| Initializes dynamically counters and statistics for a given Requestor. | |

| void | logRequest (BusState dir, RequestorID id, uint8_t _qos, Addr addr, uint64_t entries) |

| Called upon receiving a request or updates statistics and updates queues status. | |

| void | logResponse (BusState dir, RequestorID id, uint8_t _qos, Addr addr, uint64_t entries, double delay) |

| Called upon receiving a response, updates statistics and updates queues status. | |

| template<typename Queues> | |

| uint8_t | qosSchedule (std::initializer_list< Queues * > queues_ptr, uint64_t queue_entry_size, const PacketPtr pkt) |

| Assign priority to a packet by executing the configured QoS policy. | |

| uint8_t | schedule (RequestorID id, uint64_t data) |

| uint8_t | schedule (const PacketPtr pkt) |

| BusState | selectNextBusState () |

| Returns next bus direction (READ or WRITE) based on configured policy. | |

| void | setCurrentBusState () |

| Set current bus direction (READ or WRITE) from next selected one. | |

| void | recordTurnaroundStats (BusState busState, BusState busStateNext) |

| Record statistics on turnarounds based on busStateNext and busState values. | |

| template<typename Queues> | |

| void | escalate (std::initializer_list< Queues * > queues, uint64_t queue_entry_size, RequestorID id, uint8_t tgt_prio) |

| Escalates/demotes priority of all packets belonging to the passed requestor to given priority value. | |

| template<typename Queues> | |

| void | escalateQueues (Queues &queues, uint64_t queue_entry_size, RequestorID id, uint8_t curr_prio, uint8_t tgt_prio) |

| Escalates/demotes priority of all packets belonging to the passed requestor to given priority value in a specified cluster of queues (e.g. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| MemoryPort | port |

| Our incoming port, for a multi-ported controller add a crossbar in front of it. | |

| bool | isTimingMode |

| Remember if the memory system is in timing mode. | |

| bool | retryRdReq |

| Remember if we have to retry a request when available. | |

| bool | retryWrReq |

| EventFunctionWrapper | nextReqEvent |

| EventFunctionWrapper | respondEvent |

| std::vector< MemPacketQueue > | readQueue |

| The controller's main read and write queues, with support for QoS reordering. | |

| std::vector< MemPacketQueue > | writeQueue |

| std::unordered_set< Addr > | isInWriteQueue |

| To avoid iterating over the write queue to check for overlapping transactions, maintain a set of burst addresses that are currently queued. | |

| std::deque< MemPacket * > | respQueue |

| Response queue where read packets wait after we're done working with them, but it's not time to send the response yet. | |

| std::unordered_multiset< Tick > | burstTicks |

| Holds count of commands issued in burst window starting at defined Tick. | |

| MemInterface * | dram |

| uint32_t | readBufferSize |

| The following are basic design parameters of the memory controller, and are initialized based on parameter values. | |

| uint32_t | writeBufferSize |

| uint32_t | writeHighThreshold |

| uint32_t | writeLowThreshold |

| const uint32_t | minWritesPerSwitch |

| const uint32_t | minReadsPerSwitch |

| enums::MemSched | memSchedPolicy |

| Memory controller configuration initialized based on parameter values. | |

| const Tick | frontendLatency |

| Pipeline latency of the controller frontend. | |

| const Tick | backendLatency |

| Pipeline latency of the backend and PHY. | |

| const Tick | commandWindow |

| Length of a command window, used to check command bandwidth. | |

| Tick | nextBurstAt |

| Till when must we wait before issuing next RD/WR burst? | |

| Tick | prevArrival |

| Tick | nextReqTime |

| The soonest you have to start thinking about the next request is the longest access time that can occur before nextBurstAt. | |

| CtrlStats | stats |

| std::unique_ptr< Packet > | pendingDelete |

| Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call. | |

| Protected Attributes inherited from gem5::memory::qos::MemCtrl | |

| const std::unique_ptr< Policy > | policy |

| QoS Policy, assigns QoS priority to the incoming packets. | |

| const std::unique_ptr< TurnaroundPolicy > | turnPolicy |

| QoS Bus Turnaround Policy: selects the bus direction (READ/WRITE) | |

| const std::unique_ptr< QueuePolicy > | queuePolicy |

| QoS Queue Policy: selects packet among same-priority queue. | |

| const uint8_t | _numPriorities |

| Number of configured QoS priorities. | |

| const bool | qosPriorityEscalation |

| Enables QoS priority escalation. | |

| const bool | qosSyncroScheduler |

| Enables QoS synchronized scheduling invokes the QoS scheduler on all requestors, at every packet arrival. | |

| std::unordered_map< RequestorID, const std::string > | requestors |

| Hash of requestor ID - requestor name. | |

| std::unordered_map< RequestorID, std::vector< uint64_t > > | packetPriorities |

| Hash of requestors - number of packets queued per priority. | |

| std::unordered_map< RequestorID, std::unordered_map< uint64_t, std::deque< uint64_t > > > | requestTimes |

| Hash of requestors - address of request - queue of times of request. | |

| std::vector< Tick > | serviceTick |

| Vector of QoS priorities/last service time. | |

| std::vector< uint64_t > | readQueueSizes |

| Read request packets queue length in #packets, per QoS priority. | |

| std::vector< uint64_t > | writeQueueSizes |

| Write request packets queue length in #packets, per QoS priority. | |

| uint64_t | totalReadQueueSize |

| Total read request packets queue length in #packets. | |

| uint64_t | totalWriteQueueSize |

| Total write request packets queue length in #packets. | |

| BusState | busState |

| Bus state used to control the read/write switching and drive the scheduling of the next request. | |

| BusState | busStateNext |

| bus state for next request event triggered | |

| gem5::memory::qos::MemCtrl::MemCtrlStats | stats |

| System * | _system |

| Pointer to the System object. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Public Types inherited from gem5::memory::qos::MemCtrl | |

| enum | BusState { READ , WRITE } |

| Bus Direction. More... | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Detailed Description

The memory controller is a single-channel memory controller capturing the most important timing constraints associated with a contemporary controller.

For multi-channel memory systems, the controller is combined with a crossbar model, with the channel address interleaving taking part in the crossbar.

As a basic design principle, this controller model is not cycle callable, but instead uses events to: 1) decide when new decisions can be made, 2) when resources become available, 3) when things are to be considered done, and 4) when to send things back. The controller interfaces to media specific interfaces to enable flexible topoloties. Through these simple principles, the model delivers high performance, and lots of flexibility, allowing users to evaluate the system impact of a wide range of memory technologies.

For more details, please see Hansson et al, "Simulating DRAM controllers for future system architecture exploration", Proc. ISPASS, 2014. If you use this model as part of your research please cite the paper.

Definition at line 246 of file mem_ctrl.hh.

Constructor & Destructor Documentation

◆ MemCtrl()

| gem5::memory::MemCtrl::MemCtrl | ( | const MemCtrlParams & | p | ) |

Definition at line 60 of file mem_ctrl.cc.

References dram, isTimingMode, MemCtrl(), gem5::Named::name(), nextReqEvent, gem5::MipsISA::p, port, processNextReqEvent(), respondEvent, respQueue, retryRdReq, and retryWrReq.

Referenced by accessAndRespond(), addToReadQueue(), addToWriteQueue(), gem5::memory::HeteroMemCtrl::chooseNext(), chooseNext(), chooseNextFRFCFS(), gem5::memory::MemCtrl::CtrlStats::CtrlStats(), doBurstAccess(), gem5::memory::HBMCtrl::HBMCtrl(), gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), MemCtrl(), gem5::memory::MemCtrl::MemoryPort::MemoryPort(), printQs(), processNextReqEvent(), gem5::memory::HeteroMemCtrl::processRespondEvent(), processRespondEvent(), pruneBurstTick(), gem5::memory::HBMCtrl::pruneColBurstTick(), gem5::memory::HBMCtrl::pruneRowBurstTick(), readQueueFull(), gem5::memory::HBMCtrl::readQueueFullPC0(), gem5::memory::HBMCtrl::readQueueFullPC1(), recvAtomicLogic(), gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), recvTimingReq(), gem5::memory::HBMCtrl::verifyMultiCmd(), verifyMultiCmd(), gem5::memory::HBMCtrl::verifySingleCmd(), verifySingleCmd(), writeQueueFull(), gem5::memory::HBMCtrl::writeQueueFullPC0(), and gem5::memory::HBMCtrl::writeQueueFullPC1().

Member Function Documentation

◆ accessAndRespond()

|

protectedvirtual |

When a packet reaches its "readyTime" in the response Q, use the "access()" method in AbstractMemory to actually create the response packet, and send it back to the outside world requestor.

- Parameters

-

pkt The packet from the outside world static_latency Static latency to add before sending the packet mem_intr the memory interface to access

Definition at line 622 of file mem_ctrl.cc.

References gem5::memory::AbstractMemory::access(), gem5::AddrRange::contains(), gem5::curTick(), DPRINTF, gem5::Packet::getAddr(), gem5::memory::AbstractMemory::getAddrRange(), gem5::Packet::headerDelay, gem5::Packet::isResponse(), MemCtrl(), gem5::Packet::needsResponse(), panic_if, gem5::Packet::payloadDelay, pendingDelete, port, and gem5::Packet::print().

Referenced by addToReadQueue(), addToWriteQueue(), and processRespondEvent().

◆ addToReadQueue()

|

protected |

When a new read comes in, first check if the write q has a pending request to the same address. If not, decode the address to populate rank/bank/row, create one or mutliple "mem_pkt", and push them to the back of the read queue.

\ If this is the only read request in the system, schedule an event to start servicing it.

- Parameters

-

pkt The request packet from the outside world pkt_count The number of memory bursts the pkt mem_intr The memory interface this pkt will eventually go to

- Returns

- if all the read pkts are already serviced by wrQ

Definition at line 189 of file mem_ctrl.cc.

References accessAndRespond(), gem5::memory::MemPacket::addr, gem5::X86ISA::addr, burstAlign(), gem5::memory::MemPacket::burstHelper, gem5::memory::BurstHelper::burstsServiced, gem5::memory::MemInterface::bytesPerBurst(), gem5::ceilLog2(), gem5::memory::MemInterface::decodePacket(), DPRINTF, frontendLatency, gem5::Packet::getAddr(), gem5::Packet::getSize(), isInWriteQueue, gem5::Packet::isWrite(), gem5::memory::qos::MemCtrl::logRequest(), gem5::MaxTick, MemCtrl(), gem5::MipsISA::p, gem5::memory::MemInterface::pseudoChannel, gem5::memory::MemPacket::qosValue(), gem5::Packet::qosValue(), gem5::memory::MemPacket::rank, gem5::memory::qos::MemCtrl::READ, readQueue, readQueueFull(), gem5::memory::MemInterface::readQueueSize, gem5::memory::MemPacket::readyTime, gem5::Packet::requestorId(), respQueue, gem5::memory::MemInterface::setupRank(), stats, gem5::memory::qos::MemCtrl::totalReadQueueSize, gem5::PowerISA::vec, and writeQueue.

Referenced by gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

◆ addToWriteQueue()

|

protected |

Decode the incoming pkt, create a mem_pkt and push to the back of the write queue.

\If the write q length is more than the threshold specified by the user, ie the queue is beginning to get full, stop reads, and start draining writes.

- Parameters

-

pkt The request packet from the outside world pkt_count The number of memory bursts the pkt mem_intr The memory interface this pkt will eventually go to

Definition at line 304 of file mem_ctrl.cc.

References accessAndRespond(), gem5::memory::MemPacket::addr, gem5::X86ISA::addr, burstAlign(), gem5::memory::MemInterface::bytesPerBurst(), gem5::ceilLog2(), gem5::memory::MemInterface::decodePacket(), DPRINTF, frontendLatency, gem5::Packet::getAddr(), gem5::Packet::getSize(), isInWriteQueue, gem5::Packet::isWrite(), gem5::memory::qos::MemCtrl::logRequest(), gem5::MaxTick, MemCtrl(), gem5::memory::MemInterface::pseudoChannel, gem5::memory::MemPacket::qosValue(), gem5::Packet::qosValue(), gem5::memory::MemPacket::rank, gem5::memory::MemPacket::readyTime, gem5::Packet::requestorId(), gem5::memory::MemInterface::setupRank(), stats, gem5::memory::qos::MemCtrl::totalWriteQueueSize, gem5::memory::qos::MemCtrl::WRITE, writeBufferSize, writeQueue, and gem5::memory::MemInterface::writeQueueSize.

Referenced by gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

◆ allIntfDrained()

|

virtual |

Ensure that all interfaced have drained commands.

- Returns

- bool flag, set once drain complete

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 1417 of file mem_ctrl.cc.

References dram.

Referenced by drain(), processNextReqEvent(), and processRespondEvent().

◆ burstAlign()

|

protectedvirtual |

Burst-align an address.

- Parameters

-

addr The potentially unaligned address mem_intr The DRAM interface this pkt belongs to

- Returns

- An address aligned to a memory burst

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 1170 of file mem_ctrl.cc.

References gem5::X86ISA::addr, and gem5::memory::MemInterface::bytesPerBurst().

Referenced by addToReadQueue(), addToWriteQueue(), and processNextReqEvent().

◆ chooseNext()

|

protectedvirtual |

The memory schduler/arbiter - picks which request needs to go next, based on the specified policy such as FCFS or FR-FCFS and moves it to the head of the queue.

Prioritizes accesses to the same rank as previous burst unless controller is switching command type.

- Parameters

-

queue Queued requests to consider extra_col_delay Any extra delay due to a read/write switch mem_intr the memory interface to choose from

- Returns

- an iterator to the selected packet, else queue.end()

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 557 of file mem_ctrl.cc.

References chooseNextFRFCFS(), DPRINTF, gem5::ArmISA::i, MemCtrl(), memSchedPolicy, packetReady(), panic, gem5::memory::MemInterface::pseudoChannel, and gem5::memory::MemPacket::pseudoChannel.

Referenced by processNextReqEvent().

◆ chooseNextFRFCFS()

|

protectedvirtual |

For FR-FCFS policy reorder the read/write queue depending on row buffer hits and earliest bursts available in memory.

- Parameters

-

queue Queued requests to consider extra_col_delay Any extra delay due to a read/write switch

- Returns

- an iterator to the selected packet, else queue.end()

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 601 of file mem_ctrl.cc.

References gem5::memory::MemInterface::chooseNextFRFCFS(), gem5::curTick(), DPRINTF, gem5::MaxTick, MemCtrl(), and gem5::memory::MemInterface::nextBurstAt.

Referenced by chooseNext(), and gem5::memory::HeteroMemCtrl::chooseNextFRFCFS().

◆ doBurstAccess()

|

protectedvirtual |

Actually do the burst based on media specific access function.

Update bus statistics when complete.

- Parameters

-

mem_pkt The memory packet created from the outside world pkt mem_intr The memory interface to access

- Returns

- Time when the command was issued

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 796 of file mem_ctrl.cc.

References gem5::memory::MemPacket::addr, gem5::memory::MemInterface::commandOffset(), gem5::memory::MemInterface::doBurstAccess(), DPRINTF, gem5::memory::MemPacket::entryTime, gem5::memory::MemPacket::isRead(), MemCtrl(), gem5::memory::MemInterface::nextBurstAt, gem5::memory::MemInterface::nextReqTime, pruneBurstTick(), gem5::memory::MemInterface::readsThisTime, gem5::memory::MemPacket::readyTime, gem5::memory::MemPacket::requestorId(), selQueue(), gem5::memory::MemPacket::size, stats, and gem5::memory::MemInterface::writesThisTime.

Referenced by gem5::memory::HeteroMemCtrl::doBurstAccess(), and processNextReqEvent().

◆ drain()

|

overridevirtual |

Draining is the process of clearing out the states of SimObjects.These are the SimObjects that are partially executed or are partially in flight.

Draining is mostly used before forking and creating a check point.

This function notifies an object that it needs to drain its state.

If the object does not need further simulation to drain internal buffers, it returns DrainState::Drained and automatically switches to the Drained state. If the object needs more simulation, it returns DrainState::Draining and automatically enters the Draining state. Other return values are invalid.

- Note

- An object that has entered the Drained state can be disturbed by other objects in the system and consequently stop being drained. These perturbations are not visible in the drain state. The simulator therefore repeats the draining process until all objects return DrainState::Drained on the first call to drain().

- Returns

- DrainState::Drained if the object is drained at this point in time, DrainState::Draining if it needs further simulation.

Implements gem5::Drainable.

Definition at line 1426 of file mem_ctrl.cc.

References allIntfDrained(), gem5::curTick(), DPRINTF, gem5::Drained, gem5::Draining, dram, nextReqEvent, respQEmpty(), respQueue, gem5::memory::qos::MemCtrl::schedule(), gem5::memory::qos::MemCtrl::totalReadQueueSize, and gem5::memory::qos::MemCtrl::totalWriteQueueSize.

◆ drainResume()

|

overridevirtual |

Resume execution after a successful drain.

Reimplemented from gem5::Drainable.

Reimplemented in gem5::memory::HBMCtrl, and gem5::memory::HeteroMemCtrl.

Definition at line 1452 of file mem_ctrl.cc.

References dram, isTimingMode, gem5::System::isTimingMode(), startup(), and gem5::memory::qos::MemCtrl::system().

Referenced by gem5::memory::HBMCtrl::drainResume().

◆ getAddrRanges()

|

protectedvirtual |

Reimplemented in gem5::memory::HBMCtrl, and gem5::memory::HeteroMemCtrl.

Definition at line 1470 of file mem_ctrl.cc.

References dram.

◆ getBurstWindow()

Calculate burst window aligned tick.

- Parameters

-

cmd_tick Initial tick of command

- Returns

- burst window aligned tick

Definition at line 675 of file mem_ctrl.cc.

References commandWindow.

Referenced by gem5::memory::HBMCtrl::pruneColBurstTick(), gem5::memory::HBMCtrl::pruneRowBurstTick(), gem5::memory::HBMCtrl::verifyMultiCmd(), verifyMultiCmd(), gem5::memory::HBMCtrl::verifySingleCmd(), and verifySingleCmd().

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

gem5 has a request and response port interface. All memory objects are connected together via ports. These ports provide a rigid interface between these memory objects. These ports implement three different memory system modes: timing, atomic, and functional. The most important mode is the timing mode and here timing mode is used for conducting cycle-level timing experiments. The other modes are only used in special circumstances and should not be used to conduct cycle-level timing experiments. The other modes are only used in special circumstances. These ports allow SimObjects to communicate with each other.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from gem5::SimObject.

Definition at line 1407 of file mem_ctrl.cc.

References gem5::SimObject::getPort(), and port.

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 100 of file mem_ctrl.cc.

References fatal, gem5::Named::name(), and port.

Referenced by gem5::memory::HBMCtrl::init().

◆ inReadBusState()

| bool gem5::memory::MemCtrl::inReadBusState | ( | bool | next_state, |

| const MemInterface * | mem_intr ) const |

Check the current direction of the memory channel.

- Parameters

-

next_state Check either the current or next bus state

- Returns

- True when bus is currently in a read state

Definition at line 770 of file mem_ctrl.cc.

References gem5::memory::MemInterface::busState, gem5::memory::MemInterface::busStateNext, and gem5::memory::qos::MemCtrl::READ.

◆ inWriteBusState()

| bool gem5::memory::MemCtrl::inWriteBusState | ( | bool | next_state, |

| const MemInterface * | mem_intr ) const |

Check the current direction of the memory channel.

- Parameters

-

next_state Check either the current or next bus state

- Returns

- True when bus is currently in a write state

Definition at line 783 of file mem_ctrl.cc.

References gem5::memory::MemInterface::busState, gem5::memory::MemInterface::busStateNext, and gem5::memory::qos::MemCtrl::WRITE.

◆ memBusy()

|

protectedvirtual |

Checks if the memory interface is already busy.

- Parameters

-

mem_intr memory interface to check

- Returns

- a boolean indicating if memory is busy

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 838 of file mem_ctrl.cc.

References gem5::memory::MemInterface::isBusy(), gem5::memory::MemInterface::numWritesQueued, gem5::memory::MemInterface::readQueueSize, and gem5::memory::MemInterface::writeQueueSize.

Referenced by processNextReqEvent().

◆ minReadToWriteDataGap()

|

protectedvirtual |

Calculate the minimum delay used when scheduling a read-to-write transision.

- Parameters

-

return minimum delay

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 1158 of file mem_ctrl.cc.

References dram.

Referenced by processNextReqEvent().

◆ minWriteToReadDataGap()

|

protectedvirtual |

Calculate the minimum delay used when scheduling a write-to-read transision.

- Parameters

-

return minimum delay

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 1164 of file mem_ctrl.cc.

References dram.

Referenced by processNextReqEvent().

◆ nonDetermReads()

|

protectedvirtual |

Will access memory interface and select non-deterministic reads to issue.

- Parameters

-

mem_intr memory interface to use

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 866 of file mem_ctrl.cc.

References gem5::memory::MemInterface::chooseRead(), readQueue, and gem5::memory::MemInterface::readsWaitingToIssue().

Referenced by gem5::memory::HeteroMemCtrl::nonDetermReads(), and processNextReqEvent().

◆ nvmWriteBlock()

|

protectedvirtual |

Will check if all writes are for nvm interface and nvm's write resp queue is full.

The generic mem_intr is used as the same function can be called for a dram interface, in which case dram functions will eventually return false

- Parameters

-

mem_intr memory interface to use

- Returns

- a boolean showing if nvm is blocked with writes

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 859 of file mem_ctrl.cc.

References gem5::memory::MemInterface::numWritesQueued, gem5::memory::qos::MemCtrl::totalWriteQueueSize, and gem5::memory::MemInterface::writeRespQueueFull().

Referenced by gem5::memory::HeteroMemCtrl::nvmWriteBlock(), and processNextReqEvent().

◆ packetReady()

|

protectedvirtual |

Determine if there is a packet that can issue.

- Parameters

-

pkt The packet to evaluate

Definition at line 1152 of file mem_ctrl.cc.

References gem5::memory::MemInterface::burstReady().

Referenced by gem5::memory::HeteroMemCtrl::chooseNext(), and chooseNext().

◆ pktSizeCheck()

|

protectedvirtual |

Check if mem pkt's size is sane.

- Parameters

-

mem_pkt memory packet mem_intr memory interface

- Returns

- An address aligned to a memory burst

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 1176 of file mem_ctrl.cc.

References gem5::memory::MemInterface::bytesPerBurst(), and gem5::memory::MemPacket::size.

Referenced by processNextReqEvent().

◆ printQs()

|

protected |

Used for debugging to observe the contents of the queues.

Definition at line 382 of file mem_ctrl.cc.

References DPRINTF, MemCtrl(), readQueue, respQueue, and writeQueue.

◆ processNextReqEvent()

|

protectedvirtual |

Bunch of things requires to setup "events" in gem5 When event "respondEvent" occurs for example, the method processRespondEvent is called; no parameters are allowed in these methods.

Definition at line 881 of file mem_ctrl.cc.

References allIntfDrained(), burstAlign(), gem5::memory::MemInterface::busState, gem5::memory::MemInterface::busStateNext, gem5::memory::qos::MemCtrl::busStateNext, chooseNext(), gem5::curTick(), doBurstAccess(), DPRINTF, gem5::Draining, gem5::Drainable::drainState(), isInWriteQueue, gem5::memory::qos::MemCtrl::logResponse(), memBusy(), MemCtrl(), minReadsPerSwitch, minReadToWriteDataGap(), minWritesPerSwitch, minWriteToReadDataGap(), gem5::memory::MemInterface::nextReqTime, nonDetermReads(), gem5::memory::qos::MemCtrl::numPriorities(), nvmWriteBlock(), pktSizeCheck(), port, gem5::memory::qos::MemCtrl::READ, readQueue, gem5::memory::MemInterface::readQueueSize, gem5::memory::MemInterface::readsThisTime, gem5::memory::qos::MemCtrl::recordTurnaroundStats(), respQEmpty(), gem5::memory::qos::MemCtrl::schedule(), gem5::Event::scheduled(), gem5::memory::qos::MemCtrl::selectNextBusState(), gem5::Drainable::signalDrainDone(), stats, gem5::memory::qos::MemCtrl::totalReadQueueSize, gem5::memory::qos::MemCtrl::totalWriteQueueSize, gem5::memory::qos::MemCtrl::turnPolicy, gem5::memory::qos::MemCtrl::WRITE, writeBufferSize, writeHighThreshold, writeLowThreshold, writeQueue, gem5::memory::MemInterface::writeQueueSize, and gem5::memory::MemInterface::writesThisTime.

Referenced by gem5::memory::HBMCtrl::HBMCtrl(), and MemCtrl().

◆ processRespondEvent()

|

protectedvirtual |

Reimplemented in gem5::memory::HeteroMemCtrl.

Definition at line 488 of file mem_ctrl.cc.

References accessAndRespond(), allIntfDrained(), backendLatency, gem5::memory::BurstHelper::burstCount, gem5::memory::MemPacket::burstHelper, gem5::memory::BurstHelper::burstsServiced, gem5::memory::MemInterface::checkRefreshState(), gem5::curTick(), DPRINTF, gem5::Draining, gem5::Drainable::drainState(), frontendLatency, MemCtrl(), gem5::memory::MemPacket::pkt, port, gem5::memory::MemPacket::rank, gem5::memory::MemInterface::respondEvent(), gem5::memory::qos::MemCtrl::schedule(), gem5::Event::scheduled(), gem5::Drainable::signalDrainDone(), gem5::memory::qos::MemCtrl::totalReadQueueSize, and gem5::memory::qos::MemCtrl::totalWriteQueueSize.

Referenced by gem5::memory::HeteroMemCtrl::processRespondEvent().

◆ pruneBurstTick()

|

protectedvirtual |

Remove commands that have already issued from burstTicks.

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 662 of file mem_ctrl.cc.

References burstTicks, gem5::curTick(), DPRINTF, and MemCtrl().

Referenced by doBurstAccess().

◆ readQueueFull()

|

protected |

Check if the read queue has room for more entries.

- Parameters

-

pkt_count The number of entries needed in the read queue

- Returns

- true if read queue is full, false otherwise

Definition at line 166 of file mem_ctrl.cc.

References DPRINTF, MemCtrl(), readBufferSize, respQueue, and gem5::memory::qos::MemCtrl::totalReadQueueSize.

Referenced by addToReadQueue(), gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

◆ recvAtomic()

Reimplemented in gem5::memory::HBMCtrl, and gem5::memory::HeteroMemCtrl.

Definition at line 125 of file mem_ctrl.cc.

References dram, gem5::Packet::getAddr(), panic, gem5::Packet::print(), and recvAtomicLogic().

Referenced by recvAtomicBackdoor().

◆ recvAtomicBackdoor()

|

protectedvirtual |

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 158 of file mem_ctrl.cc.

References dram, and recvAtomic().

◆ recvAtomicLogic()

|

protected |

Definition at line 136 of file mem_ctrl.cc.

References gem5::memory::AbstractMemory::access(), gem5::memory::MemInterface::accessLatency(), gem5::Packet::cacheResponding(), gem5::Packet::cmdString(), DPRINTF, gem5::Packet::getAddr(), gem5::Packet::hasData(), MemCtrl(), and panic_if.

Referenced by gem5::memory::HBMCtrl::recvAtomic(), gem5::memory::HeteroMemCtrl::recvAtomic(), and recvAtomic().

◆ recvFunctional()

|

protectedvirtual |

Reimplemented in gem5::memory::HBMCtrl, and gem5::memory::HeteroMemCtrl.

Definition at line 1375 of file mem_ctrl.cc.

References dram, panic_if, gem5::Packet::print(), and recvFunctionalLogic().

◆ recvFunctionalLogic()

|

protected |

Definition at line 1395 of file mem_ctrl.cc.

References gem5::AddrRange::contains(), gem5::memory::AbstractMemory::functionalAccess(), gem5::Packet::getAddr(), and gem5::memory::AbstractMemory::getAddrRange().

Referenced by gem5::memory::HBMCtrl::recvFunctional(), gem5::memory::HeteroMemCtrl::recvFunctional(), and recvFunctional().

◆ recvMemBackdoorReq()

|

protectedvirtual |

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 1384 of file mem_ctrl.cc.

References dram, panic_if, gem5::MemBackdoorReq::range(), gem5::AddrRange::start(), and gem5::AddrRange::to_string().

◆ recvTimingReq()

|

protectedvirtual |

Reimplemented in gem5::memory::HBMCtrl, and gem5::memory::HeteroMemCtrl.

Definition at line 407 of file mem_ctrl.cc.

References addToReadQueue(), addToWriteQueue(), gem5::Packet::cacheResponding(), gem5::Packet::cmdString(), gem5::curTick(), gem5::divCeil(), DPRINTF, dram, gem5::Packet::getAddr(), gem5::Packet::getSize(), gem5::Packet::isRead(), gem5::Packet::isWrite(), MemCtrl(), nextReqEvent, gem5::ArmISA::offset, panic_if, prevArrival, gem5::Packet::print(), gem5::memory::qos::MemCtrl::qosSchedule(), readQueue, readQueueFull(), retryRdReq, retryWrReq, gem5::memory::qos::MemCtrl::schedule(), stats, writeQueue, and writeQueueFull().

◆ requestEventScheduled()

|

inlinevirtual |

Is there a read/write burst Event scheduled?

- Returns

- true if event is scheduled

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 738 of file mem_ctrl.hh.

References nextReqEvent.

Referenced by gem5::memory::HBMCtrl::requestEventScheduled().

◆ respondEventScheduled()

|

inlinevirtual |

Is there a respondEvent scheduled?

- Returns

- true if event is scheduled

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 727 of file mem_ctrl.hh.

References respondEvent.

Referenced by gem5::memory::HBMCtrl::respondEventScheduled().

◆ respQEmpty()

|

inlineprotectedvirtual |

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 641 of file mem_ctrl.hh.

References respQueue.

Referenced by drain(), and processNextReqEvent().

◆ restartScheduler()

|

inlinevirtual |

restart the controller This can be used by interfaces to restart the scheduler after maintainence commands complete

- Parameters

-

Tick to schedule next event pseudo_channel pseudo channel number for which scheduler needs to restart, will always be 0 for controllers which control only a single channel

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 753 of file mem_ctrl.hh.

References nextReqEvent, gem5::memory::qos::MemCtrl::schedule(), and gem5::Clocked::tick.

Referenced by gem5::memory::HBMCtrl::restartScheduler().

◆ selQueue()

|

inlineprotected |

Select either the read or write queue.

- Parameters

-

is_read The current burst is a read, select read queue

- Returns

- a reference to the appropriate queue

Definition at line 636 of file mem_ctrl.hh.

References readQueue, and writeQueue.

Referenced by doBurstAccess().

◆ startup()

|

overridevirtual |

startup() is the final initialization call before simulation.

All state is initialized (including unserialized state, if any, such as the curTick() value), so this is the appropriate place to schedule initial event(s) for objects that need them.

Reimplemented from gem5::SimObject.

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 110 of file mem_ctrl.cc.

References gem5::curTick(), dram, isTimingMode, gem5::System::isTimingMode(), and gem5::memory::qos::MemCtrl::system().

Referenced by gem5::memory::HeteroMemCtrl::drainResume(), drainResume(), and gem5::memory::HBMCtrl::startup().

◆ verifyMultiCmd()

|

virtual |

Check for command bus contention for multi-cycle (2 currently) command.

If there is contention, shift command(s) to next burst. Check verifies that the commands issued per burst is less than a defined max number, maxCommandsPerWindow. Therefore, contention per cycle is not verified and instead is done based on a burst window.

- Parameters

-

cmd_tick Initial tick of command, to be verified max_multi_cmd_split Maximum delay between commands max_cmds_per_burst Number of commands that can issue in a burst window

- Returns

- tick for command issue without contention

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 706 of file mem_ctrl.cc.

References burstTicks, commandWindow, DPRINTF, getBurstWindow(), and MemCtrl().

◆ verifySingleCmd()

|

virtual |

Check for command bus contention for single cycle command.

If there is contention, shift command to next burst. Check verifies that the commands issued per burst is less than a defined max number, maxCommandsPerWindow. Therefore, contention per cycle is not verified and instead is done based on a burst window.

- Parameters

-

cmd_tick Initial tick of command, to be verified max_cmds_per_burst Number of commands that can issue in a burst window

- Returns

- tick for command issue without contention

Reimplemented in gem5::memory::HBMCtrl.

Definition at line 683 of file mem_ctrl.cc.

References burstTicks, commandWindow, DPRINTF, getBurstWindow(), and MemCtrl().

◆ writeQueueFull()

|

protected |

Check if the write queue has room for more entries.

- Parameters

-

pkt_count The number of entries needed in the write queue

- Returns

- true if write queue is full, false otherwise

Definition at line 178 of file mem_ctrl.cc.

References DPRINTF, MemCtrl(), gem5::memory::qos::MemCtrl::totalWriteQueueSize, and writeBufferSize.

Referenced by gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

Member Data Documentation

◆ backendLatency

|

protected |

Pipeline latency of the backend and PHY.

Along with the frontend contribution, this latency is added to reads serviced by the memory.

Definition at line 539 of file mem_ctrl.hh.

Referenced by processRespondEvent().

◆ burstTicks

|

protected |

Holds count of commands issued in burst window starting at defined Tick.

This is used to ensure that the command bandwidth does not exceed the allowable media constraints.

Definition at line 499 of file mem_ctrl.hh.

Referenced by pruneBurstTick(), verifyMultiCmd(), and verifySingleCmd().

◆ commandWindow

|

protected |

Length of a command window, used to check command bandwidth.

Definition at line 545 of file mem_ctrl.hh.

Referenced by getBurstWindow(), gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), gem5::memory::HBMCtrl::verifyMultiCmd(), verifyMultiCmd(), gem5::memory::HBMCtrl::verifySingleCmd(), and verifySingleCmd().

◆ dram

|

protected |

- * Create pointer to interface of the actual memory media when connected

Definition at line 504 of file mem_ctrl.hh.

Referenced by gem5::memory::HeteroMemCtrl::allIntfDrained(), allIntfDrained(), gem5::memory::HeteroMemCtrl::chooseNext(), gem5::memory::HeteroMemCtrl::chooseNextFRFCFS(), gem5::memory::HeteroMemCtrl::doBurstAccess(), gem5::memory::HeteroMemCtrl::drain(), drain(), gem5::memory::HeteroMemCtrl::drainResume(), drainResume(), gem5::memory::HeteroMemCtrl::getAddrRanges(), getAddrRanges(), gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), MemCtrl(), gem5::memory::HeteroMemCtrl::minReadToWriteDataGap(), minReadToWriteDataGap(), gem5::memory::HeteroMemCtrl::minWriteToReadDataGap(), minWriteToReadDataGap(), gem5::memory::HeteroMemCtrl::processRespondEvent(), gem5::memory::HeteroMemCtrl::recvAtomic(), recvAtomic(), recvAtomicBackdoor(), gem5::memory::HeteroMemCtrl::recvFunctional(), recvFunctional(), recvMemBackdoorReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), recvTimingReq(), and startup().

◆ frontendLatency

|

protected |

Pipeline latency of the controller frontend.

The frontend contribution is added to writes (that complete when they are in the write buffer) and reads that are serviced the write buffer.

Definition at line 532 of file mem_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), and processRespondEvent().

◆ isInWriteQueue

|

protected |

To avoid iterating over the write queue to check for overlapping transactions, maintain a set of burst addresses that are currently queued.

Since we merge writes to the same location we never have more than one address to the same burst address.

Definition at line 482 of file mem_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), and processNextReqEvent().

◆ isTimingMode

|

protected |

Remember if the memory system is in timing mode.

Definition at line 288 of file mem_ctrl.hh.

Referenced by gem5::memory::HBMCtrl::drainResume(), gem5::memory::HeteroMemCtrl::drainResume(), drainResume(), MemCtrl(), gem5::memory::HBMCtrl::startup(), and startup().

◆ memSchedPolicy

|

protected |

Memory controller configuration initialized based on parameter values.

Definition at line 525 of file mem_ctrl.hh.

Referenced by gem5::memory::HeteroMemCtrl::chooseNext(), and chooseNext().

◆ minReadsPerSwitch

|

protected |

Definition at line 519 of file mem_ctrl.hh.

Referenced by processNextReqEvent().

◆ minWritesPerSwitch

|

protected |

Definition at line 518 of file mem_ctrl.hh.

Referenced by processNextReqEvent().

◆ nextBurstAt

|

protected |

Till when must we wait before issuing next RD/WR burst?

Definition at line 550 of file mem_ctrl.hh.

◆ nextReqEvent

|

protected |

Definition at line 307 of file mem_ctrl.hh.

Referenced by gem5::memory::HeteroMemCtrl::drain(), drain(), MemCtrl(), gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), recvTimingReq(), requestEventScheduled(), and restartScheduler().

◆ nextReqTime

|

protected |

The soonest you have to start thinking about the next request is the longest access time that can occur before nextBurstAt.

Assuming you need to precharge, open a new row, and access, it is tRP + tRCD + tCL.

Definition at line 560 of file mem_ctrl.hh.

◆ pendingDelete

|

protected |

Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call.

Definition at line 628 of file mem_ctrl.hh.

Referenced by accessAndRespond().

◆ port

|

protected |

Our incoming port, for a multi-ported controller add a crossbar in front of it.

Definition at line 283 of file mem_ctrl.hh.

Referenced by accessAndRespond(), getPort(), init(), MemCtrl(), processNextReqEvent(), and processRespondEvent().

◆ prevArrival

|

protected |

Definition at line 552 of file mem_ctrl.hh.

Referenced by gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

◆ readBufferSize

|

protected |

The following are basic design parameters of the memory controller, and are initialized based on parameter values.

The rowsPerBank is determined based on the capacity, number of ranks and banks, the burst size, and the row buffer size.

Definition at line 514 of file mem_ctrl.hh.

Referenced by gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), readQueueFull(), gem5::memory::HBMCtrl::readQueueFullPC0(), and gem5::memory::HBMCtrl::readQueueFullPC1().

◆ readQueue

|

protected |

The controller's main read and write queues, with support for QoS reordering.

Definition at line 472 of file mem_ctrl.hh.

Referenced by addToReadQueue(), gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), nonDetermReads(), printQs(), processNextReqEvent(), gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), recvTimingReq(), and selQueue().

◆ respondEvent

|

protected |

Definition at line 313 of file mem_ctrl.hh.

Referenced by MemCtrl(), and respondEventScheduled().

◆ respQueue

|

protected |

Response queue where read packets wait after we're done working with them, but it's not time to send the response yet.

The responses are stored separately mostly to keep the code clean and help with events scheduling. For all logical purposes such as sizing the read queue, this and the main read queue need to be added together.

Definition at line 492 of file mem_ctrl.hh.

Referenced by addToReadQueue(), gem5::memory::HeteroMemCtrl::drain(), drain(), MemCtrl(), printQs(), readQueueFull(), gem5::memory::HBMCtrl::readQueueFullPC0(), gem5::memory::HBMCtrl::respQEmpty(), and respQEmpty().

◆ retryRdReq

|

protected |

Remember if we have to retry a request when available.

Definition at line 293 of file mem_ctrl.hh.

Referenced by MemCtrl(), gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

◆ retryWrReq

|

protected |

Definition at line 294 of file mem_ctrl.hh.

Referenced by MemCtrl(), gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

◆ stats

|

protected |

Definition at line 622 of file mem_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), doBurstAccess(), processNextReqEvent(), gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), and recvTimingReq().

◆ writeBufferSize

|

protected |

Definition at line 515 of file mem_ctrl.hh.

Referenced by addToWriteQueue(), gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), processNextReqEvent(), writeQueueFull(), gem5::memory::HBMCtrl::writeQueueFullPC0(), and gem5::memory::HBMCtrl::writeQueueFullPC1().

◆ writeHighThreshold

|

protected |

Definition at line 516 of file mem_ctrl.hh.

Referenced by gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), and processNextReqEvent().

◆ writeLowThreshold

|

protected |

Definition at line 517 of file mem_ctrl.hh.

Referenced by gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), and processNextReqEvent().

◆ writeQueue

|

protected |

Definition at line 473 of file mem_ctrl.hh.

Referenced by addToReadQueue(), addToWriteQueue(), gem5::memory::HeteroMemCtrl::HeteroMemCtrl(), printQs(), processNextReqEvent(), gem5::memory::HBMCtrl::recvTimingReq(), gem5::memory::HeteroMemCtrl::recvTimingReq(), recvTimingReq(), and selQueue().

The documentation for this class was generated from the following files:

- mem/mem_ctrl.hh

- mem/mem_ctrl.cc

Generated on Sat Oct 18 2025 08:06:59 for gem5 by doxygen 1.14.0