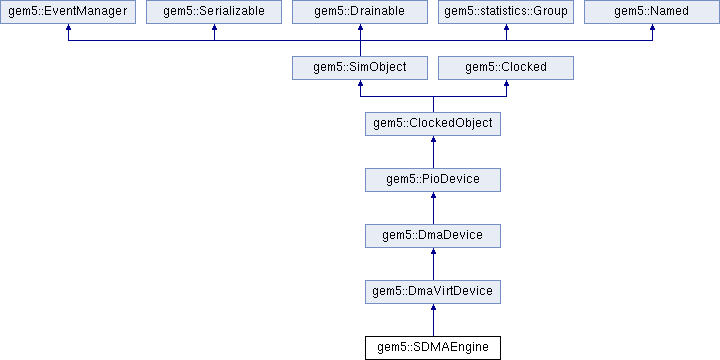

System DMA Engine class for AMD dGPU. More...

#include <sdma_engine.hh>

Classes | |

| class | SDMAQueue |

Public Member Functions | |

| SDMAEngine (const SDMAEngineParams &p) | |

| void | setGPUDevice (AMDGPUDevice *gpu_device) |

| void | setId (int _id) |

| int | getId () const |

| int | getIHClientId (int _id) |

| Returns the client id for the Interrupt Handler. | |

| Addr | getGARTAddr (Addr addr) const |

| Methods for translation. | |

| TranslationGenPtr | translate (Addr vaddr, Addr size) override |

| GPUController will perform DMA operations on VAs, and because page faults are not currently supported for GPUController, we must be able to find the pages mapped for the process. | |

| Addr | getDeviceAddress (Addr raw_addr) |

| Translate an address in an SDMA packet. | |

| Tick | write (PacketPtr pkt) override |

| Inherited methods. | |

| Tick | read (PacketPtr pkt) override |

| Pure virtual function that the device must implement. | |

| AddrRangeList | getAddrRanges () const override |

| Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| void | processGfx (Addr wptrOffset) |

| Given a new write ptr offset, communicated to the GPU through a doorbell write, the SDMA engine processes the page, gfx, rlc0, or rlc1 queue. | |

| void | processPage (Addr wptrOffset) |

| void | processRLC (Addr doorbellOffset, Addr wptrOffset) |

| void | decodeNext (SDMAQueue *q) |

| This method checks read and write pointers and starts decoding packets if the read pointer is less than the write pointer. | |

| void | decodeHeader (SDMAQueue *q, uint32_t data) |

| Reads the first DW (32 bits) (i.e., header) of an SDMA packet, which encodes the opcode and sub-opcode of the packet. | |

| void | write (SDMAQueue *q, sdmaWrite *pkt) |

| Methods that implement processing of SDMA packets. | |

| void | writeReadData (SDMAQueue *q, sdmaWrite *pkt, uint32_t *dmaBuffer) |

| void | writeDone (SDMAQueue *q, sdmaWrite *pkt, uint32_t *dmaBuffer) |

| void | writeCleanup (uint32_t *dmaBuffer) |

| void | copy (SDMAQueue *q, sdmaCopy *pkt) |

| void | copyReadData (SDMAQueue *q, sdmaCopy *pkt, uint8_t *dmaBuffer) |

| void | copyDone (SDMAQueue *q, sdmaCopy *pkt, uint8_t *dmaBuffer) |

| void | copyCleanup (uint8_t *dmaBuffer) |

| void | indirectBuffer (SDMAQueue *q, sdmaIndirectBuffer *pkt) |

| void | fence (SDMAQueue *q, sdmaFence *pkt) |

| void | fenceDone (SDMAQueue *q, sdmaFence *pkt) |

| void | trap (SDMAQueue *q, sdmaTrap *pkt) |

| void | srbmWrite (SDMAQueue *q, uint32_t header, sdmaSRBMWrite *pkt) |

| void | pollRegMem (SDMAQueue *q, uint32_t header, sdmaPollRegMem *pkt) |

| Implements a poll reg/mem packet that polls an SRBM register or a memory location, compares the retrieved value with a reference value and if unsuccessfull it retries indefinitely or for a limited number of times. | |

| void | pollRegMemRead (SDMAQueue *q, uint32_t header, sdmaPollRegMem *pkt, uint32_t dma_buffer, int count) |

| bool | pollRegMemFunc (uint32_t value, uint32_t reference, uint32_t func) |

| void | ptePde (SDMAQueue *q, sdmaPtePde *pkt) |

| void | ptePdeDone (SDMAQueue *q, sdmaPtePde *pkt, uint64_t *dmaBuffer) |

| void | ptePdeCleanup (uint64_t *dmaBuffer) |

| void | atomic (SDMAQueue *q, uint32_t header, sdmaAtomic *pkt) |

| void | atomicData (SDMAQueue *q, uint32_t header, sdmaAtomic *pkt, uint64_t *dmaBuffer) |

| void | atomicDone (SDMAQueue *q, uint32_t header, sdmaAtomic *pkt, uint64_t *dmaBuffer) |

| void | constFill (SDMAQueue *q, sdmaConstFill *pkt, uint32_t header) |

| void | constFillDone (SDMAQueue *q, sdmaConstFill *pkt, uint8_t *fill_data) |

| Addr | getMmioBase () |

| Methods for getting SDMA MMIO base address and size. | |

| Addr | getMmioSize () |

| uint64_t | getGfxBase () |

| Methods for getting the values of SDMA MMIO registers. | |

| uint64_t | getGfxRptr () |

| uint64_t | getGfxDoorbell () |

| uint64_t | getGfxDoorbellOffset () |

| uint64_t | getGfxWptr () |

| uint64_t | getPageBase () |

| uint64_t | getPageRptr () |

| uint64_t | getPageDoorbell () |

| uint64_t | getPageDoorbellOffset () |

| uint64_t | getPageWptr () |

| void | writeMMIO (PacketPtr pkt, Addr mmio_offset) |

| Methods for setting the values of SDMA MMIO registers. | |

| void | setGfxBaseLo (uint32_t data) |

| void | setGfxBaseHi (uint32_t data) |

| void | setGfxRptrLo (uint32_t data) |

| void | setGfxRptrHi (uint32_t data) |

| void | setGfxDoorbellLo (uint32_t data) |

| void | setGfxDoorbellHi (uint32_t data) |

| void | setGfxDoorbellOffsetLo (uint32_t data) |

| void | setGfxDoorbellOffsetHi (uint32_t data) |

| void | setGfxSize (uint32_t data) |

| void | setGfxWptrLo (uint32_t data) |

| void | setGfxWptrHi (uint32_t data) |

| void | setPageBaseLo (uint32_t data) |

| void | setPageBaseHi (uint32_t data) |

| void | setPageRptrLo (uint32_t data) |

| void | setPageRptrHi (uint32_t data) |

| void | setPageDoorbellLo (uint32_t data) |

| void | setPageDoorbellHi (uint32_t data) |

| void | setPageDoorbellOffsetLo (uint32_t data) |

| void | setPageDoorbellOffsetHi (uint32_t data) |

| void | setPageSize (uint32_t data) |

| void | setPageWptrLo (uint32_t data) |

| void | setPageWptrHi (uint32_t data) |

| void | registerRLCQueue (Addr doorbell, Addr mqdAddr, SDMAQueueDesc *mqd, bool isStatic) |

| Methods for RLC queues. | |

| void | unregisterRLCQueue (Addr doorbell, bool unmap_static) |

| void | deallocateRLCQueues (bool unmap_static) |

| Public Member Functions inherited from gem5::DmaVirtDevice | |

| DmaVirtDevice (const Params &p) | |

| virtual | ~DmaVirtDevice () |

| void | dmaReadVirt (Addr host_addr, unsigned size, DmaCallback *cb, void *data, Tick delay=0) |

| Initiate a DMA read from virtual address host_addr. | |

| void | dmaWriteVirt (Addr host_addr, unsigned size, DmaCallback *b, void *data, Tick delay=0) |

| Initiate a DMA write from virtual address host_addr. | |

| void | dmaVirt (DmaFnPtr dmaFn, Addr host_addr, unsigned size, DmaCallback *cb, void *data, Tick delay=0) |

| Initiate a call to DmaDevice using DmaFnPtr do a DMA starting from virtual address host_addr for size number of bytes on the data. | |

| Public Member Functions inherited from gem5::DmaDevice | |

| DmaDevice (const Params &p) | |

| virtual | ~DmaDevice ()=default |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaWrite (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, std::optional< uint32_t > sid, std::optional< uint32_t > ssid, Tick delay=0) |

| void | dmaRead (Addr addr, int size, Event *event, uint8_t *data, Tick delay=0) |

| bool | dmaPending () const |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Addr | cacheBlockSize () const |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::PioDevice | |

| PioDevice (const Params &p) | |

| virtual | ~PioDevice () |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Public Attributes | |

| int | cur_vmid = 0 |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Private Types | |

| enum | SDMAType { SDMAGfx , SDMAPage } |

Private Member Functions | |

| void | processRLC0 (Addr wptrOffset) |

| void | processRLC1 (Addr wptrOffset) |

Private Attributes | |

| int | id |

| SDMAQueue | gfx |

| Each SDMAEngine processes four queues: paging, gfx, rlc0, and rlc1, where RLC stands for Run List Controller. | |

| SDMAQueue | page |

| SDMAQueue | gfxIb |

| SDMAQueue | pageIb |

| SDMAQueue | rlc0 |

| SDMAQueue | rlc0Ib |

| SDMAQueue | rlc1 |

| SDMAQueue | rlc1Ib |

| uint64_t | gfxBase |

| uint64_t | gfxRptr |

| uint64_t | gfxDoorbell |

| uint64_t | gfxDoorbellOffset |

| uint64_t | gfxWptr |

| uint64_t | pageBase |

| uint64_t | pageRptr |

| uint64_t | pageDoorbell |

| uint64_t | pageDoorbellOffset |

| uint64_t | pageWptr |

| AMDGPUDevice * | gpuDevice |

| VegaISA::Walker * | walker |

| std::array< Addr, 2 > | rlcInfo {} |

| Addr | mmioBase = 0 |

| Addr | mmioSize = 0 |

Additional Inherited Members | |

| Public Types inherited from gem5::DmaVirtDevice | |

| typedef void(DmaDevice::* | DmaFnPtr) (Addr, int, Event *, uint8_t *, Tick) |

| Public Types inherited from gem5::DmaDevice | |

| typedef DmaDeviceParams | Params |

| Public Types inherited from gem5::PioDevice | |

| using | Params = PioDeviceParams |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

| Protected Attributes inherited from gem5::DmaDevice | |

| DmaPort | dmaPort |

| Protected Attributes inherited from gem5::PioDevice | |

| System * | sys |

| PioPort< PioDevice > | pioPort |

| The pioPort that handles the requests for us and provides us requests that it sees. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Detailed Description

System DMA Engine class for AMD dGPU.

Definition at line 48 of file sdma_engine.hh.

Member Enumeration Documentation

◆ SDMAType

|

private |

| Enumerator | |

|---|---|

| SDMAGfx | |

| SDMAPage | |

Definition at line 50 of file sdma_engine.hh.

Constructor & Destructor Documentation

◆ SDMAEngine()

| gem5::SDMAEngine::SDMAEngine | ( | const SDMAEngineParams & | p | ) |

Definition at line 49 of file sdma_engine.cc.

References gem5::DmaVirtDevice::DmaVirtDevice(), gfx, gfxBase, gfxDoorbell, gfxDoorbellOffset, gfxIb, gfxRptr, gfxWptr, gpuDevice, id, mmioBase, mmioSize, gem5::MipsISA::p, page, pageBase, pageDoorbell, pageDoorbellOffset, pageIb, pageRptr, pageWptr, rlc0, rlc0Ib, rlc1, rlc1Ib, SDMAGfx, SDMAPage, and walker.

Referenced by atomic(), atomicData(), atomicDone(), constFill(), constFillDone(), copy(), copyDone(), copyReadData(), decodeHeader(), decodeNext(), fenceDone(), getDeviceAddress(), pollRegMem(), pollRegMemRead(), ptePde(), ptePdeDone(), registerRLCQueue(), srbmWrite(), trap(), unregisterRLCQueue(), write(), writeDone(), writeMMIO(), and writeReadData().

Member Function Documentation

◆ atomic()

| void gem5::SDMAEngine::atomic | ( | SDMAQueue * | q, |

| uint32_t | header, | ||

| sdmaAtomic * | pkt ) |

Definition at line 1117 of file sdma_engine.cc.

References gem5::GEM5_PACKED::addr, atomicData(), gem5::GEM5_PACKED::cmpData, gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, header, gem5::GEM5_PACKED::loop, gem5::GEM5_PACKED::loopInt, gem5::GEM5_PACKED::opcode, gem5::GEM5_PACKED::ordinal, gem5::ArmISA::q, SDMAEngine(), and gem5::GEM5_PACKED::srcData.

◆ atomicData()

| void gem5::SDMAEngine::atomicData | ( | SDMAQueue * | q, |

| uint32_t | header, | ||

| sdmaAtomic * | pkt, | ||

| uint64_t * | dmaBuffer ) |

Definition at line 1137 of file sdma_engine.cc.

References gem5::GEM5_PACKED::addr, atomicDone(), gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, header, gem5::GEM5_PACKED::opcode, gem5::GEM5_PACKED::ordinal, panic, gem5::ArmISA::q, gem5::SDMA_ATOMIC_ADD64, SDMAEngine(), and gem5::GEM5_PACKED::srcData.

Referenced by atomic().

◆ atomicDone()

| void gem5::SDMAEngine::atomicDone | ( | SDMAQueue * | q, |

| uint32_t | header, | ||

| sdmaAtomic * | pkt, | ||

| uint64_t * | dmaBuffer ) |

Definition at line 1167 of file sdma_engine.cc.

References gem5::GEM5_PACKED::addr, decodeNext(), DPRINTF, header, gem5::GEM5_PACKED::opcode, gem5::GEM5_PACKED::ordinal, gem5::ArmISA::q, and SDMAEngine().

Referenced by atomicData().

◆ constFill()

| void gem5::SDMAEngine::constFill | ( | SDMAQueue * | q, |

| sdmaConstFill * | pkt, | ||

| uint32_t | header ) |

Definition at line 1182 of file sdma_engine.cc.

References gem5::GEM5_PACKED::addr, AMDGPU_MMHUB_PAGE_SIZE, constFillDone(), gem5::GEM5_PACKED::count, gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, gem5::GEM5_PACKED::fillsize, getDeviceAddress(), gpuDevice, header, name(), gem5::GEM5_PACKED::ordinal, gem5::ArmISA::q, SDMAEngine(), gem5::GEM5_PACKED::srcData, and gem5::GEM5_PACKED::sw.

Referenced by decodeHeader().

◆ constFillDone()

| void gem5::SDMAEngine::constFillDone | ( | SDMAQueue * | q, |

| sdmaConstFill * | pkt, | ||

| uint8_t * | fill_data ) |

Definition at line 1235 of file sdma_engine.cc.

References gem5::GEM5_PACKED::addr, decodeNext(), DPRINTF, gem5::ArmISA::q, and SDMAEngine().

Referenced by constFill().

◆ copy()

Definition at line 691 of file sdma_engine.cc.

References AMDGPU_MMHUB_PAGE_SIZE, copyReadData(), gem5::GEM5_PACKED::count, gem5::GEM5_PACKED::dest, gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, getDeviceAddress(), getGARTAddr(), gpuDevice, name(), gem5::ArmISA::q, SDMAEngine(), and gem5::GEM5_PACKED::source.

Referenced by decodeHeader().

◆ copyCleanup()

| void gem5::SDMAEngine::copyCleanup | ( | uint8_t * | dmaBuffer | ) |

Definition at line 822 of file sdma_engine.cc.

Referenced by copyDone().

◆ copyDone()

Definition at line 800 of file sdma_engine.cc.

References copyCleanup(), gem5::GEM5_PACKED::count, gem5::curTick(), decodeNext(), gem5::GEM5_PACKED::dest, DPRINTF, gpuDevice, name(), gem5::ArmISA::q, gem5::EventManager::schedule(), SDMAEngine(), and warn_once.

Referenced by copyReadData().

◆ copyReadData()

Definition at line 739 of file sdma_engine.cc.

References AMDGPU_MMHUB_PAGE_SIZE, copyDone(), gem5::GEM5_PACKED::count, gem5::GEM5_PACKED::dest, gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, getDeviceAddress(), gpuDevice, gem5::ArmISA::i, name(), gem5::ArmISA::q, and SDMAEngine().

Referenced by copy().

◆ deallocateRLCQueues()

| void gem5::SDMAEngine::deallocateRLCQueues | ( | bool | unmap_static | ) |

Definition at line 283 of file sdma_engine.cc.

References rlcInfo, and unregisterRLCQueue().

◆ decodeHeader()

| void gem5::SDMAEngine::decodeHeader | ( | SDMAQueue * | q, |

| uint32_t | data ) |

Reads the first DW (32 bits) (i.e., header) of an SDMA packet, which encodes the opcode and sub-opcode of the packet.

It also creates an SDMA packet object and calls the associated processing function.

Definition at line 393 of file sdma_engine.cc.

References gem5::ArmISA::atomic, gem5::bits(), constFill(), copy(), decodeNext(), gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, fence(), header, gem5::ArmISA::i, indirectBuffer(), gem5::ArmISA::opcode, panic, pollRegMem(), ptePde(), gem5::ArmISA::q, SDMA_OP_ATOMIC, SDMA_OP_COND_EXE, SDMA_OP_CONST_FILL, SDMA_OP_COPY, SDMA_OP_DUMMY_TRAP, SDMA_OP_FENCE, SDMA_OP_INDIRECT, SDMA_OP_NOP, SDMA_OP_POLL_REGMEM, SDMA_OP_PRE_EXE, SDMA_OP_PTEPDE, SDMA_OP_SEM, SDMA_OP_SRBM_WRITE, SDMA_OP_TIMESTAMP, SDMA_OP_TRAP, SDMA_OP_WRITE, SDMA_SUBOP_COPY_DIRTY_PAGE, SDMA_SUBOP_COPY_LINEAR, SDMA_SUBOP_COPY_LINEAR_PHY, SDMA_SUBOP_COPY_LINEAR_SUB_WIND, SDMA_SUBOP_COPY_SOA, SDMA_SUBOP_COPY_T2T_SUB_WIND, SDMA_SUBOP_COPY_TILED, SDMA_SUBOP_COPY_TILED_SUB_WIND, SDMA_SUBOP_POLL_DBIT_WRITE_MEM, SDMA_SUBOP_POLL_MEM_VERIFY, SDMA_SUBOP_POLL_REG_WRITE_MEM, SDMA_SUBOP_PTEPDE_COPY, SDMA_SUBOP_PTEPDE_COPY_BACKWARDS, SDMA_SUBOP_PTEPDE_GEN, SDMA_SUBOP_PTEPDE_RMW, SDMA_SUBOP_TIMESTAMP_GET, SDMA_SUBOP_TIMESTAMP_GET_GLOBAL, SDMA_SUBOP_TIMESTAMP_SET, SDMA_SUBOP_WRITE_LINEAR, SDMA_SUBOP_WRITE_TILED, SDMAEngine(), srbmWrite(), trap(), warn, and write().

Referenced by decodeNext().

◆ decodeNext()

| void gem5::SDMAEngine::decodeNext | ( | SDMAQueue * | q | ) |

This method checks read and write pointers and starts decoding packets if the read pointer is less than the write pointer.

It also marks a queue a being currently processing, in case the doorbell is rung again, the newly enqueued packets will be decoded once the currently processing once are finished. This is achieved by calling decodeNext once an entire SDMA packet has been processed.

Definition at line 357 of file sdma_engine.cc.

References cur_vmid, decodeHeader(), decodeNext(), gem5::DmaVirtDevice::dmaReadVirt(), gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, header, gem5::ArmISA::q, and SDMAEngine().

Referenced by atomicDone(), constFillDone(), copyDone(), decodeHeader(), decodeNext(), fenceDone(), indirectBuffer(), pollRegMem(), pollRegMemRead(), processGfx(), processPage(), processRLC0(), processRLC1(), ptePdeDone(), srbmWrite(), trap(), and writeDone().

◆ fence()

Definition at line 848 of file sdma_engine.cc.

References gem5::GEM5_PACKED::data, gem5::GEM5_PACKED::dest, gem5::DmaVirtDevice::dmaWriteVirt(), fenceDone(), getGARTAddr(), and gem5::ArmISA::q.

Referenced by decodeHeader().

◆ fenceDone()

Definition at line 863 of file sdma_engine.cc.

References gem5::GEM5_PACKED::data, decodeNext(), gem5::GEM5_PACKED::dest, DPRINTF, gem5::ArmISA::q, and SDMAEngine().

Referenced by fence().

◆ getAddrRanges()

|

overridevirtual |

Every PIO device is obliged to provide an implementation that returns the address ranges the device responds to.

- Returns

- a list of non-overlapping address ranges

Implements gem5::PioDevice.

Definition at line 1245 of file sdma_engine.cc.

◆ getDeviceAddress()

Translate an address in an SDMA packet.

Return the device address if address in the packet is on the device and 0 if the the address in the packet is on the host/system memory.

Definition at line 120 of file sdma_engine.cc.

References cur_vmid, DPRINTF, gpuDevice, SDMAEngine(), and translate().

Referenced by constFill(), copy(), and copyReadData().

◆ getGARTAddr()

Methods for translation.

Definition at line 110 of file sdma_engine.cc.

References gem5::X86ISA::addr, gem5::bits(), and gpuDevice.

Referenced by copy(), fence(), indirectBuffer(), pollRegMem(), ptePde(), setGfxRptrHi(), setGfxRptrLo(), setPageRptrHi(), setPageRptrLo(), and writeReadData().

◆ getGfxBase()

|

inline |

Methods for getting the values of SDMA MMIO registers.

Definition at line 275 of file sdma_engine.hh.

References gfxBase.

◆ getGfxDoorbell()

|

inline |

◆ getGfxDoorbellOffset()

|

inline |

Definition at line 278 of file sdma_engine.hh.

References gfxDoorbellOffset.

Referenced by writeMMIO().

◆ getGfxRptr()

|

inline |

Definition at line 276 of file sdma_engine.hh.

References gfxRptr.

◆ getGfxWptr()

|

inline |

Definition at line 279 of file sdma_engine.hh.

References gfxWptr.

◆ getId()

|

inline |

◆ getIHClientId()

| int gem5::SDMAEngine::getIHClientId | ( | int | _id | ) |

Returns the client id for the Interrupt Handler.

Definition at line 85 of file sdma_engine.cc.

References panic, gem5::SOC15_IH_CLIENTID_SDMA0, gem5::SOC15_IH_CLIENTID_SDMA1, gem5::SOC15_IH_CLIENTID_SDMA2, gem5::SOC15_IH_CLIENTID_SDMA3, gem5::SOC15_IH_CLIENTID_SDMA4, gem5::SOC15_IH_CLIENTID_SDMA5, gem5::SOC15_IH_CLIENTID_SDMA6, and gem5::SOC15_IH_CLIENTID_SDMA7.

Referenced by trap().

◆ getMmioBase()

|

inline |

Methods for getting SDMA MMIO base address and size.

These are set by the python configuration depending on device to allow for flexible base addresses depending on what GPU is being simulated.

Definition at line 269 of file sdma_engine.hh.

References mmioBase.

◆ getMmioSize()

|

inline |

Definition at line 270 of file sdma_engine.hh.

References mmioSize.

◆ getPageBase()

|

inline |

Definition at line 280 of file sdma_engine.hh.

References pageBase.

◆ getPageDoorbell()

|

inline |

◆ getPageDoorbellOffset()

|

inline |

Definition at line 283 of file sdma_engine.hh.

References pageDoorbellOffset.

Referenced by writeMMIO().

◆ getPageRptr()

|

inline |

Definition at line 281 of file sdma_engine.hh.

References pageRptr.

◆ getPageWptr()

|

inline |

Definition at line 284 of file sdma_engine.hh.

References pageWptr.

◆ indirectBuffer()

| void gem5::SDMAEngine::indirectBuffer | ( | SDMAQueue * | q, |

| sdmaIndirectBuffer * | pkt ) |

Definition at line 829 of file sdma_engine.cc.

References gem5::GEM5_PACKED::base, decodeNext(), getGARTAddr(), gem5::ArmISA::q, and gem5::GEM5_PACKED::size.

Referenced by decodeHeader().

◆ pollRegMem()

| void gem5::SDMAEngine::pollRegMem | ( | SDMAQueue * | q, |

| uint32_t | header, | ||

| sdmaPollRegMem * | pkt ) |

Implements a poll reg/mem packet that polls an SRBM register or a memory location, compares the retrieved value with a reference value and if unsuccessfull it retries indefinitely or for a limited number of times.

Definition at line 942 of file sdma_engine.cc.

References gem5::GEM5_PACKED::address, decodeNext(), gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, gem5::GEM5_PACKED::func, getGARTAddr(), header, gem5::GEM5_PACKED::mask, gem5::GEM5_PACKED::mode, gem5::GEM5_PACKED::op, gem5::GEM5_PACKED::ordinal, panic, gem5::GEM5_PACKED::pollInt, pollRegMemRead(), gem5::ArmISA::q, gem5::GEM5_PACKED::ref, gem5::GEM5_PACKED::retryCount, SDMAEngine(), and warn_once.

Referenced by decodeHeader().

◆ pollRegMemFunc()

| bool gem5::SDMAEngine::pollRegMemFunc | ( | uint32_t | value, |

| uint32_t | reference, | ||

| uint32_t | func ) |

◆ pollRegMemRead()

| void gem5::SDMAEngine::pollRegMemRead | ( | SDMAQueue * | q, |

| uint32_t | header, | ||

| sdmaPollRegMem * | pkt, | ||

| uint32_t | dma_buffer, | ||

| int | count ) |

Definition at line 985 of file sdma_engine.cc.

References gem5::GEM5_PACKED::address, gem5::X86ISA::count, decodeNext(), gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, gem5::GEM5_PACKED::func, header, gem5::GEM5_PACKED::mode, gem5::GEM5_PACKED::op, gem5::GEM5_PACKED::ordinal, pollRegMemFunc(), pollRegMemRead(), gem5::ArmISA::q, gem5::GEM5_PACKED::ref, gem5::GEM5_PACKED::retryCount, and SDMAEngine().

Referenced by pollRegMem(), and pollRegMemRead().

◆ processGfx()

| void gem5::SDMAEngine::processGfx | ( | Addr | wptrOffset | ) |

Given a new write ptr offset, communicated to the GPU through a doorbell write, the SDMA engine processes the page, gfx, rlc0, or rlc1 queue.

Definition at line 294 of file sdma_engine.cc.

References decodeNext(), and gfx.

Referenced by gem5::AMDGPUDevice::writeDoorbell().

◆ processPage()

| void gem5::SDMAEngine::processPage | ( | Addr | wptrOffset | ) |

Definition at line 305 of file sdma_engine.cc.

References decodeNext(), and page.

Referenced by gem5::AMDGPUDevice::writeDoorbell().

◆ processRLC()

Definition at line 316 of file sdma_engine.cc.

References panic, processRLC0(), processRLC1(), and rlcInfo.

Referenced by gem5::AMDGPUDevice::writeDoorbell().

◆ processRLC0()

|

private |

Definition at line 329 of file sdma_engine.cc.

References cur_vmid, decodeNext(), and rlc0.

Referenced by processRLC().

◆ processRLC1()

|

private |

Definition at line 343 of file sdma_engine.cc.

References cur_vmid, decodeNext(), and rlc1.

Referenced by processRLC().

◆ ptePde()

| void gem5::SDMAEngine::ptePde | ( | SDMAQueue * | q, |

| sdmaPtePde * | pkt ) |

Definition at line 1049 of file sdma_engine.cc.

References gem5::GEM5_PACKED::count, gem5::GEM5_PACKED::dest, gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, fatal_if, getGARTAddr(), gpuDevice, gem5::ArmISA::i, gem5::GEM5_PACKED::increment, gem5::GEM5_PACKED::initValue, gem5::GEM5_PACKED::mask, name(), ptePdeDone(), gem5::ArmISA::q, and SDMAEngine().

Referenced by decodeHeader().

◆ ptePdeCleanup()

| void gem5::SDMAEngine::ptePdeCleanup | ( | uint64_t * | dmaBuffer | ) |

Definition at line 1111 of file sdma_engine.cc.

Referenced by ptePdeDone().

◆ ptePdeDone()

| void gem5::SDMAEngine::ptePdeDone | ( | SDMAQueue * | q, |

| sdmaPtePde * | pkt, | ||

| uint64_t * | dmaBuffer ) |

Definition at line 1089 of file sdma_engine.cc.

References gem5::GEM5_PACKED::count, gem5::curTick(), decodeNext(), gem5::GEM5_PACKED::dest, DPRINTF, gpuDevice, name(), ptePdeCleanup(), gem5::ArmISA::q, gem5::EventManager::schedule(), SDMAEngine(), and warn_once.

Referenced by ptePde().

◆ read()

Pure virtual function that the device must implement.

Called when a read command is recieved by the port.

- Parameters

-

pkt Packet describing this request

- Returns

- number of ticks it took to complete

Implements gem5::PioDevice.

Definition at line 203 of file sdma_engine.hh.

◆ registerRLCQueue()

| void gem5::SDMAEngine::registerRLCQueue | ( | Addr | doorbell, |

| Addr | mqdAddr, | ||

| SDMAQueueDesc * | mqd, | ||

| bool | isStatic ) |

Methods for RLC queues.

Definition at line 182 of file sdma_engine.cc.

References gem5::bits(), DPRINTF, panic, gem5::SparcISA::priv, gem5::GEM5_PACKED::rb_base, rlc0, rlc1, rlcInfo, gem5::GEM5_PACKED::rptr, SDMAEngine(), gem5::GEM5_PACKED::sdmax_rlcx_rb_cntl, gem5::GEM5_PACKED::sdmax_rlcx_rb_rptr_addr_hi, gem5::GEM5_PACKED::sdmax_rlcx_rb_rptr_addr_lo, and gem5::GEM5_PACKED::wptr.

Referenced by gem5::PM4PacketProcessor::processSDMAMQD().

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 1252 of file sdma_engine.cc.

References gem5::RiscvISA::base, gfx, gfxBase, gfxDoorbell, gfxDoorbellOffset, gfxIb, gfxRptr, gfxWptr, gem5::ArmISA::i, page, pageBase, pageDoorbell, pageDoorbellOffset, pageIb, pageRptr, pageWptr, rlc0, rlc1, rlcInfo, gem5::ClockedObject::serialize(), SERIALIZE_SCALAR, and SERIALIZE_UNIQUE_PTR_ARRAY.

◆ setGfxBaseHi()

| void gem5::SDMAEngine::setGfxBaseHi | ( | uint32_t | data | ) |

Definition at line 1541 of file sdma_engine.cc.

References data, gfx, gfxBase, and gem5::insertBits().

Referenced by writeMMIO().

◆ setGfxBaseLo()

| void gem5::SDMAEngine::setGfxBaseLo | ( | uint32_t | data | ) |

Definition at line 1533 of file sdma_engine.cc.

References data, gfx, gfxBase, and gem5::insertBits().

Referenced by writeMMIO().

◆ setGfxDoorbellHi()

| void gem5::SDMAEngine::setGfxDoorbellHi | ( | uint32_t | data | ) |

Definition at line 1572 of file sdma_engine.cc.

References data, gfxDoorbell, and gem5::insertBits().

◆ setGfxDoorbellLo()

| void gem5::SDMAEngine::setGfxDoorbellLo | ( | uint32_t | data | ) |

Definition at line 1565 of file sdma_engine.cc.

References data, gfxDoorbell, and gem5::insertBits().

Referenced by writeMMIO().

◆ setGfxDoorbellOffsetHi()

| void gem5::SDMAEngine::setGfxDoorbellOffsetHi | ( | uint32_t | data | ) |

Definition at line 1590 of file sdma_engine.cc.

References data, gfxDoorbellOffset, and gem5::insertBits().

◆ setGfxDoorbellOffsetLo()

| void gem5::SDMAEngine::setGfxDoorbellOffsetLo | ( | uint32_t | data | ) |

Definition at line 1579 of file sdma_engine.cc.

References gem5::bits(), data, gfxDoorbell, gfxDoorbellOffset, gpuDevice, gem5::insertBits(), and gem5::SDMAGfx.

Referenced by writeMMIO().

◆ setGfxRptrHi()

| void gem5::SDMAEngine::setGfxRptrHi | ( | uint32_t | data | ) |

Definition at line 1557 of file sdma_engine.cc.

References data, getGARTAddr(), gfx, gfxRptr, and gem5::insertBits().

Referenced by writeMMIO().

◆ setGfxRptrLo()

| void gem5::SDMAEngine::setGfxRptrLo | ( | uint32_t | data | ) |

Definition at line 1549 of file sdma_engine.cc.

References data, getGARTAddr(), gfx, gfxRptr, and gem5::insertBits().

Referenced by writeMMIO().

◆ setGfxSize()

| void gem5::SDMAEngine::setGfxSize | ( | uint32_t | data | ) |

Definition at line 1597 of file sdma_engine.cc.

References gem5::bits(), data, and gfx.

Referenced by writeMMIO().

◆ setGfxWptrHi()

| void gem5::SDMAEngine::setGfxWptrHi | ( | uint32_t | data | ) |

Definition at line 1612 of file sdma_engine.cc.

References data, gfxWptr, and gem5::insertBits().

Referenced by writeMMIO().

◆ setGfxWptrLo()

| void gem5::SDMAEngine::setGfxWptrLo | ( | uint32_t | data | ) |

Definition at line 1605 of file sdma_engine.cc.

References data, gfxWptr, and gem5::insertBits().

Referenced by writeMMIO().

◆ setGPUDevice()

| void gem5::SDMAEngine::setGPUDevice | ( | AMDGPUDevice * | gpu_device | ) |

Definition at line 78 of file sdma_engine.cc.

◆ setId()

|

inline |

Definition at line 179 of file sdma_engine.hh.

◆ setPageBaseHi()

| void gem5::SDMAEngine::setPageBaseHi | ( | uint32_t | data | ) |

Definition at line 1627 of file sdma_engine.cc.

References data, gem5::insertBits(), page, and pageBase.

◆ setPageBaseLo()

| void gem5::SDMAEngine::setPageBaseLo | ( | uint32_t | data | ) |

Definition at line 1619 of file sdma_engine.cc.

References data, gem5::insertBits(), page, and pageBase.

Referenced by writeMMIO().

◆ setPageDoorbellHi()

| void gem5::SDMAEngine::setPageDoorbellHi | ( | uint32_t | data | ) |

Definition at line 1658 of file sdma_engine.cc.

References data, gem5::insertBits(), and pageDoorbell.

◆ setPageDoorbellLo()

| void gem5::SDMAEngine::setPageDoorbellLo | ( | uint32_t | data | ) |

Definition at line 1651 of file sdma_engine.cc.

References data, gem5::insertBits(), and pageDoorbell.

Referenced by writeMMIO().

◆ setPageDoorbellOffsetHi()

| void gem5::SDMAEngine::setPageDoorbellOffsetHi | ( | uint32_t | data | ) |

Definition at line 1676 of file sdma_engine.cc.

References data, gem5::insertBits(), and pageDoorbellOffset.

◆ setPageDoorbellOffsetLo()

| void gem5::SDMAEngine::setPageDoorbellOffsetLo | ( | uint32_t | data | ) |

Definition at line 1665 of file sdma_engine.cc.

References gem5::bits(), data, gpuDevice, gem5::insertBits(), pageDoorbell, pageDoorbellOffset, and gem5::SDMAPage.

Referenced by writeMMIO().

◆ setPageRptrHi()

| void gem5::SDMAEngine::setPageRptrHi | ( | uint32_t | data | ) |

Definition at line 1643 of file sdma_engine.cc.

References data, getGARTAddr(), gem5::insertBits(), page, and pageRptr.

Referenced by writeMMIO().

◆ setPageRptrLo()

| void gem5::SDMAEngine::setPageRptrLo | ( | uint32_t | data | ) |

Definition at line 1635 of file sdma_engine.cc.

References data, getGARTAddr(), gem5::insertBits(), page, and pageRptr.

Referenced by writeMMIO().

◆ setPageSize()

| void gem5::SDMAEngine::setPageSize | ( | uint32_t | data | ) |

Definition at line 1683 of file sdma_engine.cc.

References gem5::bits(), data, and page.

Referenced by writeMMIO().

◆ setPageWptrHi()

| void gem5::SDMAEngine::setPageWptrHi | ( | uint32_t | data | ) |

Definition at line 1698 of file sdma_engine.cc.

References data, gem5::insertBits(), and pageWptr.

◆ setPageWptrLo()

| void gem5::SDMAEngine::setPageWptrLo | ( | uint32_t | data | ) |

Definition at line 1691 of file sdma_engine.cc.

References data, gem5::insertBits(), and pageWptr.

Referenced by writeMMIO().

◆ srbmWrite()

| void gem5::SDMAEngine::srbmWrite | ( | SDMAQueue * | q, |

| uint32_t | header, | ||

| sdmaSRBMWrite * | pkt ) |

Definition at line 911 of file sdma_engine.cc.

References gem5::GEM5_PACKED::byteEnable, gem5::GEM5_PACKED::data, decodeNext(), DPRINTF, gpuDevice, header, gem5::GEM5_PACKED::ordinal, gem5::ArmISA::q, gem5::GEM5_PACKED::regAddr, and SDMAEngine().

Referenced by decodeHeader().

◆ translate()

|

overridevirtual |

GPUController will perform DMA operations on VAs, and because page faults are not currently supported for GPUController, we must be able to find the pages mapped for the process.

Implements gem5::DmaVirtDevice.

Definition at line 158 of file sdma_engine.cc.

References cur_vmid, gpuDevice, gem5::MipsISA::vaddr, and walker.

Referenced by getDeviceAddress().

◆ trap()

Definition at line 873 of file sdma_engine.cc.

References decodeNext(), DPRINTF, getId(), getIHClientId(), gpuDevice, gem5::GEM5_PACKED::intrContext, gem5::ArmISA::q, SDMAEngine(), SDMAPage, and gem5::TRAP_ID.

Referenced by decodeHeader().

◆ unregisterRLCQueue()

| void gem5::SDMAEngine::unregisterRLCQueue | ( | Addr | doorbell, |

| bool | unmap_static ) |

Definition at line 228 of file sdma_engine.cc.

References gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, gpuDevice, panic, rlc0, rlc1, rlcInfo, gem5::GEM5_PACKED::rptr, SDMAEngine(), warn, and gem5::GEM5_PACKED::wptr.

Referenced by deallocateRLCQueues().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::ClockedObject.

Definition at line 1354 of file sdma_engine.cc.

References gem5::RiscvISA::base, gfx, gfxBase, gfxDoorbell, gfxDoorbellOffset, gfxIb, gfxRptr, gfxWptr, gem5::ArmISA::i, page, pageBase, pageDoorbell, pageDoorbellOffset, pageIb, pageRptr, pageWptr, rlc0, rlc1, rlcInfo, gem5::ClockedObject::unserialize(), UNSERIALIZE_SCALAR, and UNSERIALIZE_UNIQUE_PTR_ARRAY.

◆ write() [1/2]

Inherited methods.

Implements gem5::PioDevice.

Definition at line 202 of file sdma_engine.hh.

Referenced by decodeHeader().

◆ write() [2/2]

Methods that implement processing of SDMA packets.

Definition at line 612 of file sdma_engine.cc.

References gem5::GEM5_PACKED::count, gem5::GEM5_PACKED::dest, gem5::DmaVirtDevice::dmaReadVirt(), DPRINTF, gem5::ArmISA::q, SDMAEngine(), and writeReadData().

◆ writeCleanup()

| void gem5::SDMAEngine::writeCleanup | ( | uint32_t * | dmaBuffer | ) |

Definition at line 684 of file sdma_engine.cc.

Referenced by writeDone().

◆ writeDone()

Definition at line 662 of file sdma_engine.cc.

References gem5::GEM5_PACKED::count, gem5::curTick(), decodeNext(), gem5::GEM5_PACKED::dest, DPRINTF, gpuDevice, name(), gem5::ArmISA::q, gem5::EventManager::schedule(), SDMAEngine(), warn_once, and writeCleanup().

Referenced by writeReadData().

◆ writeMMIO()

Methods for setting the values of SDMA MMIO registers.

Definition at line 1455 of file sdma_engine.cc.

References gem5::bits(), DPRINTF, getGfxDoorbell(), getGfxDoorbellOffset(), gem5::Packet::getLE(), getPageDoorbell(), getPageDoorbellOffset(), gpuDevice, mmSDMA_GFX_DOORBELL, mmSDMA_GFX_DOORBELL_OFFSET, mmSDMA_GFX_RB_BASE, mmSDMA_GFX_RB_BASE_HI, mmSDMA_GFX_RB_CNTL, mmSDMA_GFX_RB_RPTR_ADDR_HI, mmSDMA_GFX_RB_RPTR_ADDR_LO, mmSDMA_GFX_RB_WPTR_POLL_ADDR_HI, mmSDMA_GFX_RB_WPTR_POLL_ADDR_LO, mmSDMA_PAGE_DOORBELL, mmSDMA_PAGE_DOORBELL_OFFSET, mmSDMA_PAGE_RB_BASE, mmSDMA_PAGE_RB_CNTL, mmSDMA_PAGE_RB_RPTR_ADDR_HI, mmSDMA_PAGE_RB_RPTR_ADDR_LO, mmSDMA_PAGE_RB_WPTR_POLL_ADDR_LO, SDMAEngine(), gem5::SDMAGfx, gem5::SDMAPage, setGfxBaseHi(), setGfxBaseLo(), setGfxDoorbellLo(), setGfxDoorbellOffsetLo(), setGfxRptrHi(), setGfxRptrLo(), setGfxSize(), setGfxWptrHi(), setGfxWptrLo(), setPageBaseLo(), setPageDoorbellLo(), setPageDoorbellOffsetLo(), setPageRptrHi(), setPageRptrLo(), setPageSize(), and setPageWptrLo().

◆ writeReadData()

Definition at line 629 of file sdma_engine.cc.

References gem5::GEM5_PACKED::count, gem5::GEM5_PACKED::dest, gem5::DmaVirtDevice::dmaWriteVirt(), DPRINTF, fatal_if, getGARTAddr(), gpuDevice, gem5::ArmISA::i, name(), gem5::ArmISA::q, SDMAEngine(), and writeDone().

Referenced by write().

Member Data Documentation

◆ cur_vmid

| int gem5::SDMAEngine::cur_vmid = 0 |

Definition at line 322 of file sdma_engine.hh.

Referenced by decodeNext(), getDeviceAddress(), processRLC0(), processRLC1(), and translate().

◆ gfx

|

private |

Each SDMAEngine processes four queues: paging, gfx, rlc0, and rlc1, where RLC stands for Run List Controller.

Each one of these can have one indirect buffer associated at any particular time. The switching order between queues is supposed to be page -> gfx -> rlc0 -> page -> gfx -> rlc1, skipping empty queues.

Definition at line 147 of file sdma_engine.hh.

Referenced by processGfx(), SDMAEngine(), serialize(), setGfxBaseHi(), setGfxBaseLo(), setGfxRptrHi(), setGfxRptrLo(), setGfxSize(), and unserialize().

◆ gfxBase

|

private |

Definition at line 151 of file sdma_engine.hh.

Referenced by getGfxBase(), SDMAEngine(), serialize(), setGfxBaseHi(), setGfxBaseLo(), and unserialize().

◆ gfxDoorbell

|

private |

Definition at line 153 of file sdma_engine.hh.

Referenced by getGfxDoorbell(), SDMAEngine(), serialize(), setGfxDoorbellHi(), setGfxDoorbellLo(), setGfxDoorbellOffsetLo(), and unserialize().

◆ gfxDoorbellOffset

|

private |

Definition at line 154 of file sdma_engine.hh.

Referenced by getGfxDoorbellOffset(), SDMAEngine(), serialize(), setGfxDoorbellOffsetHi(), setGfxDoorbellOffsetLo(), and unserialize().

◆ gfxIb

|

private |

Definition at line 147 of file sdma_engine.hh.

Referenced by SDMAEngine(), serialize(), and unserialize().

◆ gfxRptr

|

private |

Definition at line 152 of file sdma_engine.hh.

Referenced by getGfxRptr(), SDMAEngine(), serialize(), setGfxRptrHi(), setGfxRptrLo(), and unserialize().

◆ gfxWptr

|

private |

Definition at line 155 of file sdma_engine.hh.

Referenced by getGfxWptr(), SDMAEngine(), serialize(), setGfxWptrHi(), setGfxWptrLo(), and unserialize().

◆ gpuDevice

|

private |

Definition at line 163 of file sdma_engine.hh.

Referenced by constFill(), copy(), copyDone(), copyReadData(), getDeviceAddress(), getGARTAddr(), ptePde(), ptePdeDone(), SDMAEngine(), setGfxDoorbellOffsetLo(), setGPUDevice(), setPageDoorbellOffsetLo(), srbmWrite(), translate(), trap(), unregisterRLCQueue(), writeDone(), writeMMIO(), and writeReadData().

◆ id

|

private |

Definition at line 139 of file sdma_engine.hh.

Referenced by getId(), and SDMAEngine().

◆ mmioBase

|

private |

Definition at line 171 of file sdma_engine.hh.

Referenced by getMmioBase(), and SDMAEngine().

◆ mmioSize

|

private |

Definition at line 172 of file sdma_engine.hh.

Referenced by getMmioSize(), and SDMAEngine().

◆ page

|

private |

Definition at line 147 of file sdma_engine.hh.

Referenced by processPage(), SDMAEngine(), serialize(), setPageBaseHi(), setPageBaseLo(), setPageRptrHi(), setPageRptrLo(), setPageSize(), and unserialize().

◆ pageBase

|

private |

Definition at line 157 of file sdma_engine.hh.

Referenced by getPageBase(), SDMAEngine(), serialize(), setPageBaseHi(), setPageBaseLo(), and unserialize().

◆ pageDoorbell

|

private |

Definition at line 159 of file sdma_engine.hh.

Referenced by getPageDoorbell(), SDMAEngine(), serialize(), setPageDoorbellHi(), setPageDoorbellLo(), setPageDoorbellOffsetLo(), and unserialize().

◆ pageDoorbellOffset

|

private |

Definition at line 160 of file sdma_engine.hh.

Referenced by getPageDoorbellOffset(), SDMAEngine(), serialize(), setPageDoorbellOffsetHi(), setPageDoorbellOffsetLo(), and unserialize().

◆ pageIb

|

private |

Definition at line 147 of file sdma_engine.hh.

Referenced by SDMAEngine(), serialize(), and unserialize().

◆ pageRptr

|

private |

Definition at line 158 of file sdma_engine.hh.

Referenced by getPageRptr(), SDMAEngine(), serialize(), setPageRptrHi(), setPageRptrLo(), and unserialize().

◆ pageWptr

|

private |

Definition at line 161 of file sdma_engine.hh.

Referenced by getPageWptr(), SDMAEngine(), serialize(), setPageWptrHi(), setPageWptrLo(), and unserialize().

◆ rlc0

|

private |

Definition at line 148 of file sdma_engine.hh.

Referenced by processRLC0(), registerRLCQueue(), SDMAEngine(), serialize(), unregisterRLCQueue(), and unserialize().

◆ rlc0Ib

|

private |

Definition at line 148 of file sdma_engine.hh.

Referenced by SDMAEngine().

◆ rlc1

|

private |

Definition at line 148 of file sdma_engine.hh.

Referenced by processRLC1(), registerRLCQueue(), SDMAEngine(), serialize(), unregisterRLCQueue(), and unserialize().

◆ rlc1Ib

|

private |

Definition at line 148 of file sdma_engine.hh.

Referenced by SDMAEngine().

◆ rlcInfo

|

private |

Definition at line 167 of file sdma_engine.hh.

Referenced by deallocateRLCQueues(), processRLC(), registerRLCQueue(), serialize(), unregisterRLCQueue(), and unserialize().

◆ walker

|

private |

Definition at line 164 of file sdma_engine.hh.

Referenced by SDMAEngine(), setGPUDevice(), and translate().

The documentation for this class was generated from the following files:

- dev/amdgpu/sdma_engine.hh

- dev/amdgpu/sdma_engine.cc

Generated on Sat Oct 18 2025 08:06:54 for gem5 by doxygen 1.14.0