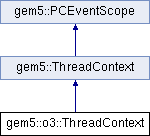

Derived ThreadContext class for use with the O3CPU. More...

#include <thread_context.hh>

Public Member Functions | |

| bool | schedule (PCEvent *e) override |

| bool | remove (PCEvent *e) override |

| void | scheduleInstCountEvent (Event *event, Tick count) override |

| void | descheduleInstCountEvent (Event *event) override |

| Tick | getCurrentInstCount () override |

| BaseMMU * | getMMUPtr () override |

| Returns a pointer to the MMU. | |

| CheckerCPU * | getCheckerCpuPtr () override |

| BaseISA * | getIsaPtr () const override |

| InstDecoder * | getDecoderPtr () override |

| BaseCPU * | getCpuPtr () override |

| Returns a pointer to this CPU. | |

| int | cpuId () const override |

| Reads this CPU's ID. | |

| uint32_t | socketId () const override |

| Reads this CPU's Socket ID. | |

| ContextID | contextId () const override |

| void | setContextId (ContextID id) override |

| int | threadId () const override |

| Returns this thread's ID number. | |

| void | setThreadId (int id) override |

| System * | getSystemPtr () override |

| Returns a pointer to the system. | |

| Process * | getProcessPtr () override |

| Returns a pointer to this thread's process. | |

| void | setProcessPtr (Process *p) override |

| Status | status () const override |

| Returns this thread's status. | |

| void | setStatus (Status new_status) override |

| Sets this thread's status. | |

| void | activate () override |

| Set the status to Active. | |

| void | suspend () override |

| Set the status to Suspended. | |

| void | halt () override |

| Set the status to Halted. | |

| void | takeOverFrom (gem5::ThreadContext *old_context) override |

| Takes over execution of a thread from another CPU. | |

| Tick | readLastActivate () override |

| Reads the last tick that this thread was activated on. | |

| Tick | readLastSuspend () override |

| Reads the last tick that this thread was suspended on. | |

| void | copyArchRegs (gem5::ThreadContext *tc) override |

| Copies the architectural registers from another TC into this TC. | |

| void | clearArchRegs () override |

| Resets all architectural registers to 0. | |

| const PCStateBase & | pcState () const override |

| Reads this thread's PC state. | |

| void | pcState (const PCStateBase &val) override |

| Sets this thread's PC state. | |

| void | pcStateNoRecord (const PCStateBase &val) override |

| RegVal | readMiscRegNoEffect (RegIndex misc_reg) const override |

| Reads a miscellaneous register. | |

| RegVal | readMiscReg (RegIndex misc_reg) override |

| Reads a misc. | |

| void | setMiscRegNoEffect (RegIndex misc_reg, RegVal val) override |

| Sets a misc. | |

| void | setMiscReg (RegIndex misc_reg, RegVal val) override |

| Sets a misc. | |

| unsigned | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. | |

| void | setStCondFailures (unsigned sc_failures) override |

| Sets the number of consecutive store conditional failures. | |

| void | conditionalSquash () |

| check if the cpu is currently in state update mode and squash if not. | |

| RegVal | getReg (const RegId ®) const override |

| void | getReg (const RegId ®, void *val) const override |

| void * | getWritableReg (const RegId ®) override |

| void | setReg (const RegId ®, RegVal val) override |

| void | setReg (const RegId ®, const void *val) override |

| void | htmAbortTransaction (uint64_t htm_uid, HtmFailureFaultCause cause) override |

| BaseHTMCheckpointPtr & | getHtmCheckpointPtr () override |

| void | setHtmCheckpointPtr (BaseHTMCheckpointPtr new_cpt) override |

| Public Member Functions inherited from gem5::ThreadContext | |

| bool | getUseForClone () |

| void | setUseForClone (bool new_val) |

| virtual | ~ThreadContext () |

| virtual void | sendFunctional (PacketPtr pkt) |

| void | quiesce () |

| Quiesce thread context. | |

| void | quiesceTick (Tick resume) |

| Quiesce, suspend, and schedule activate at resume. | |

| virtual void | regStats (const std::string &name) |

| void | pcState (Addr addr) |

| virtual int | exit () |

Public Attributes | |

| CPU * | cpu |

| Pointer to the CPU. | |

| ThreadState * | thread |

| Pointer to the thread state that this TC corrseponds to. | |

| Public Attributes inherited from gem5::ThreadContext | |

| int | intResult = DefaultIntResult |

| double | floatResult = DefaultFloatResult |

| int | intOffset = 0 |

Additional Inherited Members | |

| Public Types inherited from gem5::ThreadContext | |

| enum | Status { Active , Suspended , Halting , Halted } |

| Static Public Member Functions inherited from gem5::ThreadContext | |

| static void | compare (ThreadContext *one, ThreadContext *two) |

| function to compare two thread contexts (for debugging) | |

| Static Public Attributes inherited from gem5::ThreadContext | |

| static const int | ints [] |

| static const double | floats [] |

| static const int | DefaultIntResult = 0 |

| static const double | DefaultFloatResult = 0.0 |

| Protected Attributes inherited from gem5::ThreadContext | |

| bool | useForClone = false |

Detailed Description

Derived ThreadContext class for use with the O3CPU.

It provides the interface for any external objects to access a single thread's state and some general CPU state. Any time external objects try to update state through this interface, the CPU will create an event to squash all in-flight instructions in order to ensure state is maintained correctly. It must be defined specifically for the O3CPU because not all architectural state is located within the ThreadState (such as the commit PC, and registers), and specific actions must be taken when using this interface (such as squashing all in-flight instructions when doing a write to this interface).

Definition at line 67 of file thread_context.hh.

Member Function Documentation

◆ activate()

|

overridevirtual |

Set the status to Active.

Implements gem5::ThreadContext.

Definition at line 68 of file thread_context.cc.

References gem5::ThreadContext::Active, cpu, gem5::curTick(), DPRINTF, thread, and threadId().

◆ clearArchRegs()

|

overridevirtual |

Resets all architectural registers to 0.

Implements gem5::ThreadContext.

Definition at line 145 of file thread_context.cc.

◆ conditionalSquash()

|

inline |

check if the cpu is currently in state update mode and squash if not.

This function will return true if a trap is pending or if a fault or similar is currently writing to the thread context and doesn't want reset all the state (see noSquashFromTC).

Definition at line 233 of file thread_context.hh.

Referenced by htmAbortTransaction(), pcState(), pcStateNoRecord(), setMiscReg(), setMiscRegNoEffect(), setReg(), and setReg().

◆ contextId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 129 of file thread_context.hh.

References thread.

◆ copyArchRegs()

|

overridevirtual |

Copies the architectural registers from another TC into this TC.

Implements gem5::ThreadContext.

Definition at line 136 of file thread_context.cc.

References gem5::BaseISA::copyRegsFrom(), getIsaPtr(), and thread.

◆ cpuId()

|

inlineoverridevirtual |

Reads this CPU's ID.

Implements gem5::ThreadContext.

Definition at line 124 of file thread_context.hh.

References cpu.

◆ descheduleInstCountEvent()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 90 of file thread_context.hh.

References gem5::MipsISA::event, and thread.

◆ getCheckerCpuPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 106 of file thread_context.hh.

◆ getCpuPtr()

|

inlineoverridevirtual |

Returns a pointer to this CPU.

Implements gem5::ThreadContext.

Definition at line 121 of file thread_context.hh.

References cpu.

◆ getCurrentInstCount()

|

inlineoverridevirtual |

◆ getDecoderPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 115 of file thread_context.hh.

Referenced by takeOverFrom().

◆ getHtmCheckpointPtr()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 225 of file thread_context.cc.

References thread.

◆ getIsaPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 109 of file thread_context.hh.

Referenced by copyArchRegs(), and takeOverFrom().

◆ getMMUPtr()

|

inlineoverridevirtual |

Returns a pointer to the MMU.

Implements gem5::ThreadContext.

Definition at line 104 of file thread_context.hh.

References cpu.

◆ getProcessPtr()

|

inlineoverridevirtual |

Returns a pointer to this thread's process.

Implements gem5::ThreadContext.

Definition at line 141 of file thread_context.hh.

References thread.

◆ getReg() [1/2]

Reimplemented from gem5::ThreadContext.

Definition at line 151 of file thread_context.cc.

References cpu, gem5::X86ISA::reg, and thread.

◆ getReg() [2/2]

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 163 of file thread_context.cc.

References cpu, gem5::X86ISA::reg, thread, and gem5::X86ISA::val.

◆ getSystemPtr()

|

inlineoverridevirtual |

Returns a pointer to the system.

Implements gem5::ThreadContext.

Definition at line 138 of file thread_context.hh.

References cpu.

◆ getWritableReg()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 157 of file thread_context.cc.

References cpu, gem5::X86ISA::reg, and thread.

◆ halt()

|

overridevirtual |

Set the status to Halted.

Implements gem5::ThreadContext.

Definition at line 105 of file thread_context.cc.

References cpu, DPRINTF, gem5::ThreadContext::Halted, gem5::ThreadContext::Halting, thread, and threadId().

◆ htmAbortTransaction()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 216 of file thread_context.cc.

References conditionalSquash(), cpu, and thread.

◆ pcState() [1/2]

|

inlineoverridevirtual |

Reads this thread's PC state.

Implements gem5::ThreadContext.

Definition at line 180 of file thread_context.hh.

◆ pcState() [2/2]

|

overridevirtual |

Sets this thread's PC state.

Implements gem5::ThreadContext.

Definition at line 183 of file thread_context.cc.

References conditionalSquash(), cpu, thread, and gem5::X86ISA::val.

◆ pcStateNoRecord()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 191 of file thread_context.cc.

References conditionalSquash(), cpu, thread, and gem5::X86ISA::val.

◆ readLastActivate()

|

overridevirtual |

Reads the last tick that this thread was activated on.

Implements gem5::ThreadContext.

Definition at line 124 of file thread_context.cc.

References thread.

◆ readLastSuspend()

|

overridevirtual |

Reads the last tick that this thread was suspended on.

Implements gem5::ThreadContext.

Definition at line 130 of file thread_context.cc.

References thread.

◆ readMiscReg()

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements gem5::ThreadContext.

Definition at line 200 of file thread_context.hh.

◆ readMiscRegNoEffect()

|

inlineoverridevirtual |

Reads a miscellaneous register.

Implements gem5::ThreadContext.

Definition at line 192 of file thread_context.hh.

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements gem5::ThreadContext.

Definition at line 215 of file thread_context.hh.

References thread.

◆ remove()

|

inlineoverridevirtual |

Implements gem5::PCEventScope.

Definition at line 79 of file thread_context.hh.

References gem5::ArmISA::e, and thread.

◆ schedule()

|

inlineoverridevirtual |

Implements gem5::PCEventScope.

Definition at line 74 of file thread_context.hh.

References gem5::ArmISA::e, and thread.

◆ scheduleInstCountEvent()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 85 of file thread_context.hh.

References gem5::X86ISA::count, gem5::MipsISA::event, and thread.

◆ setContextId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 131 of file thread_context.hh.

References thread.

◆ setHtmCheckpointPtr()

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 231 of file thread_context.cc.

References thread.

◆ setMiscReg()

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Implements gem5::ThreadContext.

Definition at line 207 of file thread_context.cc.

References conditionalSquash(), cpu, thread, and gem5::X86ISA::val.

◆ setMiscRegNoEffect()

Sets a misc.

register.

Implements gem5::ThreadContext.

Definition at line 199 of file thread_context.cc.

References conditionalSquash(), cpu, thread, and gem5::X86ISA::val.

◆ setProcessPtr()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 143 of file thread_context.hh.

References gem5::MipsISA::p, and thread.

◆ setReg() [1/2]

|

overridevirtual |

Implements gem5::ThreadContext.

Definition at line 176 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::X86ISA::reg, thread, and gem5::X86ISA::val.

◆ setReg() [2/2]

Reimplemented from gem5::ThreadContext.

Definition at line 169 of file thread_context.cc.

References conditionalSquash(), cpu, gem5::X86ISA::reg, thread, and gem5::X86ISA::val.

◆ setStatus()

|

inlineoverridevirtual |

Sets this thread's status.

Implements gem5::ThreadContext.

Definition at line 150 of file thread_context.hh.

References thread.

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements gem5::ThreadContext.

Definition at line 222 of file thread_context.hh.

References thread.

◆ setThreadId()

|

inlineoverridevirtual |

Implements gem5::ThreadContext.

Definition at line 135 of file thread_context.hh.

References thread.

◆ socketId()

|

inlineoverridevirtual |

Reads this CPU's Socket ID.

Implements gem5::ThreadContext.

Definition at line 127 of file thread_context.hh.

References cpu.

◆ status()

|

inlineoverridevirtual |

Returns this thread's status.

Implements gem5::ThreadContext.

Definition at line 146 of file thread_context.hh.

References thread.

◆ suspend()

|

overridevirtual |

Set the status to Suspended.

Implements gem5::ThreadContext.

Definition at line 84 of file thread_context.cc.

References cpu, gem5::curTick(), DPRINTF, gem5::ThreadContext::Suspended, thread, and threadId().

◆ takeOverFrom()

|

overridevirtual |

Takes over execution of a thread from another CPU.

Implements gem5::ThreadContext.

Definition at line 53 of file thread_context.cc.

References getDecoderPtr(), gem5::ThreadContext::getDecoderPtr(), getIsaPtr(), gem5::BaseISA::takeOverFrom(), gem5::InstDecoder::takeOverFrom(), gem5::takeOverFrom(), and thread.

◆ threadId()

|

inlineoverridevirtual |

Returns this thread's ID number.

Implements gem5::ThreadContext.

Definition at line 134 of file thread_context.hh.

References thread.

Referenced by activate(), halt(), and suspend().

Member Data Documentation

◆ cpu

| CPU* gem5::o3::ThreadContext::cpu |

Pointer to the CPU.

Definition at line 71 of file thread_context.hh.

Referenced by activate(), clearArchRegs(), conditionalSquash(), cpuId(), getCpuPtr(), getDecoderPtr(), getIsaPtr(), getMMUPtr(), getReg(), getReg(), getSystemPtr(), getWritableReg(), halt(), htmAbortTransaction(), pcState(), pcState(), pcStateNoRecord(), readMiscReg(), readMiscRegNoEffect(), setMiscReg(), setMiscRegNoEffect(), setReg(), setReg(), socketId(), and suspend().

◆ thread

| ThreadState* gem5::o3::ThreadContext::thread |

Pointer to the thread state that this TC corrseponds to.

Definition at line 101 of file thread_context.hh.

Referenced by activate(), clearArchRegs(), conditionalSquash(), contextId(), copyArchRegs(), descheduleInstCountEvent(), getCurrentInstCount(), getDecoderPtr(), getHtmCheckpointPtr(), getIsaPtr(), getProcessPtr(), getReg(), getReg(), getWritableReg(), halt(), htmAbortTransaction(), pcState(), pcState(), pcStateNoRecord(), readLastActivate(), readLastSuspend(), readMiscReg(), readMiscRegNoEffect(), readStCondFailures(), remove(), schedule(), scheduleInstCountEvent(), setContextId(), setHtmCheckpointPtr(), setMiscReg(), setMiscRegNoEffect(), setProcessPtr(), setReg(), setReg(), setStatus(), setStCondFailures(), setThreadId(), status(), suspend(), takeOverFrom(), and threadId().

The documentation for this class was generated from the following files:

- cpu/o3/thread_context.hh

- cpu/o3/thread_context.cc

Generated on Sat Oct 18 2025 08:07:00 for gem5 by doxygen 1.14.0