#include <shader.hh>

Classes | |

| struct | ShaderStats |

Public Types | |

| enum | hsail_mode_e { SIMT , VECTOR_SCALAR } |

| typedef ShaderParams | Params |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| GPUDispatcher & | dispatcher () |

| void | sampleLoad (const Tick accessTime) |

| void | sampleStore (const Tick accessTime) |

| void | sampleInstRoundTrip (std::vector< Tick > roundTripTime) |

| void | sampleLineRoundTrip (const std::map< Addr, std::vector< Tick > > &roundTripTime) |

| void | setHwReg (int regIdx, uint32_t val) |

| uint32_t | getHwReg (int regIdx) |

| const ApertureRegister & | gpuVmApe () const |

| const ApertureRegister & | ldsApe () const |

| void | setLdsApe (Addr base, Addr limit) |

| const ApertureRegister & | scratchApe () const |

| void | setScratchApe (Addr base, Addr limit) |

| bool | isGpuVmApe (Addr addr) const |

| bool | isLdsApe (Addr addr) const |

| bool | isScratchApe (Addr addr) const |

| Addr | getScratchBase () |

| Addr | getHiddenPrivateBase () |

| void | initShHiddenPrivateBase (Addr queueBase, uint32_t offset) |

| RequestorID | vramRequestorId () |

| Forward the VRAM requestor ID needed for device memory from CP. | |

| GfxVersion | getGfxVersion () const |

| Tick | getProgressInterval () const |

| Shader (const Params &p) | |

| ~Shader () | |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| void | execScheduledAdds () |

| void | ScheduleAdd (int *val, Tick when, int x) |

| bool | processTimingPacket (PacketPtr pkt) |

| void | AccessMem (uint64_t address, void *ptr, uint32_t size, int cu_id, MemCmd cmd, bool suppress_func_errors) |

| void | ReadMem (uint64_t address, void *ptr, uint32_t sz, int cu_id) |

| void | ReadMem (uint64_t address, void *ptr, uint32_t sz, int cu_id, bool suppress_func_errors) |

| void | WriteMem (uint64_t address, void *ptr, uint32_t sz, int cu_id) |

| void | WriteMem (uint64_t address, void *ptr, uint32_t sz, int cu_id, bool suppress_func_errors) |

| void | doFunctionalAccess (const RequestPtr &req, MemCmd cmd, void *data, bool suppress_func_errors, int cu_id) |

| void | registerCU (int cu_id, ComputeUnit *compute_unit) |

| void | prepareInvalidate (HSAQueueEntry *task) |

| void | prepareFlush (GPUDynInstPtr gpuDynInst) |

| dispatcher/shader arranges flush requests to the CUs | |

| bool | dispatchWorkgroups (HSAQueueEntry *task) |

| Addr | mmap (int length) |

| void | functionalTLBAccess (PacketPtr pkt, int cu_id, BaseMMU::Mode mode) |

| void | updateContext (int cid) |

| void | notifyCuSleep () |

| void | incVectorInstSrcOperand (int num_operands) |

| void | incVectorInstDstOperand (int num_operands) |

| void | requestKernelExitEvent (bool is_blit_kernel) |

| void | decNumOutstandingInvL2s () |

| void | incNumOutstandingInvL2s () |

| int | getNumOutstandingInvL2s () const |

| void | addDeferredDispatch (void *raw_pkt, uint32_t queue_id, Addr host_pkt_addr) |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Public Attributes | |

| SimpleThread * | cpuThread |

| ThreadContext * | gpuTc |

| BaseCPU * | cpuPointer |

| EventFunctionWrapper | tickEvent |

| bool | timingSim |

| hsail_mode_e | hsail_mode |

| int | impl_kern_launch_acq |

| int | impl_kern_end_rel |

| int | coissue_return |

| int | trace_vgpr_all |

| int | n_cu |

| int | n_wf |

| int | n_cu_per_sqc |

| int | globalMemSize |

| int | nextSchedCu |

| uint32_t | sa_n |

| std::vector< int * > | sa_val |

| std::vector< uint64_t > | sa_when |

| std::vector< int32_t > | sa_x |

| std::vector< ComputeUnit * > | cuList |

| GPUCommandProcessor & | gpuCmdProc |

| GPUDispatcher & | _dispatcher |

| AMDGPUSystemHub * | systemHub |

| int64_t | max_valu_insts |

| int64_t | total_valu_insts |

| const Tick | progressInterval |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Protected Attributes | |

| gem5::Shader::ShaderStats | stats |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Private Attributes | |

| ApertureRegister | _gpuVmApe |

| ApertureRegister | _ldsApe |

| ApertureRegister | _scratchApe |

| Addr | shHiddenPrivateBaseVmid |

| std::unordered_map< int, uint32_t > | hwRegs |

| int | _activeCus |

| Tick | _lastInactiveTick |

| bool | kernelExitRequested = false |

| bool | blitKernel = false |

| int | num_outstanding_invl2s = 0 |

| std::vector< std::tuple< void *, uint32_t, Addr > > | deferred_dispatches |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

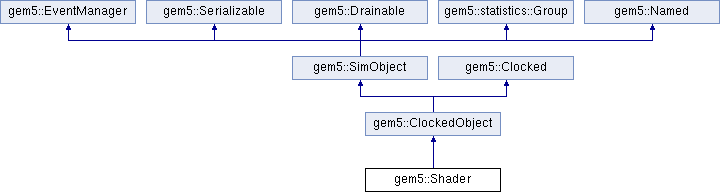

Detailed Description

Member Typedef Documentation

◆ Params

| typedef ShaderParams gem5::Shader::Params |

Member Enumeration Documentation

◆ hsail_mode_e

Constructor & Destructor Documentation

◆ Shader()

| gem5::Shader::Shader | ( | const Params & | p | ) |

Definition at line 57 of file shader.cc.

References _activeCus, _lastInactiveTick, gem5::ClockedObject::ClockedObject(), cpuPointer, cpuThread, execScheduledAdds(), gpuTc, gem5::MipsISA::p, and tickEvent.

Referenced by gem5::Shader::ShaderStats::ShaderStats().

◆ ~Shader()

Member Function Documentation

◆ AccessMem()

| void gem5::Shader::AccessMem | ( | uint64_t | address, |

| void * | ptr, | ||

| uint32_t | size, | ||

| int | cu_id, | ||

| MemCmd | cmd, | ||

| bool | suppress_func_errors ) |

Definition at line 400 of file shader.cc.

References cuList, doFunctionalAccess(), and gem5::ChunkGenerator::done().

Referenced by ReadMem(), ReadMem(), WriteMem(), and WriteMem().

◆ addDeferredDispatch()

| void gem5::Shader::addDeferredDispatch | ( | void * | raw_pkt, |

| uint32_t | queue_id, | ||

| Addr | host_pkt_addr ) |

Definition at line 576 of file shader.cc.

References deferred_dispatches.

Referenced by gem5::GPUCommandProcessor::submitDispatchPkt().

◆ decNumOutstandingInvL2s()

| void gem5::Shader::decNumOutstandingInvL2s | ( | ) |

Definition at line 561 of file shader.cc.

References deferred_dispatches, gpuCmdProc, and num_outstanding_invl2s.

Referenced by gem5::ComputeUnit::DataPort::handleResponse().

◆ dispatcher()

| GPUDispatcher & gem5::Shader::dispatcher | ( | ) |

Definition at line 112 of file shader.cc.

References _dispatcher.

Referenced by gem5::VegaISA::Inst_SOPP__S_ENDPGM::execute().

◆ dispatchWorkgroups()

| bool gem5::Shader::dispatchWorkgroups | ( | HSAQueueEntry * | task | ) |

Definition at line 259 of file shader.cc.

References _activeCus, _lastInactiveTick, cuList, gem5::curTick(), gem5::HSAQueueEntry::dispComplete(), DPRINTF, gem5::HSAQueueEntry::globalWgId(), gem5::HSAQueueEntry::markWgDispatch(), n_cu, nextSchedCu, panic_if, and tickEvent.

◆ doFunctionalAccess()

| void gem5::Shader::doFunctionalAccess | ( | const RequestPtr & | req, |

| MemCmd | cmd, | ||

| void * | data, | ||

| bool | suppress_func_errors, | ||

| int | cu_id ) |

Definition at line 308 of file shader.cc.

References cuList, data, gem5::Packet::dataStatic(), fatal, functionalTLBAccess(), gem5::BaseMMU::Read, gem5::MemCmd::ReadReq, gem5::Packet::req, gem5::roundDown(), gem5::Packet::setSuppressFuncError(), gem5::BaseMMU::Write, and gem5::MemCmd::WriteReq.

Referenced by AccessMem().

◆ execScheduledAdds()

| void gem5::Shader::execScheduledAdds | ( | ) |

Definition at line 174 of file shader.cc.

References gem5::curTick(), DPRINTF, gem5::ArmISA::i, panic_if, sa_n, sa_val, sa_when, sa_x, gem5::EventManager::schedule(), and tickEvent.

Referenced by Shader().

◆ functionalTLBAccess()

| void gem5::Shader::functionalTLBAccess | ( | PacketPtr | pkt, |

| int | cu_id, | ||

| BaseMMU::Mode | mode ) |

Definition at line 451 of file shader.cc.

References cuList, gpuTc, gem5::ArmISA::mode, gem5::safe_cast(), gem5::Packet::senderState, and gem5::GpuTranslationState::tlbEntry.

Referenced by doFunctionalAccess().

◆ getGfxVersion()

| GfxVersion gem5::Shader::getGfxVersion | ( | ) | const |

Definition at line 593 of file shader.cc.

References gpuCmdProc.

◆ getHiddenPrivateBase()

|

inline |

Definition at line 203 of file shader.hh.

References shHiddenPrivateBaseVmid.

◆ getHwReg()

|

inline |

◆ getNumOutstandingInvL2s()

|

inline |

Definition at line 345 of file shader.hh.

References num_outstanding_invl2s.

Referenced by gem5::ComputeUnit::DataPort::handleResponse().

◆ getProgressInterval()

|

inline |

Definition at line 280 of file shader.hh.

References progressInterval.

◆ getScratchBase()

|

inline |

Definition at line 197 of file shader.hh.

References _scratchApe.

◆ gpuVmApe()

|

inline |

◆ incNumOutstandingInvL2s()

|

inline |

Definition at line 344 of file shader.hh.

References num_outstanding_invl2s.

◆ incVectorInstDstOperand()

|

inline |

◆ incVectorInstSrcOperand()

|

inline |

◆ init()

|

virtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Definition at line 151 of file shader.cc.

References cpuPointer, and gpuTc.

◆ initShHiddenPrivateBase()

|

inline |

Definition at line 209 of file shader.hh.

References gem5::ArmISA::offset, panic_if, and shHiddenPrivateBaseVmid.

◆ isGpuVmApe()

|

inline |

Definition at line 172 of file shader.hh.

References _gpuVmApe, and gem5::X86ISA::addr.

◆ isLdsApe()

|

inline |

Definition at line 180 of file shader.hh.

References _ldsApe, and gem5::X86ISA::addr.

◆ isScratchApe()

|

inline |

Definition at line 188 of file shader.hh.

References _scratchApe, and gem5::X86ISA::addr.

◆ ldsApe()

|

inline |

Definition at line 146 of file shader.hh.

References _ldsApe.

Referenced by gem5::VegaISA::ScalarOperand< ScalarRegU8, false, 1 >::readSpecialVal(), and gem5::GPUDynInst::resolveFlatSegment().

◆ mmap()

| Addr gem5::Shader::mmap | ( | int | length | ) |

Definition at line 118 of file shader.cc.

References gem5::Process::allocateMem(), DPRINTF, gpuTc, gem5::Process::memState, gem5::Process::mmapGrowsDown(), gem5::X86ISA::PageBytes, and gem5::roundUp().

◆ notifyCuSleep()

| void gem5::Shader::notifyCuSleep | ( | ) |

Definition at line 541 of file shader.cc.

References _activeCus, _lastInactiveTick, blitKernel, cuList, gem5::curTick(), gem5::exitSimLoop(), kernelExitRequested, panic_if, and stats.

◆ prepareFlush()

| void gem5::Shader::prepareFlush | ( | GPUDynInstPtr | gpuDynInst | ) |

dispatcher/shader arranges flush requests to the CUs

Definition at line 246 of file shader.cc.

References _dispatcher, and cuList.

Referenced by gem5::VegaISA::Inst_SOPP__S_ENDPGM::execute().

◆ prepareInvalidate()

| void gem5::Shader::prepareInvalidate | ( | HSAQueueEntry * | task | ) |

Definition at line 204 of file shader.cc.

References _dispatcher, cuList, gem5::HSAQueueEntry::dispatchId(), gem5::HSAQueueEntry::isInvStarted(), n_cu, n_cu_per_sqc, and gem5::HSAQueueEntry::outstandingInvs().

◆ processTimingPacket()

◆ ReadMem() [1/2]

| void gem5::Shader::ReadMem | ( | uint64_t | address, |

| void * | ptr, | ||

| uint32_t | sz, | ||

| int | cu_id ) |

Definition at line 418 of file shader.cc.

References AccessMem(), and gem5::MemCmd::ReadReq.

◆ ReadMem() [2/2]

| void gem5::Shader::ReadMem | ( | uint64_t | address, |

| void * | ptr, | ||

| uint32_t | sz, | ||

| int | cu_id, | ||

| bool | suppress_func_errors ) |

Definition at line 424 of file shader.cc.

References AccessMem(), and gem5::MemCmd::ReadReq.

◆ registerCU()

|

inline |

◆ requestKernelExitEvent()

|

inline |

Definition at line 337 of file shader.hh.

References blitKernel, and kernelExitRequested.

◆ sampleInstRoundTrip()

| void gem5::Shader::sampleInstRoundTrip | ( | std::vector< Tick > | roundTripTime | ) |

Definition at line 492 of file shader.cc.

References gem5::InstMemoryHopMax, stats, gem5::ArmISA::t1, gem5::ArmISA::t2, gem5::ArmISA::t3, gem5::ArmISA::t4, and gem5::ArmISA::t5.

◆ sampleLineRoundTrip()

| void gem5::Shader::sampleLineRoundTrip | ( | const std::map< Addr, std::vector< Tick > > & | roundTripTime | ) |

◆ sampleLoad()

| void gem5::Shader::sampleLoad | ( | const Tick | accessTime | ) |

◆ sampleStore()

| void gem5::Shader::sampleStore | ( | const Tick | accessTime | ) |

◆ ScheduleAdd()

| void gem5::Shader::ScheduleAdd | ( | int * | val, |

| Tick | when, | ||

| int | x ) |

Definition at line 381 of file shader.cc.

References gem5::curTick(), DPRINTF, gem5::EventManager::reschedule(), sa_n, sa_val, sa_when, sa_x, tickEvent, gem5::X86ISA::val, and gem5::RiscvISA::x.

◆ scratchApe()

|

inline |

Definition at line 159 of file shader.hh.

References _scratchApe.

Referenced by gem5::VegaISA::ScalarOperand< ScalarRegU8, false, 1 >::readSpecialVal().

◆ setHwReg()

|

inline |

Definition at line 128 of file shader.hh.

References hwRegs, and gem5::X86ISA::val.

◆ setLdsApe()

Definition at line 152 of file shader.hh.

References _ldsApe, gem5::RiscvISA::base, and gem5::X86ISA::limit.

◆ setScratchApe()

Definition at line 165 of file shader.hh.

References _scratchApe, gem5::RiscvISA::base, and gem5::X86ISA::limit.

◆ updateContext()

| void gem5::Shader::updateContext | ( | int | cid | ) |

Definition at line 166 of file shader.cc.

References cpuPointer, and gpuTc.

◆ vramRequestorId()

| RequestorID gem5::Shader::vramRequestorId | ( | ) |

Forward the VRAM requestor ID needed for device memory from CP.

Definition at line 587 of file shader.cc.

References gpuCmdProc.

◆ WriteMem() [1/2]

| void gem5::Shader::WriteMem | ( | uint64_t | address, |

| void * | ptr, | ||

| uint32_t | sz, | ||

| int | cu_id ) |

Definition at line 432 of file shader.cc.

References AccessMem(), and gem5::MemCmd::WriteReq.

◆ WriteMem() [2/2]

| void gem5::Shader::WriteMem | ( | uint64_t | address, |

| void * | ptr, | ||

| uint32_t | sz, | ||

| int | cu_id, | ||

| bool | suppress_func_errors ) |

Definition at line 438 of file shader.cc.

References AccessMem(), and gem5::MemCmd::WriteReq.

Member Data Documentation

◆ _activeCus

|

private |

Definition at line 95 of file shader.hh.

Referenced by dispatchWorkgroups(), notifyCuSleep(), and Shader().

◆ _dispatcher

| GPUDispatcher& gem5::Shader::_dispatcher |

Definition at line 272 of file shader.hh.

Referenced by dispatcher(), prepareFlush(), and prepareInvalidate().

◆ _gpuVmApe

|

private |

Definition at line 86 of file shader.hh.

Referenced by gpuVmApe(), and isGpuVmApe().

◆ _lastInactiveTick

|

private |

Definition at line 98 of file shader.hh.

Referenced by dispatchWorkgroups(), notifyCuSleep(), and Shader().

◆ _ldsApe

|

private |

Definition at line 87 of file shader.hh.

Referenced by isLdsApe(), ldsApe(), and setLdsApe().

◆ _scratchApe

|

private |

Definition at line 88 of file shader.hh.

Referenced by getScratchBase(), isScratchApe(), scratchApe(), and setScratchApe().

◆ blitKernel

|

private |

Definition at line 105 of file shader.hh.

Referenced by notifyCuSleep(), and requestKernelExitEvent().

◆ coissue_return

◆ cpuPointer

| BaseCPU* gem5::Shader::cpuPointer |

Definition at line 125 of file shader.hh.

Referenced by init(), Shader(), and updateContext().

◆ cpuThread

| SimpleThread* gem5::Shader::cpuThread |

◆ cuList

| std::vector<ComputeUnit*> gem5::Shader::cuList |

Definition at line 269 of file shader.hh.

Referenced by AccessMem(), dispatchWorkgroups(), doFunctionalAccess(), functionalTLBAccess(), notifyCuSleep(), gem5::GPUCommandProcessor::performTimingRead(), prepareFlush(), prepareInvalidate(), registerCU(), and ~Shader().

◆ deferred_dispatches

|

private |

Definition at line 110 of file shader.hh.

Referenced by addDeferredDispatch(), and decNumOutstandingInvL2s().

◆ globalMemSize

◆ gpuCmdProc

| GPUCommandProcessor& gem5::Shader::gpuCmdProc |

Definition at line 271 of file shader.hh.

Referenced by decNumOutstandingInvL2s(), getGfxVersion(), and vramRequestorId().

◆ gpuTc

| ThreadContext* gem5::Shader::gpuTc |

Definition at line 124 of file shader.hh.

Referenced by functionalTLBAccess(), init(), mmap(), Shader(), and updateContext().

◆ hsail_mode

| hsail_mode_e gem5::Shader::hsail_mode |

◆ hwRegs

|

private |

Definition at line 92 of file shader.hh.

Referenced by getHwReg(), and setHwReg().

◆ impl_kern_end_rel

| int gem5::Shader::impl_kern_end_rel |

Definition at line 240 of file shader.hh.

Referenced by gem5::VegaISA::Inst_SOPP__S_ENDPGM::execute().

◆ impl_kern_launch_acq

◆ kernelExitRequested

|

private |

Definition at line 102 of file shader.hh.

Referenced by notifyCuSleep(), and requestKernelExitEvent().

◆ max_valu_insts

◆ n_cu

| int gem5::Shader::n_cu |

Definition at line 246 of file shader.hh.

Referenced by dispatchWorkgroups(), prepareInvalidate(), and ~Shader().

◆ n_cu_per_sqc

| int gem5::Shader::n_cu_per_sqc |

Definition at line 250 of file shader.hh.

Referenced by prepareInvalidate().

◆ n_wf

◆ nextSchedCu

| int gem5::Shader::nextSchedCu |

Definition at line 256 of file shader.hh.

Referenced by dispatchWorkgroups().

◆ num_outstanding_invl2s

|

private |

Definition at line 109 of file shader.hh.

Referenced by decNumOutstandingInvL2s(), getNumOutstandingInvL2s(), and incNumOutstandingInvL2s().

◆ progressInterval

| const Tick gem5::Shader::progressInterval |

Definition at line 279 of file shader.hh.

Referenced by getProgressInterval().

◆ sa_n

| uint32_t gem5::Shader::sa_n |

Definition at line 259 of file shader.hh.

Referenced by execScheduledAdds(), and ScheduleAdd().

◆ sa_val

| std::vector<int*> gem5::Shader::sa_val |

Definition at line 262 of file shader.hh.

Referenced by execScheduledAdds(), and ScheduleAdd().

◆ sa_when

| std::vector<uint64_t> gem5::Shader::sa_when |

Definition at line 264 of file shader.hh.

Referenced by execScheduledAdds(), and ScheduleAdd().

◆ sa_x

| std::vector<int32_t> gem5::Shader::sa_x |

Definition at line 266 of file shader.hh.

Referenced by execScheduledAdds(), and ScheduleAdd().

◆ shHiddenPrivateBaseVmid

|

private |

Definition at line 89 of file shader.hh.

Referenced by getHiddenPrivateBase(), and initShHiddenPrivateBase().

◆ stats

|

protected |

◆ systemHub

| AMDGPUSystemHub* gem5::Shader::systemHub |

Definition at line 273 of file shader.hh.

Referenced by gem5::ComputeUnit::ScalarDataPort::MemReqEvent::process(), and gem5::ComputeUnit::DataPort::processMemReqEvent().

◆ tickEvent

| EventFunctionWrapper gem5::Shader::tickEvent |

Definition at line 231 of file shader.hh.

Referenced by dispatchWorkgroups(), execScheduledAdds(), ScheduleAdd(), and Shader().

◆ timingSim

◆ total_valu_insts

◆ trace_vgpr_all

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:06:54 for gem5 by doxygen 1.14.0