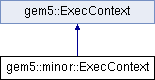

ExecContext bears the exec_context interface for Minor. More...

#include <exec_context.hh>

Public Member Functions | |

| ExecContext (MinorCPU &cpu_, SimpleThread &thread_, Execute &execute_, MinorDynInstPtr inst_) | |

| ~ExecContext () | |

| Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) override |

| Initiate a timing memory read operation. | |

| Fault | initiateMemMgmtCmd (Request::Flags flags) override |

| Initiate a memory management command with no valid address. | |

| Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable) override |

| For atomic-mode contexts, perform an atomic memory write operation. | |

| Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) | |

| RegVal | getRegOperand (const StaticInst *si, int idx) override |

| void | getRegOperand (const StaticInst *si, int idx, void *val) override |

| void * | getWritableRegOperand (const StaticInst *si, int idx) override |

| void | setRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setRegOperand (const StaticInst *si, int idx, const void *val) override |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| const PCStateBase & | pcState () const override |

| void | pcState (const PCStateBase &val) override |

| RegVal | readMiscRegNoEffect (int misc_reg) const |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a miscellaneous register, handling any architectural side effects due to reading that register. | |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a miscellaneous register, handling any architectural side effects due to writing that register. | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| ThreadContext * | tcBase () const override |

| Returns a pointer to the ThreadContext. | |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. | |

| void | setStCondFailures (unsigned int st_cond_failures) override |

| Sets the number of consecutive store conditional failures. | |

| ContextID | contextId () |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. | |

| BaseCPU * | getCpuPtr () |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| Public Member Functions inherited from gem5::ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Perform an atomic memory read operation. | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) | |

Public Attributes | |

| MinorCPU & | cpu |

| SimpleThread & | thread |

| ThreadState object, provides all the architectural state. | |

| Execute & | execute |

| The execute stage so we can peek at its contents. | |

| MinorDynInstPtr | inst |

| Instruction for the benefit of memory operations and for PC. | |

Detailed Description

ExecContext bears the exec_context interface for Minor.

This nicely separates that interface from other classes such as Pipeline, MinorCPU and DynMinorInst and makes it easier to see what state is accessed by it.

Definition at line 72 of file exec_context.hh.

Constructor & Destructor Documentation

◆ ExecContext()

|

inline |

Definition at line 86 of file exec_context.hh.

References cpu, DPRINTF, execute, inst, pcState(), setMemAccPredicate(), setPredicate(), and thread.

◆ ~ExecContext()

|

inline |

Definition at line 101 of file exec_context.hh.

References inst, readMemAccPredicate(), and readPredicate().

Member Function Documentation

◆ armMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 306 of file exec_context.hh.

References gem5::BaseCPU::armMonitor(), getCpuPtr(), and inst.

◆ contextId()

|

inline |

Definition at line 291 of file exec_context.hh.

References thread.

◆ demapPage()

|

inlineoverridevirtual |

Invalidate a page in the DTLB and ITLB.

Implements gem5::ExecContext.

Definition at line 296 of file exec_context.hh.

References thread, and gem5::MipsISA::vaddr.

◆ getAddrMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 324 of file exec_context.hh.

References gem5::BaseCPU::getCpuAddrMonitor(), getCpuPtr(), and inst.

◆ getCpuPtr()

|

inline |

Definition at line 301 of file exec_context.hh.

References cpu.

Referenced by armMonitor(), getAddrMonitor(), mwait(), and mwaitAtomic().

◆ getHtmTransactionalDepth()

|

inlineoverridevirtual |

◆ getHtmTransactionUid()

|

inlineoverridevirtual |

◆ getRegOperand() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 147 of file exec_context.hh.

References gem5::InvalidRegClass, gem5::X86ISA::reg, gem5::ArmISA::si, and thread.

◆ getRegOperand() [2/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 156 of file exec_context.hh.

References gem5::ArmISA::si, thread, and gem5::X86ISA::val.

◆ getWritableRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 162 of file exec_context.hh.

References gem5::ArmISA::si, and thread.

◆ inHtmTransactionalState()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 224 of file exec_context.hh.

◆ initiateMemAMO()

|

inlineoverridevirtual |

For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation)

Reimplemented from gem5::ExecContext.

Definition at line 137 of file exec_context.hh.

References gem5::X86ISA::addr, execute, and inst.

◆ initiateMemMgmtCmd()

|

inlineoverridevirtual |

Initiate a memory management command with no valid address.

Currently, these instructions need to bypass squashing in the O3 model Examples include HTM commands and TLBI commands. e.g. tell Ruby we're starting/stopping a HTM transaction, or tell Ruby to issue a TLBI operation

Implements gem5::ExecContext.

Definition at line 118 of file exec_context.hh.

References gem5::NoFault, and panic.

◆ initiateMemRead()

|

inlineoverridevirtual |

Initiate a timing memory read operation.

Must be overridden for exec contexts that support timing memory mode. Not pure virtual since exec contexts that only support atomic memory mode need not override (though in that case this function should never be called).

Reimplemented from gem5::ExecContext.

Definition at line 108 of file exec_context.hh.

References gem5::X86ISA::addr, execute, and inst.

◆ mwait()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 312 of file exec_context.hh.

References getCpuPtr(), inst, and gem5::BaseCPU::mwait().

◆ mwaitAtomic()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 318 of file exec_context.hh.

References getCpuPtr(), inst, gem5::BaseCPU::mwaitAtomic(), and thread.

◆ newHtmTransactionUid()

|

inlineoverridevirtual |

◆ pcState() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 240 of file exec_context.hh.

References thread.

Referenced by ExecContext().

◆ pcState() [2/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 246 of file exec_context.hh.

References thread, and gem5::X86ISA::val.

◆ readMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 195 of file exec_context.hh.

References thread.

Referenced by gem5::minor::Execute::executeMemRefInst(), gem5::minor::Execute::handleMemResponse(), and ~ExecContext().

◆ readMiscReg()

|

inlineoverridevirtual |

Reads a miscellaneous register, handling any architectural side effects due to reading that register.

Implements gem5::ExecContext.

Definition at line 258 of file exec_context.hh.

References thread.

◆ readMiscRegNoEffect()

|

inline |

Definition at line 252 of file exec_context.hh.

References thread.

◆ readMiscRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 270 of file exec_context.hh.

References gem5::MiscRegClass, gem5::X86ISA::reg, gem5::ArmISA::si, and thread.

◆ readPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 183 of file exec_context.hh.

References thread.

Referenced by gem5::minor::Execute::commitInst(), gem5::minor::Execute::executeMemRefInst(), gem5::minor::Execute::handleMemResponse(), and ~ExecContext().

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements gem5::ExecContext.

Definition at line 288 of file exec_context.hh.

◆ setMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 201 of file exec_context.hh.

References thread, and gem5::X86ISA::val.

Referenced by gem5::minor::LSQ::LSQRequest::completeDisabledMemAccess(), and ExecContext().

◆ setMiscReg()

|

inlineoverridevirtual |

Sets a miscellaneous register, handling any architectural side effects due to writing that register.

Implements gem5::ExecContext.

Definition at line 264 of file exec_context.hh.

References thread, and gem5::X86ISA::val.

◆ setMiscRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 278 of file exec_context.hh.

References gem5::MiscRegClass, gem5::X86ISA::reg, gem5::ArmISA::si, thread, and gem5::X86ISA::val.

◆ setPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 189 of file exec_context.hh.

References thread, and gem5::X86ISA::val.

Referenced by ExecContext().

◆ setRegOperand() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 177 of file exec_context.hh.

References gem5::ArmISA::si, thread, and gem5::X86ISA::val.

◆ setRegOperand() [2/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 168 of file exec_context.hh.

References gem5::InvalidRegClass, gem5::X86ISA::reg, gem5::ArmISA::si, thread, and gem5::X86ISA::val.

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements gem5::ExecContext.

Definition at line 289 of file exec_context.hh.

◆ tcBase()

|

inlineoverridevirtual |

Returns a pointer to the ThreadContext.

Implements gem5::ExecContext.

Definition at line 285 of file exec_context.hh.

References thread.

◆ writeMem()

|

inlineoverridevirtual |

For atomic-mode contexts, perform an atomic memory write operation.

For timing-mode contexts, initiate a timing memory write operation.

Implements gem5::ExecContext.

Definition at line 126 of file exec_context.hh.

References gem5::X86ISA::addr, data, execute, and inst.

Member Data Documentation

◆ cpu

| MinorCPU& gem5::minor::ExecContext::cpu |

Definition at line 75 of file exec_context.hh.

Referenced by ExecContext(), and getCpuPtr().

◆ execute

| Execute& gem5::minor::ExecContext::execute |

The execute stage so we can peek at its contents.

Definition at line 81 of file exec_context.hh.

Referenced by ExecContext(), initiateMemAMO(), initiateMemRead(), and writeMem().

◆ inst

| MinorDynInstPtr gem5::minor::ExecContext::inst |

Instruction for the benefit of memory operations and for PC.

Definition at line 84 of file exec_context.hh.

Referenced by armMonitor(), ExecContext(), getAddrMonitor(), initiateMemAMO(), initiateMemRead(), mwait(), mwaitAtomic(), writeMem(), and ~ExecContext().

◆ thread

| SimpleThread& gem5::minor::ExecContext::thread |

ThreadState object, provides all the architectural state.

Definition at line 78 of file exec_context.hh.

Referenced by contextId(), demapPage(), ExecContext(), getRegOperand(), getRegOperand(), getWritableRegOperand(), mwaitAtomic(), pcState(), pcState(), readMemAccPredicate(), readMiscReg(), readMiscRegNoEffect(), readMiscRegOperand(), readPredicate(), setMemAccPredicate(), setMiscReg(), setMiscRegOperand(), setPredicate(), setRegOperand(), setRegOperand(), and tcBase().

The documentation for this class was generated from the following file:

- cpu/minor/exec_context.hh

Generated on Sat Oct 18 2025 08:06:59 for gem5 by doxygen 1.14.0