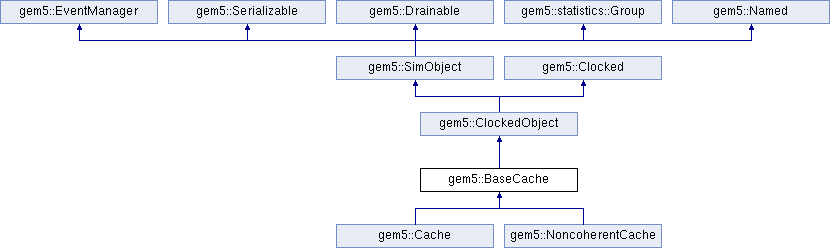

A basic cache interface. More...

#include <base.hh>

Classes | |

| struct | CacheAccessorImpl |

| struct | CacheCmdStats |

| class | CacheReqPacketQueue |

| Override the default behaviour of sendDeferredPacket to enable the memory-side cache port to also send requests based on the current MSHR status. More... | |

| class | CacheRequestPort |

| A cache request port is used for the memory-side port of the cache, and in addition to the basic timing port that only sends response packets through a transmit list, it also offers the ability to schedule and send request packets (requests & writebacks). More... | |

| class | CacheResponsePort |

| A cache response port is used for the CPU-side port of the cache, and it is basically a simple timing port that uses a transmit list for responses to the CPU (or connected requestor). More... | |

| struct | CacheStats |

| class | CpuSidePort |

| The CPU-side port extends the base cache response port with access functions for functional, atomic and timing requests. More... | |

| class | MemSidePort |

| The memory-side port extends the base cache request port with access functions for functional, atomic and timing snoops. More... | |

Public Types | |

| enum | BlockedCause { Blocked_NoMSHRs = MSHRQueue_MSHRs , Blocked_NoWBBuffers = MSHRQueue_WriteBuffer , Blocked_NoTargets , NUM_BLOCKED_CAUSES } |

| Reasons for caches to be blocked. More... | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| void | regProbePoints () override |

| Registers probes. | |

| BaseCache (const BaseCacheParams &p, unsigned blk_size) | |

| ~BaseCache () | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port with a given name and index. | |

| unsigned | getBlockSize () const |

| Query block size of a cache. | |

| const AddrRangeList & | getAddrRanges () const |

| MSHR * | allocateMissBuffer (PacketPtr pkt, Tick time, bool sched_send=true) |

| void | allocateWriteBuffer (PacketPtr pkt, Tick time) |

| bool | isBlocked () const |

| Returns true if the cache is blocked for accesses. | |

| void | setBlocked (BlockedCause cause) |

| Marks the access path of the cache as blocked for the given cause. | |

| void | clearBlocked (BlockedCause cause) |

| Marks the cache as unblocked for the given cause. | |

| void | schedMemSideSendEvent (Tick time) |

| Schedule a send event for the memory-side port. | |

| bool | inCache (Addr addr, bool is_secure) const |

| bool | hasBeenPrefetched (Addr addr, bool is_secure) const |

| bool | hasBeenPrefetched (Addr addr, bool is_secure, RequestorID requestor) const |

| bool | inMissQueue (Addr addr, bool is_secure) const |

| void | incMissCount (PacketPtr pkt) |

| void | incHitCount (PacketPtr pkt) |

| bool | coalesce () const |

| Checks if the cache is coalescing writes. | |

| void | writebackVisitor (CacheBlk &blk) |

| Cache block visitor that writes back dirty cache blocks using functional writes. | |

| void | invalidateVisitor (CacheBlk &blk) |

| Cache block visitor that invalidates all blocks in the cache. | |

| virtual bool | sendMSHRQueuePacket (MSHR *mshr) |

| Take an MSHR, turn it into a suitable downstream packet, and send it out. | |

| bool | sendWriteQueuePacket (WriteQueueEntry *wq_entry) |

| Similar to sendMSHR, but for a write-queue entry instead. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize the state of the caches. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

Public Attributes | |

| System * | system |

| System we are currently operating in. | |

| gem5::BaseCache::CacheStats | stats |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

Protected Types | |

| enum | MSHRQueueIndex { MSHRQueue_MSHRs , MSHRQueue_WriteBuffer } |

| Indexes to enumerate the MSHR queues. More... | |

Protected Member Functions | |

| void | markInService (MSHR *mshr, bool pending_modified_resp) |

| Mark a request as in service (sent downstream in the memory system), effectively making this MSHR the ordering point. | |

| void | markInService (WriteQueueEntry *entry) |

| bool | allocOnFill (MemCmd cmd) const |

| Determine whether we should allocate on a fill or not. | |

| Addr | regenerateBlkAddr (CacheBlk *blk) |

| Regenerate block address using tags. | |

| Cycles | calculateTagOnlyLatency (const uint32_t delay, const Cycles lookup_lat) const |

| Calculate latency of accesses that only touch the tag array. | |

| Cycles | calculateAccessLatency (const CacheBlk *blk, const uint32_t delay, const Cycles lookup_lat) const |

| Calculate access latency in ticks given a tag lookup latency, and whether access was a hit or miss. | |

| virtual bool | access (PacketPtr pkt, CacheBlk *&blk, Cycles &lat, PacketList &writebacks) |

| Does all the processing necessary to perform the provided request. | |

| virtual void | handleTimingReqHit (PacketPtr pkt, CacheBlk *blk, Tick request_time) |

| virtual void | handleTimingReqMiss (PacketPtr pkt, CacheBlk *blk, Tick forward_time, Tick request_time)=0 |

| void | handleTimingReqMiss (PacketPtr pkt, MSHR *mshr, CacheBlk *blk, Tick forward_time, Tick request_time) |

| virtual void | recvTimingReq (PacketPtr pkt) |

| Performs the access specified by the request. | |

| void | handleUncacheableWriteResp (PacketPtr pkt) |

| Handling the special case of uncacheable write responses to make recvTimingResp less cluttered. | |

| virtual void | serviceMSHRTargets (MSHR *mshr, const PacketPtr pkt, CacheBlk *blk)=0 |

| Service non-deferred MSHR targets using the received response. | |

| virtual void | recvTimingResp (PacketPtr pkt) |

| Handles a response (cache line fill/write ack) from the bus. | |

| virtual void | recvTimingSnoopReq (PacketPtr pkt)=0 |

| Snoops bus transactions to maintain coherence. | |

| virtual void | recvTimingSnoopResp (PacketPtr pkt)=0 |

| Handle a snoop response. | |

| virtual Cycles | handleAtomicReqMiss (PacketPtr pkt, CacheBlk *&blk, PacketList &writebacks)=0 |

| Handle a request in atomic mode that missed in this cache. | |

| virtual Tick | recvAtomic (PacketPtr pkt) |

| Performs the access specified by the request. | |

| virtual Tick | recvAtomicSnoop (PacketPtr pkt)=0 |

| Snoop for the provided request in the cache and return the estimated time taken. | |

| virtual void | functionalAccess (PacketPtr pkt, bool from_cpu_side) |

| Performs the access specified by the request. | |

| void | updateBlockData (CacheBlk *blk, const PacketPtr cpkt, bool has_old_data) |

| Update the data contents of a block. | |

| void | cmpAndSwap (CacheBlk *blk, PacketPtr pkt) |

| Handle doing the Compare and Swap function for SPARC. | |

| QueueEntry * | getNextQueueEntry () |

| Return the next queue entry to service, either a pending miss from the MSHR queue, a buffered write from the write buffer, or something from the prefetcher. | |

| virtual void | doWritebacks (PacketList &writebacks, Tick forward_time)=0 |

| Insert writebacks into the write buffer. | |

| virtual void | doWritebacksAtomic (PacketList &writebacks)=0 |

| Send writebacks down the memory hierarchy in atomic mode. | |

| virtual PacketPtr | createMissPacket (PacketPtr cpu_pkt, CacheBlk *blk, bool needs_writable, bool is_whole_line_write) const =0 |

| Create an appropriate downstream bus request packet. | |

| void | writebackTempBlockAtomic () |

| Send the outstanding tempBlock writeback. | |

| bool | updateCompressionData (CacheBlk *&blk, const uint64_t *data, PacketList &writebacks) |

| When a block is overwriten, its compression information must be updated, and it may need to be recompressed. | |

| virtual void | satisfyRequest (PacketPtr pkt, CacheBlk *blk, bool deferred_response=false, bool pending_downgrade=false) |

| Perform any necessary updates to the block and perform any data exchange between the packet and the block. | |

| void | maintainClusivity (bool from_cache, CacheBlk *blk) |

| Maintain the clusivity of this cache by potentially invalidating a block. | |

| bool | handleEvictions (std::vector< CacheBlk * > &evict_blks, PacketList &writebacks) |

| Try to evict the given blocks. | |

| CacheBlk * | handleFill (PacketPtr pkt, CacheBlk *blk, PacketList &writebacks, bool allocate) |

| Handle a fill operation caused by a received packet. | |

| CacheBlk * | allocateBlock (const PacketPtr pkt, PacketList &writebacks) |

| Allocate a new block and perform any necessary writebacks. | |

| virtual PacketPtr | evictBlock (CacheBlk *blk)=0 |

| Evict a cache block. | |

| void | evictBlock (CacheBlk *blk, PacketList &writebacks) |

| Evict a cache block. | |

| void | invalidateBlock (CacheBlk *blk) |

| Invalidate a cache block. | |

| PacketPtr | writebackBlk (CacheBlk *blk) |

| Create a writeback request for the given block. | |

| PacketPtr | writecleanBlk (CacheBlk *blk, Request::Flags dest, PacketId id) |

| Create a writeclean request for the given block. | |

| virtual void | memWriteback () override |

| Write back dirty blocks in the cache using functional accesses. | |

| virtual void | memInvalidate () override |

| Invalidates all blocks in the cache. | |

| bool | isDirty () const |

| Determine if there are any dirty blocks in the cache. | |

| bool | inRange (Addr addr) const |

| Determine if an address is in the ranges covered by this cache. | |

| Tick | nextQueueReadyTime () const |

| Find next request ready time from among possible sources. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

Protected Attributes | |

| CpuSidePort | cpuSidePort |

| MemSidePort | memSidePort |

| gem5::BaseCache::CacheAccessorImpl | accessor |

| MSHRQueue | mshrQueue |

| Miss status registers. | |

| WriteQueue | writeBuffer |

| Write/writeback buffer. | |

| BaseTags * | tags |

| Tag and data Storage. | |

| compression::Base * | compressor |

| Compression method being used. | |

| partitioning_policy::PartitionManager * | partitionManager |

| Partitioning manager. | |

| prefetch::Base * | prefetcher |

| Prefetcher. | |

| ProbePointArg< CacheAccessProbeArg > * | ppHit |

| To probe when a cache hit occurs. | |

| ProbePointArg< CacheAccessProbeArg > * | ppMiss |

| To probe when a cache miss occurs. | |

| ProbePointArg< CacheAccessProbeArg > * | ppFill |

| To probe when a cache fill occurs. | |

| ProbePointArg< CacheDataUpdateProbeArg > * | ppDataUpdate |

| To probe when the contents of a block are updated. | |

| WriteAllocator *const | writeAllocator |

| The writeAllocator drive optimizations for streaming writes. | |

| TempCacheBlk * | tempBlock |

| Temporary cache block for occasional transitory use. | |

| std::unique_ptr< Packet > | pendingDelete |

| Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call. | |

| const bool | writebackClean |

| Determine if clean lines should be written back or not. | |

| PacketPtr | tempBlockWriteback |

| Writebacks from the tempBlock, resulting on the response path in atomic mode, must happen after the call to recvAtomic has finished (for the right ordering of the packets). | |

| EventFunctionWrapper | writebackTempBlockAtomicEvent |

| An event to writeback the tempBlock after recvAtomic finishes. | |

| const unsigned | blkSize |

| Block size of this cache. | |

| const Cycles | lookupLatency |

| The latency of tag lookup of a cache. | |

| const Cycles | dataLatency |

| The latency of data access of a cache. | |

| const Cycles | forwardLatency |

| This is the forward latency of the cache. | |

| const Cycles | fillLatency |

| The latency to fill a cache block. | |

| const Cycles | responseLatency |

| The latency of sending reponse to its upper level cache/core on a linefill. | |

| const bool | sequentialAccess |

| Whether tags and data are accessed sequentially. | |

| const int | numTarget |

| The number of targets for each MSHR. | |

| bool | forwardSnoops |

| Do we forward snoops from mem side port through to cpu side port? | |

| const enums::Clusivity | clusivity |

| Clusivity with respect to the upstream cache, determining if we fill into both this cache and the cache above on a miss. | |

| const bool | isReadOnly |

| Is this cache read only, for example the instruction cache, or table-walker cache. | |

| const bool | replaceExpansions |

| when a data expansion of a compressed block happens it will not be able to co-allocate where it is at anymore. | |

| const bool | moveContractions |

| Similar to data expansions, after a block improves its compression, it may need to be moved elsewhere compatible with the new compression factor, or, if not required by the compaction method, it may be moved to co-allocate with an existing block and thus free an entry. | |

| uint8_t | blocked |

| Bit vector of the blocking reasons for the access path. | |

| uint64_t | order |

| Increasing order number assigned to each incoming request. | |

| Cycles | blockedCycle |

| Stores time the cache blocked for statistics. | |

| MSHR * | noTargetMSHR |

| Pointer to the MSHR that has no targets. | |

| Counter | missCount |

| The number of misses to trigger an exit event. | |

| const AddrRangeList | addrRanges |

| The address range to which the cache responds on the CPU side. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

Detailed Description

A basic cache interface.

Implements some common functions for speed.

Member Enumeration Documentation

◆ BlockedCause

◆ MSHRQueueIndex

|

protected |

Constructor & Destructor Documentation

◆ BaseCache()

| gem5::BaseCache::BaseCache | ( | const BaseCacheParams & | p, |

| unsigned | blk_size ) |

Definition at line 81 of file base.cc.

References accessor, gem5::ClockedObject::ClockedObject(), compressor, cpuSidePort, memSidePort, mshrQueue, gem5::Named::name(), gem5::MipsISA::p, partitionManager, prefetcher, tags, tempBlockWriteback, writeAllocator, writebackClean, writebackTempBlockAtomic(), writebackTempBlockAtomicEvent, and writeBuffer.

Referenced by gem5::Cache::Cache(), gem5::BaseCache::CacheAccessorImpl::CacheAccessorImpl(), gem5::BaseCache::CacheCmdStats::CacheCmdStats(), gem5::BaseCache::CacheReqPacketQueue::CacheReqPacketQueue(), gem5::BaseCache::CacheResponsePort::CacheResponsePort(), gem5::BaseCache::CacheStats::CacheStats(), gem5::BaseCache::CpuSidePort::CpuSidePort(), gem5::BaseCache::MemSidePort::MemSidePort(), and gem5::NoncoherentCache::NoncoherentCache().

◆ ~BaseCache()

Member Function Documentation

◆ access()

|

protectedvirtual |

Does all the processing necessary to perform the provided request.

- Parameters

-

pkt The memory request to perform. blk The cache block to be updated. lat The latency of the access. writebacks List for any writebacks that need to be performed.

- Returns

- Boolean indicating whether the request was satisfied.

Reimplemented in gem5::Cache, and gem5::NoncoherentCache.

Definition at line 1244 of file base.cc.

References allocateBlock(), blkSize, calculateAccessLatency(), calculateTagOnlyLatency(), gem5::MemCmd::CleanEvict, gem5::Packet::clearBlockCached(), gem5::Clocked::clockEdge(), gem5::Packet::cmd, compressor, gem5::Clocked::cyclesToTicks(), gem5::CacheBlk::DirtyBit, DPRINTF, fillLatency, gem5::Packet::fromCache(), gem5_assert, gem5::Packet::getAddr(), gem5::Packet::getConstPtr(), gem5::WriteQueueEntry::getNumTargets(), gem5::Packet::getSize(), gem5::WriteQueueEntry::getTarget(), gem5::Packet::hasSharers(), gem5::Packet::headerDelay, incHitCount(), incMissCount(), invalidateBlock(), gem5::Packet::isCleanEviction(), gem5::Packet::isEviction(), gem5::Packet::isLLSC(), gem5::Packet::isRead(), isReadOnly, gem5::Packet::isRequest(), gem5::Packet::isSecure(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::Packet::isWrite(), gem5::Packet::isWriteback(), maintainClusivity(), markInService(), mshrQueue, gem5::Named::name(), gem5::Packet::needsResponse(), gem5::Packet::needsWritable(), gem5::Packet::payloadDelay, gem5::QueueEntry::Target::pkt, gem5::CacheBlk::print(), gem5::Packet::print(), gem5::CacheBlk::ReadableBit, gem5::Packet::req, satisfyRequest(), gem5::CacheBlk::setCoherenceBits(), gem5::CacheBlk::setWhenReady(), tags, updateBlockData(), updateCompressionData(), gem5::CacheBlk::WritableBit, gem5::MemCmd::WritebackClean, gem5::MemCmd::WritebackDirty, writeBuffer, gem5::MemCmd::WriteClean, and gem5::Packet::writeThrough().

Referenced by gem5::Cache::access(), gem5::NoncoherentCache::access(), recvAtomic(), and recvTimingReq().

◆ allocateBlock()

|

protected |

Allocate a new block and perform any necessary writebacks.

Find a victim block and if necessary prepare writebacks for any existing data. May return nullptr if there are no replaceable blocks. If a replaceable block is found, it inserts the new block in its place. The new block, however, is not set as valid yet.

- Parameters

-

pkt Packet holding the address to update writebacks A list of writeback packets for the evicted blocks

- Returns

- the allocated block

Definition at line 1621 of file base.cc.

References gem5::X86ISA::addr, blkSize, compressor, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getConstPtr(), handleEvictions(), gem5::Packet::hasData(), gem5::Packet::isSecure(), partitionManager, gem5::CacheBlk::print(), and tags.

Referenced by access(), and handleFill().

◆ allocateMissBuffer()

|

inline |

Definition at line 1179 of file base.hh.

References allocOnFill(), blkSize, gem5::Packet::cmd, gem5::Packet::getBlockAddr(), mshrQueue, MSHRQueue_MSHRs, order, schedMemSideSendEvent(), and setBlocked().

Referenced by getNextQueueEntry(), handleTimingReqHit(), handleTimingReqMiss(), and gem5::Cache::handleTimingReqMiss().

◆ allocateWriteBuffer()

Definition at line 1197 of file base.hh.

References blkSize, gem5::MemCmd::CleanEvict, gem5::Packet::cmd, compressor, DPRINTF, gem5::Packet::getBlockAddr(), gem5::QueueEntry::inService, gem5::Packet::isSecure(), gem5::Packet::isWrite(), MSHRQueue_WriteBuffer, order, gem5::Packet::payloadDelay, gem5::Packet::print(), schedMemSideSendEvent(), setBlocked(), and writeBuffer.

Referenced by gem5::Cache::doWritebacks(), gem5::NoncoherentCache::doWritebacks(), handleTimingReqMiss(), and gem5::Cache::handleTimingReqMiss().

◆ allocOnFill()

|

inlineprotected |

Determine whether we should allocate on a fill or not.

If this cache is mostly inclusive with regards to the upstream cache(s) we always allocate (for any non-forwarded and cacheable requests). In the case of a mostly exclusive cache, we allocate on fill if the packet did not come from a cache, thus if we: are dealing with a whole-line write (the latter behaves much like a writeback), the original target packet came from a non-caching source, or if we are performing a prefetch or LLSC.

- Parameters

-

cmd Command of the incoming requesting packet

- Returns

- Whether we should allocate on the fill

Definition at line 447 of file base.hh.

References clusivity, gem5::MemCmd::isLLSC(), gem5::MemCmd::isPrefetch(), gem5::MemCmd::ReadReq, gem5::MemCmd::WriteLineReq, and gem5::MemCmd::WriteReq.

Referenced by allocateMissBuffer(), gem5::Cache::handleAtomicReqMiss(), gem5::NoncoherentCache::handleAtomicReqMiss(), and handleTimingReqMiss().

◆ calculateAccessLatency()

|

protected |

Calculate access latency in ticks given a tag lookup latency, and whether access was a hit or miss.

- Parameters

-

blk The cache block that was accessed. delay The delay until the packet's metadata is present. lookup_lat Latency of the respective tag lookup.

- Returns

- The number of ticks that pass due to a block access.

Definition at line 1210 of file base.cc.

References calculateTagOnlyLatency(), gem5::curTick(), dataLatency, gem5::CacheBlk::getWhenReady(), sequentialAccess, gem5::Clocked::tick, and gem5::Clocked::ticksToCycles().

Referenced by access().

◆ calculateTagOnlyLatency()

|

protected |

Calculate latency of accesses that only touch the tag array.

- See also

- calculateAccessLatency

- Parameters

-

delay The delay until the packet's metadata is present. lookup_lat Latency of the respective tag lookup.

- Returns

- The number of ticks that pass due to a tag-only access.

Definition at line 1201 of file base.cc.

References gem5::Clocked::ticksToCycles().

Referenced by access(), and calculateAccessLatency().

◆ clearBlocked()

|

inline |

Marks the cache as unblocked for the given cause.

This also clears the blocked flags in the appropriate interfaces.

- Parameters

-

cause The newly unblocked cause.

- Warning

- Calling this function can cause a blocked request on the bus to access the cache. The cache must be in a state to handle that request.

Definition at line 1261 of file base.hh.

References blocked, blockedCycle, cpuSidePort, gem5::Clocked::curCycle(), DPRINTF, and stats.

Referenced by markInService(), markInService(), recvTimingResp(), and gem5::Cache::sendMSHRQueuePacket().

◆ cmpAndSwap()

Handle doing the Compare and Swap function for SPARC.

Definition at line 804 of file base.cc.

References accessor, blkSize, gem5::CacheBlk::data, gem5::CacheBlk::DirtyBit, gem5::Packet::getOffset(), gem5::Packet::getSize(), gem5::CacheBlk::getSrcRequestorId(), gem5::Packet::isRequest(), gem5::TaggedEntry::isSecure(), gem5::CacheDataUpdateProbeArg::newData, gem5::ArmISA::offset, gem5::CacheDataUpdateProbeArg::oldData, panic, ppDataUpdate, regenerateBlkAddr(), gem5::Packet::req, gem5::CacheBlk::setCoherenceBits(), gem5::Packet::setData(), and gem5::Packet::writeData().

Referenced by satisfyRequest().

◆ coalesce()

| bool gem5::BaseCache::coalesce | ( | ) | const |

Checks if the cache is coalescing writes.

- Returns

- True if the cache is coalescing writes

Definition at line 1825 of file base.cc.

References writeAllocator.

◆ createMissPacket()

|

protectedpure virtual |

Create an appropriate downstream bus request packet.

Creates a new packet with the request to be send to the memory below, or nullptr if the current request in cpu_pkt should just be forwarded on.

- Parameters

-

cpu_pkt The miss packet that needs to be satisfied. blk The referenced block, can be nullptr. needs_writable Indicates that the block must be writable even if the request in cpu_pkt doesn't indicate that. is_whole_line_write True if there are writes for the whole line

- Returns

- A packet send to the memory below

Implemented in gem5::Cache, and gem5::NoncoherentCache.

Referenced by sendMSHRQueuePacket().

◆ doWritebacks()

|

protectedpure virtual |

Insert writebacks into the write buffer.

Implemented in gem5::Cache, and gem5::NoncoherentCache.

Referenced by recvTimingReq(), recvTimingResp(), and sendMSHRQueuePacket().

◆ doWritebacksAtomic()

|

protectedpure virtual |

Send writebacks down the memory hierarchy in atomic mode.

Implemented in gem5::Cache, and gem5::NoncoherentCache.

Referenced by recvAtomic(), and writebackTempBlockAtomic().

◆ evictBlock() [1/2]

Evict a cache block.

Performs a writeback if necesssary and invalidates the block

- Parameters

-

blk Block to invalidate

- Returns

- A packet with the writeback, can be nullptr

Implemented in gem5::Cache, and gem5::NoncoherentCache.

References gem5::X86ISA::addr.

Referenced by gem5::Cache::access(), evictBlock(), handleEvictions(), recvAtomic(), and recvTimingResp().

◆ evictBlock() [2/2]

|

protected |

Evict a cache block.

Performs a writeback if necesssary and invalidates the block

- Parameters

-

blk Block to invalidate writebacks Return a list of packets with writebacks

Definition at line 1701 of file base.cc.

References evictBlock().

◆ functionalAccess()

|

protectedvirtual |

Performs the access specified by the request.

- Parameters

-

pkt The request to perform. fromCpuSide from the CPU side port or the memory side port

Reimplemented in gem5::NoncoherentCache.

Definition at line 719 of file base.cc.

References blkSize, cpuSidePort, gem5::CacheBlk::data, gem5::CacheBlk::DirtyBit, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getBlockAddr(), gem5::QueueEntry::inService, gem5::MSHR::isPendingModified(), gem5::Packet::isSecure(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::Packet::makeResponse(), memSidePort, mshrQueue, gem5::Named::name(), gem5::Packet::popLabel(), gem5::Packet::print(), gem5::Packet::pushLabel(), tags, gem5::Packet::trySatisfyFunctional(), and writeBuffer.

Referenced by gem5::NoncoherentCache::functionalAccess().

◆ getAddrRanges()

|

inline |

Definition at line 1177 of file base.hh.

References addrRanges.

◆ getBlockSize()

|

inline |

◆ getNextQueueEntry()

|

protected |

Return the next queue entry to service, either a pending miss from the MSHR queue, a buffered write from the write buffer, or something from the prefetcher.

This function is responsible for prioritizing among those sources on the fly.

Definition at line 859 of file base.cc.

References allocateMissBuffer(), blkSize, gem5::curTick(), DPRINTF, gem5::Packet::getBlockAddr(), isBlocked(), gem5::Packet::isSecure(), mshrQueue, gem5::QueueEntry::order, prefetcher, gem5::Packet::req, stats, system, tags, and writeBuffer.

◆ getPort()

|

overridevirtual |

Get a port with a given name and index.

This is used at binding time and returns a reference to a protocol-agnostic port.

gem5 has a request and response port interface. All memory objects are connected together via ports. These ports provide a rigid interface between these memory objects. These ports implement three different memory system modes: timing, atomic, and functional. The most important mode is the timing mode and here timing mode is used for conducting cycle-level timing experiments. The other modes are only used in special circumstances and should not be used to conduct cycle-level timing experiments. The other modes are only used in special circumstances. These ports allow SimObjects to communicate with each other.

- Parameters

-

if_name Port name idx Index in the case of a VectorPort

- Returns

- A reference to the given port

Reimplemented from gem5::SimObject.

Definition at line 206 of file base.cc.

References cpuSidePort, gem5::SimObject::getPort(), and memSidePort.

◆ handleAtomicReqMiss()

|

protectedpure virtual |

Handle a request in atomic mode that missed in this cache.

Creates a downstream request, sends it to the memory below and handles the response. As we are in atomic mode all operations are performed immediately.

- Parameters

-

pkt The packet with the requests blk The referenced block writebacks A list with packets for any performed writebacks

- Returns

- Cycles for handling the request

Implemented in gem5::Cache, and gem5::NoncoherentCache.

Referenced by recvAtomic().

◆ handleEvictions()

|

protected |

Try to evict the given blocks.

If any of them is a transient eviction, that is, the block is present in the MSHR queue all evictions are cancelled since handling such cases has not been implemented.

- Parameters

-

evict_blks Blocks marked for eviction. writebacks List for any writebacks that need to be performed.

- Returns

- False if any of the evicted blocks is in transient state.

Definition at line 950 of file base.cc.

References evictBlock(), gem5::MSHR::isCleaning(), mshrQueue, gem5::MSHR::needsWritable(), regenerateBlkAddr(), stats, and gem5::CacheBlk::WritableBit.

Referenced by allocateBlock(), and updateCompressionData().

◆ handleFill()

|

protected |

Handle a fill operation caused by a received packet.

Populates a cache block and handles all outstanding requests for the satisfied fill request. This version takes two memory requests. One contains the fill data, the other is an optional target to satisfy. Note that the reason we return a list of writebacks rather than inserting them directly in the write buffer is that this function is called by both atomic and timing-mode accesses, and in atomic mode we don't mess with the write buffer (we just perform the writebacks atomically once the original request is complete).

- Parameters

-

pkt The memory request with the fill data. blk The cache block if it already exists. writebacks List for any writebacks that need to be performed. allocate Whether to allocate a block or use the temp block

- Returns

- Pointer to the new cache block.

Definition at line 1525 of file base.cc.

References gem5::X86ISA::addr, allocateBlock(), blkSize, gem5::Packet::cacheResponding(), gem5::Clocked::clockEdge(), gem5::Packet::cmd, gem5::CacheBlk::DirtyBit, DPRINTF, fillLatency, gem5_assert, gem5::Packet::getAddr(), gem5::Packet::getBlockAddr(), gem5::Packet::getSize(), gem5::Packet::hasData(), gem5::Packet::hasSharers(), gem5::Packet::headerDelay, gem5::MemCmd::InvalidateResp, gem5::Packet::isRead(), isReadOnly, gem5::Packet::isResponse(), gem5::Packet::isSecure(), gem5::TaggedEntry::isSecure(), gem5::TaggedEntry::isValid(), gem5::Named::name(), gem5::Packet::payloadDelay, gem5::CacheBlk::print(), gem5::CacheBlk::ReadableBit, regenerateBlkAddr(), gem5::CacheBlk::setCoherenceBits(), gem5::CacheBlk::setWhenReady(), tempBlock, updateBlockData(), gem5::CacheBlk::WritableBit, and writeBuffer.

Referenced by gem5::Cache::handleAtomicReqMiss(), gem5::NoncoherentCache::handleAtomicReqMiss(), and recvTimingResp().

◆ handleTimingReqHit()

|

protectedvirtual |

Reimplemented in gem5::Cache.

Definition at line 229 of file base.cc.

References allocateMissBuffer(), blkSize, gem5::CacheBlk::clearCoherenceBits(), gem5::Packet::cmd, cpuSidePort, gem5::curTick(), DPRINTF, gem5::Packet::getBlockAddr(), gem5::Packet::headerDelay, gem5::Packet::isLockedRMW(), gem5::Packet::isRead(), gem5::Packet::isSecure(), gem5::Packet::isWrite(), gem5::MemCmd::LockedRMWWriteResp, gem5::Packet::makeTimingResponse(), mshrQueue, gem5::Packet::needsResponse(), gem5::Packet::payloadDelay, pendingDelete, gem5::Packet::print(), gem5::CacheBlk::ReadableBit, recvTimingResp(), gem5::Packet::req, gem5::Packet::senderState, and gem5::CacheBlk::WritableBit.

Referenced by gem5::Cache::handleTimingReqHit(), and recvTimingReq().

◆ handleTimingReqMiss() [1/2]

|

protectedpure virtual |

Implemented in gem5::Cache, and gem5::NoncoherentCache.

Referenced by gem5::Cache::handleTimingReqMiss(), gem5::NoncoherentCache::handleTimingReqMiss(), and recvTimingReq().

◆ handleTimingReqMiss() [2/2]

|

protected |

MSHR hit

- Note

- writebacks will be checked in getNextMSHR() for any conflicting requests to the same block

Definition at line 310 of file base.cc.

References allocateMissBuffer(), gem5::MSHR::allocateTarget(), allocateWriteBuffer(), allocOnFill(), blkSize, Blocked_NoTargets, gem5::MemCmd::CleanEvict, gem5::CacheBlk::clearCoherenceBits(), gem5::Packet::cmd, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getBlockAddr(), gem5::MSHR::getNumTargets(), gem5::Packet::getSize(), gem5::Packet::isDemand(), gem5::Packet::isEviction(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::Packet::isWrite(), gem5::Packet::isWriteback(), gem5::Packet::needsWritable(), noTargetMSHR, numTarget, order, pendingDelete, prefetcher, gem5::Packet::print(), gem5::CacheBlk::ReadableBit, gem5::Packet::req, setBlocked(), stats, system, gem5::CacheBlk::WritableBit, writeAllocator, and gem5::MemCmd::WriteClean.

◆ handleUncacheableWriteResp()

|

protected |

Handling the special case of uncacheable write responses to make recvTimingResp less cluttered.

Definition at line 481 of file base.cc.

References gem5::Clocked::clockEdge(), cpuSidePort, gem5::Packet::headerDelay, gem5::Packet::payloadDelay, and responseLatency.

Referenced by recvTimingResp().

◆ hasBeenPrefetched() [1/2]

|

inline |

Definition at line 1289 of file base.hh.

References gem5::X86ISA::addr, tags, and gem5::CacheBlk::wasPrefetched().

◆ hasBeenPrefetched() [2/2]

|

inline |

Definition at line 1294 of file base.hh.

References gem5::X86ISA::addr, gem5::CacheBlk::getSrcRequestorId(), tags, and gem5::CacheBlk::wasPrefetched().

◆ inCache()

|

inline |

Definition at line 1285 of file base.hh.

References gem5::X86ISA::addr, and tags.

◆ incHitCount()

|

inline |

◆ incMissCount()

|

inline |

Definition at line 1305 of file base.hh.

References gem5::exitSimLoop(), missCount, gem5::Packet::req, stats, and system.

Referenced by access().

◆ init()

|

overridevirtual |

init() is called after all C++ SimObjects have been created and all ports are connected.

Initializations that are independent of unserialization but rely on a fully instantiated and connected SimObject graph should be done here.

Reimplemented from gem5::SimObject.

Definition at line 197 of file base.cc.

References cpuSidePort, fatal, forwardSnoops, memSidePort, and gem5::Named::name().

◆ inMissQueue()

|

inline |

Definition at line 1301 of file base.hh.

References gem5::X86ISA::addr, and mshrQueue.

◆ inRange()

|

protected |

Determine if an address is in the ranges covered by this cache.

This is useful to filter snoops.

- Parameters

-

addr Address to check against

- Returns

- If the address in question is in range

Definition at line 218 of file base.cc.

References gem5::X86ISA::addr, addrRanges, and gem5::MipsISA::r.

Referenced by gem5::Cache::recvAtomicSnoop(), and gem5::Cache::recvTimingSnoopReq().

◆ invalidateBlock()

|

protected |

Invalidate a cache block.

- Parameters

-

blk Block to invalidate

Definition at line 1681 of file base.cc.

References gem5::TaggedEntry::isValid(), prefetcher, tags, tempBlock, updateBlockData(), and gem5::CacheBlk::wasPrefetched().

Referenced by access(), gem5::Cache::evictBlock(), gem5::NoncoherentCache::evictBlock(), gem5::Cache::handleAtomicReqMiss(), gem5::Cache::handleSnoop(), invalidateVisitor(), maintainClusivity(), satisfyRequest(), and gem5::Cache::serviceMSHRTargets().

◆ invalidateVisitor()

| void gem5::BaseCache::invalidateVisitor | ( | CacheBlk & | blk | ) |

Cache block visitor that invalidates all blocks in the cache.

@warn Dirty cache lines will not be written back to memory.

Definition at line 1854 of file base.cc.

References gem5::CacheBlk::DirtyBit, invalidateBlock(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), and warn_once.

Referenced by memInvalidate().

◆ isBlocked()

|

inline |

Returns true if the cache is blocked for accesses.

Definition at line 1232 of file base.hh.

References blocked.

Referenced by getNextQueueEntry(), nextQueueReadyTime(), and recvTimingResp().

◆ isDirty()

|

protected |

Determine if there are any dirty blocks in the cache.

- Returns

- true if at least one block is dirty, false otherwise.

Definition at line 1818 of file base.cc.

References gem5::CacheBlk::DirtyBit, gem5::CacheBlk::isSet(), and tags.

Referenced by serialize().

◆ maintainClusivity()

|

protected |

Maintain the clusivity of this cache by potentially invalidating a block.

This method works in conjunction with satisfyRequest, but is separate to allow us to handle all MSHR targets before potentially dropping a block.

- Parameters

-

from_cache Whether we have dealt with a packet from a cache blk The block that should potentially be dropped

Definition at line 1513 of file base.cc.

References clusivity, gem5::CacheBlk::DirtyBit, invalidateBlock(), gem5::CacheBlk::isSet(), and gem5::TaggedEntry::isValid().

Referenced by access(), gem5::Cache::handleAtomicReqMiss(), gem5::NoncoherentCache::handleAtomicReqMiss(), and gem5::Cache::serviceMSHRTargets().

◆ markInService() [1/2]

|

inlineprotected |

Mark a request as in service (sent downstream in the memory system), effectively making this MSHR the ordering point.

Definition at line 414 of file base.hh.

References Blocked_NoMSHRs, clearBlocked(), and mshrQueue.

Referenced by access(), gem5::Cache::recvTimingSnoopReq(), sendMSHRQueuePacket(), gem5::Cache::sendMSHRQueuePacket(), and sendWriteQueuePacket().

◆ markInService() [2/2]

|

inlineprotected |

Definition at line 424 of file base.hh.

References Blocked_NoWBBuffers, clearBlocked(), and writeBuffer.

◆ memInvalidate()

|

overrideprotectedvirtual |

Invalidates all blocks in the cache.

@warn Dirty cache lines will not be written back to memory. Make sure to call functionalWriteback() first if you want the to write them to memory.

Reimplemented from gem5::SimObject.

Definition at line 1812 of file base.cc.

References invalidateVisitor(), and tags.

◆ memWriteback()

|

overrideprotectedvirtual |

Write back dirty blocks in the cache using functional accesses.

Reimplemented from gem5::SimObject.

Definition at line 1806 of file base.cc.

References tags, and writebackVisitor().

◆ nextQueueReadyTime()

|

protected |

Find next request ready time from among possible sources.

Definition at line 1867 of file base.cc.

References isBlocked(), mshrQueue, prefetcher, and writeBuffer.

◆ recvAtomic()

Performs the access specified by the request.

- Parameters

-

pkt The request to perform.

- Returns

- The number of ticks required for the access.

Reimplemented in gem5::Cache, and gem5::NoncoherentCache.

Definition at line 639 of file base.cc.

References access(), gem5::Clocked::clockPeriod(), gem5::curTick(), gem5::CacheBlk::DirtyBit, doWritebacksAtomic(), DPRINTF, evictBlock(), handleAtomicReqMiss(), gem5::Packet::id, gem5::Packet::isClean(), gem5::CacheBlk::isSet(), lookupLatency, gem5::Packet::makeAtomicResponse(), gem5::Packet::needsResponse(), gem5::CacheBlk::print(), gem5::Packet::print(), gem5::Packet::req, gem5::EventManager::schedule(), gem5::Packet::setSatisfied(), tempBlock, tempBlockWriteback, writebackTempBlockAtomic(), writebackTempBlockAtomicEvent, and writecleanBlk().

Referenced by gem5::Cache::recvAtomic(), and gem5::NoncoherentCache::recvAtomic().

◆ recvAtomicSnoop()

Snoop for the provided request in the cache and return the estimated time taken.

- Parameters

-

pkt The memory request to snoop

- Returns

- The number of ticks required for the snoop.

Implemented in gem5::Cache, and gem5::NoncoherentCache.

◆ recvTimingReq()

|

protectedvirtual |

Performs the access specified by the request.

- Parameters

-

pkt The request to perform.

Reimplemented in gem5::Cache, and gem5::NoncoherentCache.

Definition at line 408 of file base.cc.

References access(), accessor, gem5::CacheBlk::clearPrefetched(), gem5::Clocked::clockEdge(), gem5::Packet::cmd, doWritebacks(), DPRINTF, forwardLatency, gem5::Packet::getAddr(), handleTimingReqHit(), handleTimingReqMiss(), gem5::Packet::headerDelay, gem5::Packet::isSecure(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::MemCmd::LockedRMWWriteReq, gem5::MaxTick, gem5::Packet::payloadDelay, ppHit, ppMiss, prefetcher, gem5::CacheBlk::ReadableBit, schedMemSideSendEvent(), gem5::CacheBlk::setCoherenceBits(), tags, gem5::CacheBlk::wasPrefetched(), and gem5::CacheBlk::WritableBit.

Referenced by gem5::Cache::recvTimingReq(), and gem5::NoncoherentCache::recvTimingReq().

◆ recvTimingResp()

|

protectedvirtual |

Handles a response (cache line fill/write ack) from the bus.

- Parameters

-

pkt The response packet

Reimplemented in gem5::NoncoherentCache.

Definition at line 493 of file base.cc.

References accessor, gem5::MSHR::allocOnFill(), Blocked_NoMSHRs, Blocked_NoTargets, clearBlocked(), gem5::CacheBlk::clearCoherenceBits(), gem5::Clocked::clockEdge(), gem5::Packet::cmd, gem5::curTick(), doWritebacks(), DPRINTF, evictBlock(), forwardLatency, gem5::Packet::getAddr(), gem5::MSHR::getTarget(), handleFill(), handleUncacheableWriteResp(), gem5::MemCmd::HardPFResp, gem5::MSHR::hasLockedRMWReadTarget(), gem5::Packet::headerDelay, isBlocked(), gem5::Packet::isClean(), gem5::Packet::isError(), gem5::MSHR::isForward, gem5::Packet::isInvalidate(), gem5::Packet::isRead(), gem5::Packet::isResponse(), gem5::Packet::isSecure(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::Packet::isWrite(), gem5::MemCmd::LockedRMWWriteResp, gem5::MaxTick, mshrQueue, gem5::Named::name(), noTargetMSHR, panic_if, gem5::Packet::payloadDelay, gem5::QueueEntry::Target::pkt, gem5::Packet::popSenderState(), ppFill, prefetcher, gem5::Packet::print(), gem5::MSHR::promoteDeferredTargets(), gem5::MSHR::promoteReadable(), gem5::MSHR::promoteWritable(), gem5::CacheBlk::ReadableBit, gem5::QueueEntry::Target::recvTime, gem5::Packet::req, schedMemSideSendEvent(), serviceMSHRTargets(), gem5::CacheBlk::setCoherenceBits(), stats, system, tags, tempBlock, gem5::MemCmd::UpgradeResp, gem5::MSHR::wasWholeLineWrite, gem5::CacheBlk::WritableBit, and writeAllocator.

Referenced by handleTimingReqHit(), gem5::NoncoherentCache::recvTimingResp(), and gem5::Cache::recvTimingSnoopResp().

◆ recvTimingSnoopReq()

|

protectedpure virtual |

Snoops bus transactions to maintain coherence.

- Parameters

-

pkt The current bus transaction.

Implemented in gem5::Cache, and gem5::NoncoherentCache.

◆ recvTimingSnoopResp()

|

protectedpure virtual |

Handle a snoop response.

- Parameters

-

pkt Snoop response packet

Implemented in gem5::Cache, and gem5::NoncoherentCache.

◆ regenerateBlkAddr()

Regenerate block address using tags.

Block address regeneration depends on whether we're using a temporary block or not.

- Parameters

-

blk The block to regenerate address.

- Returns

- The block's address.

Definition at line 187 of file base.cc.

References tags, and tempBlock.

Referenced by gem5::Cache::cleanEvictBlk(), cmpAndSwap(), handleEvictions(), handleFill(), satisfyRequest(), updateBlockData(), updateCompressionData(), writebackBlk(), writebackVisitor(), and writecleanBlk().

◆ regProbePoints()

|

overridevirtual |

Registers probes.

Reimplemented from gem5::SimObject.

Definition at line 2525 of file base.cc.

References gem5::SimObject::getProbeManager(), ppDataUpdate, ppFill, ppHit, and ppMiss.

◆ satisfyRequest()

|

protectedvirtual |

Perform any necessary updates to the block and perform any data exchange between the packet and the block.

The flags of the packet are also set accordingly.

- Parameters

-

pkt Request packet from upstream that hit a block blk Cache block that the packet hit deferred_response Whether this request originally missed pending_downgrade Whether the writable flag is to be removed

Reimplemented in gem5::Cache, and gem5::NoncoherentCache.

Definition at line 1100 of file base.cc.

References accessor, blkSize, gem5::CacheBlk::checkWrite(), gem5::CacheBlk::clearCoherenceBits(), gem5::Packet::cmd, cmpAndSwap(), gem5::CacheBlk::data, gem5::CacheBlk::DirtyBit, DPRINTF, gem5::Packet::getAddr(), gem5::Packet::getAtomicOp(), gem5::Packet::getOffset(), gem5::Packet::getSize(), gem5::CacheBlk::getSrcRequestorId(), gem5::Packet::hasRespData(), gem5::Packet::hasSharers(), gem5::CacheDataUpdateProbeArg::hwPrefetched, invalidateBlock(), gem5::Packet::isAtomicOp(), gem5::Packet::isClean(), gem5::Packet::isInvalidate(), gem5::Packet::isLLSC(), gem5::Packet::isRead(), gem5::Packet::isRequest(), gem5::TaggedEntry::isSecure(), gem5::CacheBlk::isSet(), gem5::Packet::isUpgrade(), gem5::TaggedEntry::isValid(), gem5::Packet::isWrite(), gem5::CacheDataUpdateProbeArg::newData, gem5::ArmISA::offset, gem5::CacheDataUpdateProbeArg::oldData, ppDataUpdate, gem5::Packet::print(), regenerateBlkAddr(), gem5::Packet::setCacheResponding(), gem5::CacheBlk::setCoherenceBits(), gem5::Packet::setData(), gem5::Packet::setDataFromBlock(), gem5::MemCmd::SwapReq, tags, gem5::CacheBlk::trackLoadLocked(), updateBlockData(), gem5::CacheBlk::wasPrefetched(), and gem5::CacheBlk::WritableBit.

Referenced by access(), gem5::Cache::satisfyRequest(), and gem5::NoncoherentCache::satisfyRequest().

◆ schedMemSideSendEvent()

|

inline |

Schedule a send event for the memory-side port.

If already scheduled, this may reschedule the event at an earlier time. When the specified time is reached, the port is free to send either a response, a request, or a prefetch request.

- Parameters

-

time The time when to attempt sending a packet.

Definition at line 1280 of file base.hh.

References memSidePort.

Referenced by allocateMissBuffer(), allocateWriteBuffer(), recvTimingReq(), and recvTimingResp().

◆ sendMSHRQueuePacket()

|

virtual |

Take an MSHR, turn it into a suitable downstream packet, and send it out.

This construct allows a queue entry to choose a suitable approach based on its type.

- Parameters

-

mshr The MSHR to turn into a packet and send

- Returns

- True if the port is waiting for a retry

Reimplemented in gem5::Cache.

Definition at line 1884 of file base.cc.

References gem5::QueueEntry::blkAddr, blkSize, gem5::Packet::cacheResponding(), gem5::Clocked::clockPeriod(), createMissPacket(), gem5::CacheBlk::DirtyBit, doWritebacks(), DPRINTF, gem5::Packet::getSize(), gem5::MSHR::getTarget(), gem5::Packet::hasSharers(), gem5::Packet::id, gem5::Packet::isClean(), gem5::MSHR::isForward, gem5::QueueEntry::isSecure, gem5::CacheBlk::isSet(), gem5::MSHR::isWholeLineWrite(), gem5::Packet::isWrite(), markInService(), memSidePort, mshrQueue, gem5::MSHR::needsWritable(), gem5::QueueEntry::Target::pkt, gem5::CacheBlk::print(), gem5::Packet::print(), gem5::Packet::pushSenderState(), gem5::Packet::req, gem5::Packet::setSatisfied(), tags, writeAllocator, and writecleanBlk().

Referenced by gem5::Cache::sendMSHRQueuePacket(), and gem5::MSHR::sendPacket().

◆ sendWriteQueuePacket()

| bool gem5::BaseCache::sendWriteQueuePacket | ( | WriteQueueEntry * | wq_entry | ) |

Similar to sendMSHR, but for a write-queue entry instead.

Create the packet, and send it, and if successful also mark the entry in service.

- Parameters

-

wq_entry The write-queue entry to turn into a packet and send

- Returns

- True if the port is waiting for a retry

Definition at line 1987 of file base.cc.

References DPRINTF, gem5::WriteQueueEntry::getTarget(), markInService(), memSidePort, gem5::QueueEntry::Target::pkt, and gem5::Packet::print().

Referenced by gem5::WriteQueueEntry::sendPacket().

◆ serialize()

|

overridevirtual |

Serialize the state of the caches.

We currently don't support checkpointing cache state, so this panics.

Implements gem5::Serializable.

Definition at line 2011 of file base.cc.

References isDirty(), SERIALIZE_SCALAR, and warn.

◆ serviceMSHRTargets()

|

protectedpure virtual |

Service non-deferred MSHR targets using the received response.

Iterates through the list of targets that can be serviced with the current response.

- Parameters

-

mshr The MSHR that corresponds to the reponse pkt The response packet blk The reference block

Implemented in gem5::Cache, and gem5::NoncoherentCache.

Referenced by recvTimingResp().

◆ setBlocked()

|

inline |

Marks the access path of the cache as blocked for the given cause.

This also sets the blocked flag in the response interface.

- Parameters

-

cause The reason for the cache blocking.

Definition at line 1242 of file base.hh.

References blocked, blockedCycle, cpuSidePort, gem5::Clocked::curCycle(), DPRINTF, and stats.

Referenced by allocateMissBuffer(), allocateWriteBuffer(), and handleTimingReqMiss().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Implements gem5::Serializable.

Definition at line 2031 of file base.cc.

References fatal, and UNSERIALIZE_SCALAR.

◆ updateBlockData()

|

protected |

Update the data contents of a block.

When no packet is provided no data will be written to the block, which means that this was likely triggered by an invalidation.

- Parameters

-

blk The block being updated. cpkt The packet containing the new data. has_old_data Whether this block had data previously.

Definition at line 775 of file base.cc.

References accessor, blkSize, gem5::CacheBlk::data, gem5::CacheBlk::getSrcRequestorId(), gem5::CacheDataUpdateProbeArg::hwPrefetched, gem5::TaggedEntry::isSecure(), gem5::CacheDataUpdateProbeArg::newData, gem5::CacheDataUpdateProbeArg::oldData, ppDataUpdate, regenerateBlkAddr(), gem5::CacheBlk::wasPrefetched(), and gem5::Packet::writeDataToBlock().

Referenced by access(), handleFill(), invalidateBlock(), and satisfyRequest().

◆ updateCompressionData()

|

protected |

When a block is overwriten, its compression information must be updated, and it may need to be recompressed.

If the compression size changes, the block may either become smaller, in which case there is no side effect, or bigger (data expansion; fat write), in which case the block might not fit in its current location anymore. If that happens, there are usually two options to be taken:

- The co-allocated blocks must be evicted to make room for this block. Simpler, but ignores replacement data.

- The block itself is moved elsewhere (used in policies where the CF determines the location of the block).

This implementation uses the first approach.

Notice that this is only called for writebacks, which means that L1 caches (which see regular Writes), do not support compression.

- See also

- CompressedTags

- Parameters

-

blk The block to be overwriten. data A pointer to the data to be compressed (blk's new data). writebacks List for any writebacks that need to be performed.

- Returns

- Whether operation is successful or not.

Definition at line 987 of file base.cc.

References gem5::SectorBlk::blks, gem5::CompressionBlk::checkExpansionContraction(), compressor, data, gem5::CompressionBlk::DATA_CONTRACTION, gem5::CompressionBlk::DATA_EXPANSION, DPRINTF, gem5::CacheBlk::getPartitionId(), gem5::SectorSubBlk::getSectorBlock(), gem5::CompressionBlk::getSizeBits(), handleEvictions(), gem5::TaggedEntry::isSecure(), moveContractions, gem5::CacheBlk::print(), regenerateBlkAddr(), replaceExpansions, gem5::CompressionBlk::setDecompressionLatency(), gem5::CompressionBlk::setSizeBits(), stats, tags, and tempBlock.

Referenced by access().

◆ writebackBlk()

Create a writeback request for the given block.

- Parameters

-

blk The block to writeback.

- Returns

- The writeback request for the block.

Definition at line 1710 of file base.cc.

References gem5::Packet::allocate(), blkSize, gem5::CacheBlk::clearCoherenceBits(), compressor, gem5::CacheBlk::data, gem5::CacheBlk::DirtyBit, DPRINTF, gem5_assert, gem5::CacheBlk::getTaskId(), isReadOnly, gem5::TaggedEntry::isSecure(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), gem5::Packet::payloadDelay, gem5::Packet::print(), regenerateBlkAddr(), gem5::Request::SECURE, gem5::Packet::setDataFromBlock(), gem5::Packet::setHasSharers(), stats, gem5::Request::wbRequestorId, gem5::CacheBlk::WritableBit, gem5::MemCmd::WritebackClean, writebackClean, and gem5::MemCmd::WritebackDirty.

Referenced by gem5::Cache::evictBlock(), and gem5::NoncoherentCache::evictBlock().

◆ writebackTempBlockAtomic()

|

inlineprotected |

Send the outstanding tempBlock writeback.

To be called after recvAtomic finishes in cases where the block we filled is in fact the tempBlock, and now needs to be written back.

Definition at line 697 of file base.hh.

References doWritebacksAtomic(), and tempBlockWriteback.

Referenced by BaseCache(), and recvAtomic().

◆ writebackVisitor()

| void gem5::BaseCache::writebackVisitor | ( | CacheBlk & | blk | ) |

Cache block visitor that writes back dirty cache blocks using functional writes.

Definition at line 1831 of file base.cc.

References blkSize, gem5::CacheBlk::clearCoherenceBits(), gem5::CacheBlk::data, gem5::Packet::dataStatic(), gem5::CacheBlk::DirtyBit, gem5::Request::funcRequestorId, gem5::CacheBlk::getTaskId(), gem5::TaggedEntry::isSecure(), gem5::CacheBlk::isSet(), gem5::TaggedEntry::isValid(), memSidePort, regenerateBlkAddr(), gem5::Request::SECURE, and gem5::MemCmd::WriteReq.

Referenced by memWriteback().

◆ writecleanBlk()

|

protected |

Create a writeclean request for the given block.

Creates a request that writes the block to the cache below without evicting the block from the current cache.

- Parameters

-

blk The block to write clean. dest The destination of the write clean operation. id Use the given packet id for the write clean operation.

- Returns

- The generated write clean packet.

Definition at line 1760 of file base.cc.

References gem5::Packet::allocate(), blkSize, gem5::CacheBlk::clearCoherenceBits(), compressor, gem5::CacheBlk::data, gem5::CacheBlk::DirtyBit, DPRINTF, gem5::CacheBlk::getTaskId(), gem5::TaggedEntry::isSecure(), gem5::CacheBlk::isSet(), gem5::Packet::payloadDelay, gem5::Packet::print(), regenerateBlkAddr(), gem5::Request::SECURE, gem5::Packet::setDataFromBlock(), gem5::Packet::setHasSharers(), gem5::Packet::setWriteThrough(), gem5::Request::wbRequestorId, gem5::CacheBlk::WritableBit, and gem5::MemCmd::WriteClean.

Referenced by gem5::Cache::handleSnoop(), recvAtomic(), and sendMSHRQueuePacket().

Member Data Documentation

◆ accessor

|

protected |

Referenced by BaseCache(), cmpAndSwap(), recvTimingReq(), recvTimingResp(), satisfyRequest(), and updateBlockData().

◆ addrRanges

|

protected |

The address range to which the cache responds on the CPU side.

Normally this is all possible memory addresses.

Definition at line 988 of file base.hh.

Referenced by getAddrRanges(), and inRange().

◆ blkSize

|

protected |

Block size of this cache.

Definition at line 894 of file base.hh.

Referenced by access(), allocateBlock(), allocateMissBuffer(), allocateWriteBuffer(), gem5::Cache::cleanEvictBlk(), cmpAndSwap(), gem5::Cache::createMissPacket(), gem5::NoncoherentCache::createMissPacket(), gem5::Cache::doTimingSupplyResponse(), functionalAccess(), getBlockSize(), getNextQueueEntry(), gem5::Cache::handleAtomicReqMiss(), gem5::NoncoherentCache::handleAtomicReqMiss(), handleFill(), gem5::Cache::handleSnoop(), handleTimingReqHit(), handleTimingReqMiss(), gem5::Cache::handleTimingReqMiss(), gem5::NoncoherentCache::handleTimingReqMiss(), gem5::Cache::promoteWholeLineWrites(), gem5::Cache::recvTimingSnoopReq(), satisfyRequest(), gem5::Cache::satisfyRequest(), sendMSHRQueuePacket(), gem5::Cache::serviceMSHRTargets(), gem5::NoncoherentCache::serviceMSHRTargets(), updateBlockData(), writebackBlk(), writebackVisitor(), and writecleanBlk().

◆ blocked

|

protected |

Bit vector of the blocking reasons for the access path.

- See also

- BlockedCause

Definition at line 971 of file base.hh.

Referenced by clearBlocked(), isBlocked(), and setBlocked().

◆ blockedCycle

|

protected |

Stores time the cache blocked for statistics.

Definition at line 977 of file base.hh.

Referenced by clearBlocked(), and setBlocked().

◆ clusivity

|

protected |

Clusivity with respect to the upstream cache, determining if we fill into both this cache and the cache above on a miss.

Note that we currently do not support strict clusivity policies.

Definition at line 941 of file base.hh.

Referenced by allocOnFill(), gem5::Cache::createMissPacket(), and maintainClusivity().

◆ compressor

|

protected |

Compression method being used.

Definition at line 356 of file base.hh.

Referenced by access(), allocateBlock(), allocateWriteBuffer(), BaseCache(), gem5::Cache::handleSnoop(), updateCompressionData(), writebackBlk(), and writecleanBlk().

◆ cpuSidePort

|

protected |

Definition at line 317 of file base.hh.

Referenced by BaseCache(), clearBlocked(), functionalAccess(), getPort(), gem5::Cache::handleSnoop(), handleTimingReqHit(), gem5::Cache::handleTimingReqMiss(), handleUncacheableWriteResp(), init(), gem5::Cache::isCachedAbove(), gem5::Cache::sendMSHRQueuePacket(), gem5::Cache::serviceMSHRTargets(), gem5::NoncoherentCache::serviceMSHRTargets(), and setBlocked().

◆ dataLatency

|

protected |

The latency of data access of a cache.

It occurs when there is an access to the cache.

Definition at line 906 of file base.hh.

Referenced by calculateAccessLatency().

◆ fillLatency

|

protected |

The latency to fill a cache block.

Definition at line 916 of file base.hh.

Referenced by access(), and handleFill().

◆ forwardLatency

|

protected |

This is the forward latency of the cache.

It occurs when there is a cache miss and a request is forwarded downstream, in particular an outbound miss.

Definition at line 913 of file base.hh.

Referenced by gem5::Cache::doTimingSupplyResponse(), gem5::Cache::handleSnoop(), recvTimingReq(), recvTimingResp(), and gem5::Cache::recvTimingSnoopResp().

◆ forwardSnoops

|

protected |

Do we forward snoops from mem side port through to cpu side port?

Definition at line 934 of file base.hh.

Referenced by gem5::Cache::handleSnoop(), init(), gem5::Cache::isCachedAbove(), and gem5::Cache::sendMSHRQueuePacket().

◆ isReadOnly

|

protected |

Is this cache read only, for example the instruction cache, or table-walker cache.

A cache that is read only should never see any writes, and should never get any dirty data (and hence never have to do any writebacks).

Definition at line 949 of file base.hh.

Referenced by access(), gem5::Cache::access(), gem5::Cache::createMissPacket(), handleFill(), gem5::Cache::handleSnoop(), gem5::Cache::serviceMSHRTargets(), and writebackBlk().

◆ lookupLatency

|

protected |

The latency of tag lookup of a cache.

It occurs when there is an access to the cache.

Definition at line 900 of file base.hh.

Referenced by gem5::Cache::access(), recvAtomic(), gem5::Cache::recvAtomicSnoop(), and gem5::Cache::recvTimingSnoopReq().

◆ memSidePort

|

protected |

Definition at line 318 of file base.hh.

Referenced by BaseCache(), gem5::Cache::doTimingSupplyResponse(), gem5::Cache::doWritebacksAtomic(), gem5::NoncoherentCache::doWritebacksAtomic(), functionalAccess(), getPort(), gem5::Cache::handleAtomicReqMiss(), gem5::NoncoherentCache::handleAtomicReqMiss(), init(), gem5::Cache::recvAtomic(), gem5::Cache::recvTimingReq(), gem5::Cache::recvTimingSnoopResp(), schedMemSideSendEvent(), sendMSHRQueuePacket(), sendWriteQueuePacket(), and writebackVisitor().

◆ missCount

|

protected |

The number of misses to trigger an exit event.

Definition at line 983 of file base.hh.

Referenced by incMissCount().

◆ moveContractions

|

protected |

Similar to data expansions, after a block improves its compression, it may need to be moved elsewhere compatible with the new compression factor, or, if not required by the compaction method, it may be moved to co-allocate with an existing block and thus free an entry.

Definition at line 965 of file base.hh.

Referenced by updateCompressionData().

◆ mshrQueue

|

protected |

Miss status registers.

Definition at line 347 of file base.hh.

Referenced by access(), allocateMissBuffer(), BaseCache(), functionalAccess(), getNextQueueEntry(), handleEvictions(), handleTimingReqHit(), gem5::Cache::handleTimingReqMiss(), gem5::NoncoherentCache::handleTimingReqMiss(), inMissQueue(), markInService(), nextQueueReadyTime(), recvTimingResp(), gem5::Cache::recvTimingSnoopReq(), sendMSHRQueuePacket(), and gem5::Cache::sendMSHRQueuePacket().

◆ noTargetMSHR

|

protected |

Pointer to the MSHR that has no targets.

Definition at line 980 of file base.hh.

Referenced by handleTimingReqMiss(), and recvTimingResp().

◆ numTarget

|

protected |

The number of targets for each MSHR.

Definition at line 931 of file base.hh.

Referenced by handleTimingReqMiss(), and gem5::Cache::recvTimingSnoopReq().

◆ order

|

protected |

Increasing order number assigned to each incoming request.

Definition at line 974 of file base.hh.

Referenced by allocateMissBuffer(), allocateWriteBuffer(), handleTimingReqMiss(), and gem5::Cache::recvTimingSnoopReq().

◆ partitionManager

|

protected |

Partitioning manager.

Definition at line 359 of file base.hh.

Referenced by allocateBlock(), and BaseCache().

◆ pendingDelete

|

protected |

Upstream caches need this packet until true is returned, so hold it for deletion until a subsequent call.

Definition at line 408 of file base.hh.

Referenced by handleTimingReqHit(), handleTimingReqMiss(), and gem5::Cache::recvTimingReq().

◆ ppDataUpdate

|

protected |

To probe when the contents of a block are updated.

Content updates include data fills, overwrites, and invalidations, which means that this probe partially overlaps with other probes.

Definition at line 378 of file base.hh.

Referenced by cmpAndSwap(), regProbePoints(), satisfyRequest(), and updateBlockData().

◆ ppFill

|

protected |

To probe when a cache fill occurs.

Definition at line 371 of file base.hh.

Referenced by recvTimingResp(), and regProbePoints().

◆ ppHit

|

protected |

To probe when a cache hit occurs.

Definition at line 365 of file base.hh.

Referenced by recvTimingReq(), and regProbePoints().

◆ ppMiss

|

protected |

To probe when a cache miss occurs.

Definition at line 368 of file base.hh.

Referenced by recvTimingReq(), and regProbePoints().

◆ prefetcher

|

protected |

Prefetcher.

Definition at line 362 of file base.hh.

Referenced by BaseCache(), getNextQueueEntry(), handleTimingReqMiss(), invalidateBlock(), nextQueueReadyTime(), recvTimingReq(), and recvTimingResp().

◆ replaceExpansions

|

protected |

when a data expansion of a compressed block happens it will not be able to co-allocate where it is at anymore.

If true, the replacement policy is called to chose a new location for the block. Otherwise, all co-allocated blocks are evicted.

Definition at line 957 of file base.hh.

Referenced by updateCompressionData().

◆ responseLatency

|

protected |

The latency of sending reponse to its upper level cache/core on a linefill.

The responseLatency parameter captures this latency.

Definition at line 923 of file base.hh.

Referenced by handleUncacheableWriteResp(), gem5::Cache::serviceMSHRTargets(), and gem5::NoncoherentCache::serviceMSHRTargets().

◆ sequentialAccess

|

protected |

Whether tags and data are accessed sequentially.

Definition at line 928 of file base.hh.

Referenced by calculateAccessLatency().

◆ stats

| gem5::BaseCache::CacheStats gem5::BaseCache::stats |

Referenced by clearBlocked(), getNextQueueEntry(), handleEvictions(), handleTimingReqMiss(), gem5::Cache::handleTimingReqMiss(), incHitCount(), incMissCount(), recvTimingResp(), gem5::Cache::serviceMSHRTargets(), gem5::NoncoherentCache::serviceMSHRTargets(), setBlocked(), updateCompressionData(), and writebackBlk().

◆ system

| System* gem5::BaseCache::system |

System we are currently operating in.

Definition at line 992 of file base.hh.

Referenced by gem5::Cache::Cache(), getNextQueueEntry(), handleTimingReqMiss(), incHitCount(), incMissCount(), gem5::NoncoherentCache::NoncoherentCache(), recvTimingResp(), gem5::BaseCache::CacheStats::regStats(), gem5::BaseCache::CacheCmdStats::regStatsFromParent(), gem5::Cache::serviceMSHRTargets(), and gem5::NoncoherentCache::serviceMSHRTargets().

◆ tags

|

protected |

Tag and data Storage.

Definition at line 353 of file base.hh.

Referenced by access(), gem5::Cache::access(), allocateBlock(), BaseCache(), functionalAccess(), getNextQueueEntry(), hasBeenPrefetched(), hasBeenPrefetched(), inCache(), invalidateBlock(), isDirty(), memInvalidate(), memWriteback(), gem5::Cache::recvAtomicSnoop(), recvTimingReq(), gem5::Cache::recvTimingReq(), recvTimingResp(), gem5::Cache::recvTimingSnoopReq(), regenerateBlkAddr(), satisfyRequest(), sendMSHRQueuePacket(), gem5::Cache::sendMSHRQueuePacket(), and updateCompressionData().

◆ tempBlock

|

protected |

Temporary cache block for occasional transitory use.

We use the tempBlock to fill when allocation fails (e.g., when there is an outstanding request that accesses the victim block) or when we want to avoid allocation (e.g., exclusive caches)

Definition at line 402 of file base.hh.

Referenced by handleFill(), invalidateBlock(), recvAtomic(), recvTimingResp(), regenerateBlkAddr(), updateCompressionData(), and ~BaseCache().

◆ tempBlockWriteback

|

protected |

Writebacks from the tempBlock, resulting on the response path in atomic mode, must happen after the call to recvAtomic has finished (for the right ordering of the packets).

We therefore need to hold on to the packets, and have a method and an event to send them.

Definition at line 690 of file base.hh.

Referenced by BaseCache(), recvAtomic(), and writebackTempBlockAtomic().

◆ writeAllocator

|

protected |

The writeAllocator drive optimizations for streaming writes.

It first determines whether a WriteReq MSHR should be delayed, thus ensuring that we wait longer in cases when we are write coalescing and allowing all the bytes of the line to be written before the MSHR packet is sent downstream. This works in unison with the tracking in the MSHR to check if the entire line is written. The write mode also affects the behaviour on filling any whole-line writes. Normally the cache allocates the line when receiving the InvalidateResp, but after seeing enough consecutive lines we switch to using the tempBlock, and thus end up not allocating the line, and instead turning the whole-line write into a writeback straight away.

Definition at line 394 of file base.hh.

Referenced by BaseCache(), coalesce(), gem5::Cache::handleAtomicReqMiss(), handleTimingReqMiss(), recvTimingResp(), and sendMSHRQueuePacket().

◆ writebackClean

|

protected |

Determine if clean lines should be written back or not.

In cases where a downstream cache is mostly inclusive we likely want it to act as a victim cache also for lines that have not been modified. Hence, we cannot simply drop the line (or send a clean evict), but rather need to send the actual data.

Definition at line 681 of file base.hh.

Referenced by BaseCache(), gem5::Cache::cleanEvictBlk(), gem5::Cache::doWritebacks(), gem5::Cache::evictBlock(), gem5::NoncoherentCache::evictBlock(), and writebackBlk().

◆ writebackTempBlockAtomicEvent

|

protected |

An event to writeback the tempBlock after recvAtomic finishes.

To avoid other calls to recvAtomic getting in between, we create this event with a higher priority.

Definition at line 709 of file base.hh.

Referenced by BaseCache(), and recvAtomic().

◆ writeBuffer

|

protected |

Write/writeback buffer.

Definition at line 350 of file base.hh.

Referenced by access(), allocateWriteBuffer(), BaseCache(), functionalAccess(), getNextQueueEntry(), handleFill(), markInService(), nextQueueReadyTime(), and gem5::Cache::recvTimingSnoopReq().