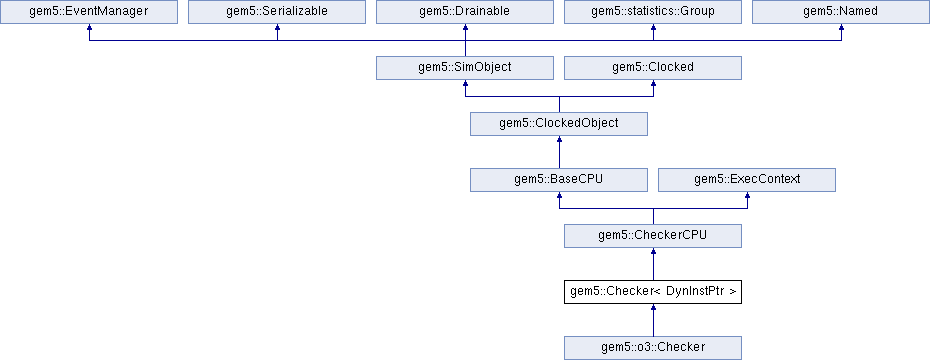

Templated Checker class. More...

#include <cpu.hh>

Public Member Functions | |

| Checker (const Params &p) | |

| void | switchOut () |

| Prepare for another CPU to take over execution. | |

| void | takeOverFrom (BaseCPU *oldCPU) |

| Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in. | |

| void | advancePC (const Fault &fault) |

| void | verify (const DynInstPtr &inst) |

| void | validateInst (const DynInstPtr &inst) |

| void | validateExecution (const DynInstPtr &inst) |

| void | validateState () |

| void | copyResult (const DynInstPtr &inst, const InstResult &mismatch_val, int start_idx) |

| void | handlePendingInt () |

| Public Member Functions inherited from gem5::CheckerCPU | |

| void | init () override |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| PARAMS (CheckerCPU) | |

| CheckerCPU (const Params &p) | |

| virtual | ~CheckerCPU () |

| void | setSystem (System *system) |

| void | setIcachePort (RequestPort *icache_port) |

| void | setDcachePort (RequestPort *dcache_port) |

| Port & | getDataPort () override |

| Purely virtual method that returns a reference to the data port. | |

| Port & | getInstPort () override |

| Purely virtual method that returns a reference to the instruction port. | |

| BaseMMU * | getMMUPtr () |

| virtual Counter | totalInsts () const override |

| virtual Counter | totalOps () const override |

| void | serialize (CheckpointOut &cp) const override |

| Serialize this object to the given output stream. | |

| void | unserialize (CheckpointIn &cp) override |

| Reconstruct the state of this object from a checkpoint. | |

| RegVal | getRegOperand (const StaticInst *si, int idx) override |

| void | getRegOperand (const StaticInst *si, int idx, void *val) override |

| void * | getWritableRegOperand (const StaticInst *si, int idx) override |

| void | setRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setRegOperand (const StaticInst *si, int idx, const void *val) override |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| Fault | initiateMemMgmtCmd (Request::Flags flags) override |

| Initiate a memory management command with no valid address. | |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| const PCStateBase & | pcState () const override |

| void | pcState (const PCStateBase &val) override |

| RegVal | readMiscRegNoEffect (int misc_reg) const |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a miscellaneous register, handling any architectural side effects due to reading that register. | |

| void | setMiscRegNoEffect (int misc_reg, RegVal val) |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a miscellaneous register, handling any architectural side effects due to writing that register. | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | recordPCChange (const PCStateBase &val) |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| RequestPtr | genMemFragmentRequest (Addr frag_addr, int size, Request::Flags flags, const std::vector< bool > &byte_enable, int &frag_size, int &size_left) const |

| Helper function used to generate the request for a single fragment of a memory access. | |

| Fault | readMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable) override |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable) override |

| Fault | amoMem (Addr addr, uint8_t *data, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. | |

| void | wakeup (ThreadID tid) override |

| void | handleError () |

| bool | checkFlags (const RequestPtr &unverified_req, Addr vAddr, Addr pAddr, int flags) |

| Checks if the flags set by the Checker and Checkee match. | |

| void | dumpAndExit () |

| ThreadContext * | tcBase () const override |

| Returns a pointer to the ThreadContext. | |

| SimpleThread * | threadBase () |

| Public Member Functions inherited from gem5::BaseCPU | |

| int | cpuId () const |

| Reads this CPU's ID. | |

| uint32_t | socketId () const |

| Reads this CPU's Socket ID. | |

| RequestorID | dataRequestorId () const |

| Reads this CPU's unique data requestor ID. | |

| RequestorID | instRequestorId () const |

| Reads this CPU's unique instruction requestor ID. | |

| Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) override |

| Get a port on this CPU. | |

| uint32_t | taskId () const |

| Get cpu task id. | |

| void | taskId (uint32_t id) |

| Set cpu task id. | |

| uint32_t | getPid () const |

| void | setPid (uint32_t pid) |

| void | workItemBegin () |

| void | workItemEnd () |

| Tick | instCount () |

| BaseInterrupts * | getInterruptController (ThreadID tid) |

| void | postInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupt (ThreadID tid, int int_num, int index) |

| void | clearInterrupts (ThreadID tid) |

| bool | checkInterrupts (ThreadID tid) const |

| trace::InstTracer * | getTracer () |

| Provide access to the tracer pointer. | |

| virtual void | activateContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now active. | |

| virtual void | suspendContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now suspended. | |

| virtual void | haltContext (ThreadID thread_num) |

| Notify the CPU that the indicated context is now halted. | |

| int | findContext (ThreadContext *tc) |

| Given a Thread Context pointer return the thread num. | |

| virtual ThreadContext * | getContext (int tn) |

| Given a thread num get tho thread context for it. | |

| unsigned | numContexts () |

| Get the number of thread contexts available. | |

| ThreadID | contextToThread (ContextID cid) |

| Convert ContextID to threadID. | |

| PARAMS (BaseCPU) | |

| BaseCPU (const Params ¶ms, bool is_checker=false) | |

| virtual | ~BaseCPU () |

| void | startup () override |

| startup() is the final initialization call before simulation. | |

| void | regStats () override |

| Callback to set stat parameters. | |

| void | regProbePoints () override |

| Register probe points for this object. | |

| void | registerThreadContexts () |

| void | deschedulePowerGatingEvent () |

| void | schedulePowerGatingEvent () |

| virtual void | setReset (bool state) |

| Set the reset of the CPU to be either asserted or deasserted. | |

| void | flushTLBs () |

| Flush all TLBs in the CPU. | |

| bool | switchedOut () const |

| Determine if the CPU is switched out. | |

| virtual void | verifyMemoryMode () const |

| Verify that the system is in a memory mode supported by the CPU. | |

| Addr | cacheLineSize () const |

| Get the cache line size of the system. | |

| virtual void | serializeThread (CheckpointOut &cp, ThreadID tid) const |

| Serialize a single thread. | |

| virtual void | unserializeThread (CheckpointIn &cp, ThreadID tid) |

| Unserialize one thread. | |

| void | scheduleInstStop (ThreadID tid, Counter insts, std::string cause) |

| Schedule an event that exits the simulation loops after a predefined number of instructions. | |

| void | scheduleSimpointsInstStop (std::vector< Counter > inst_starts) |

| Schedule simpoint events using the scheduleInstStop function. | |

| void | scheduleInstStopAnyThread (Counter max_insts) |

| Schedule an exit event when any threads in the core reach the max_insts instructions using the scheduleInstStop function. | |

| uint64_t | getCurrentInstCount (ThreadID tid) |

| Get the number of instructions executed by the specified thread on this CPU. | |

| void | traceFunctions (Addr pc) |

| void | armMonitor (ThreadID tid, Addr address) |

| bool | mwait (ThreadID tid, PacketPtr pkt) |

| void | mwaitAtomic (ThreadID tid, ThreadContext *tc, BaseMMU *mmu) |

| AddressMonitor * | getCpuAddrMonitor (ThreadID tid) |

| virtual void | htmSendAbortSignal (ThreadID tid, uint64_t htm_uid, HtmFailureFaultCause cause) |

| This function is used to instruct the memory subsystem that a transaction should be aborted and the speculative state should be thrown away. | |

| virtual void | probeInstCommit (const StaticInstPtr &inst, Addr pc) |

| Helper method to trigger PMU probes for a committed instruction. | |

| Public Member Functions inherited from gem5::ClockedObject | |

| ClockedObject (const ClockedObjectParams &p) | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| virtual void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

| Public Member Functions inherited from gem5::Clocked | |

| void | updateClockPeriod () |

| Update the tick to the current tick. | |

| Tick | clockEdge (Cycles cycles=Cycles(0)) const |

| Determine the tick when a cycle begins, by default the current one, but the argument also enables the caller to determine a future cycle. | |

| Cycles | curCycle () const |

| Determine the current cycle, corresponding to a tick aligned to a clock edge. | |

| Tick | nextCycle () const |

| Based on the clock of the object, determine the start tick of the first cycle that is at least one cycle in the future. | |

| uint64_t | frequency () const |

| Tick | clockPeriod () const |

| double | voltage () const |

| Cycles | ticksToCycles (Tick t) const |

| Tick | cyclesToTicks (Cycles c) const |

| Public Member Functions inherited from gem5::ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Perform an atomic memory read operation. | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Initiate a timing memory read operation. | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable)=0 |

| For atomic-mode contexts, perform an atomic memory write operation. | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) | |

Private Types | |

| typedef std::list< DynInstPtr >::iterator | InstListIt |

Private Member Functions | |

| void | handleError (const DynInstPtr &inst) |

| void | dumpAndExit (const DynInstPtr &inst) |

| void | dumpInsts () |

Private Attributes | |

| bool | updateThisCycle |

| DynInstPtr | unverifiedInst |

| std::list< DynInstPtr > | instList |

Additional Inherited Members | |

| Public Types inherited from gem5::ClockedObject | |

| using | Params = ClockedObjectParams |

| Parameters of ClockedObject. | |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

| Static Public Member Functions inherited from gem5::BaseCPU | |

| static int | numSimulatedCPUs () |

| static Counter | totalNumSimulatedInsts () |

| static Counter | totalNumSimulatedOps () |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

| Public Attributes inherited from gem5::CheckerCPU | |

| SimpleThread * | thread |

| Counter | numLoad |

| Counter | startNumLoad |

| InstResult | unverifiedResult |

| RequestPtr | unverifiedReq |

| uint8_t * | unverifiedMemData |

| bool | changedPC |

| bool | willChangePC |

| std::unique_ptr< PCStateBase > | newPCState |

| bool | exitOnError |

| bool | updateOnError |

| bool | warnOnlyOnLoadError |

| InstSeqNum | youngestSN |

| Public Attributes inherited from gem5::BaseCPU | |

| ThreadID | numThreads |

| Number of threads we're actually simulating (<= SMT_MAX_THREADS). | |

| System * | system |

| gem5::BaseCPU::BaseCPUStats | baseStats |

| Cycles | syscallRetryLatency |

| std::vector< std::unique_ptr< FetchCPUStats > > | fetchStats |

| std::vector< std::unique_ptr< ExecuteCPUStats > > | executeStats |

| std::vector< std::unique_ptr< CommitCPUStats > > | commitStats |

| Public Attributes inherited from gem5::ClockedObject | |

| PowerState * | powerState |

| Static Public Attributes inherited from gem5::BaseCPU | |

| static const uint32_t | invldPid = std::numeric_limits<uint32_t>::max() |

| Invalid or unknown Pid. | |

| Protected Types inherited from gem5::BaseCPU | |

| enum | CPUState { CPU_STATE_ON , CPU_STATE_SLEEP , CPU_STATE_WAKEUP } |

| Protected Member Functions inherited from gem5::BaseCPU | |

| void | updateCycleCounters (CPUState state) |

| base method keeping track of cycle progression | |

| void | enterPwrGating () |

| probing::PMUUPtr | pmuProbePoint (const char *name) |

| Helper method to instantiate probe points belonging to this object. | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

| Protected Member Functions inherited from gem5::Clocked | |

| Clocked (ClockDomain &clk_domain) | |

| Create a clocked object and set the clock domain based on the parameters. | |

| Clocked (Clocked &)=delete | |

| Clocked & | operator= (Clocked &)=delete |

| virtual | ~Clocked () |

| Virtual destructor due to inheritance. | |

| void | resetClock () const |

| Reset the object's clock using the current global tick value. | |

| virtual void | clockPeriodUpdated () |

| A hook subclasses can implement so they can do any extra work that's needed when the clock rate is changed. | |

| Protected Attributes inherited from gem5::CheckerCPU | |

| RequestorID | requestorId |

| id attached to all issued requests | |

| std::vector< Process * > | workload |

| System * | systemPtr |

| RequestPort * | icachePort |

| RequestPort * | dcachePort |

| ThreadContext * | tc |

| BaseMMU * | mmu |

| std::queue< InstResult > | result |

| StaticInstPtr | curStaticInst |

| StaticInstPtr | curMacroStaticInst |

| Counter | numInst |

| Counter | startNumInst |

| std::queue< int > | miscRegIdxs |

| Protected Attributes inherited from gem5::BaseCPU | |

| Tick | instCnt |

| Instruction count used for SPARC misc register. | |

| int | _cpuId |

| const uint32_t | _socketId |

| Each cpu will have a socket ID that corresponds to its physical location in the system. | |

| RequestorID | _instRequestorId |

| instruction side request id that must be placed in all requests | |

| RequestorID | _dataRequestorId |

| data side request id that must be placed in all requests | |

| uint32_t | _taskId |

| An intrenal representation of a task identifier within gem5. | |

| uint32_t | _pid |

| The current OS process ID that is executing on this processor. | |

| bool | _switchedOut |

| Is the CPU switched out or active? | |

| const Addr | _cacheLineSize |

| Cache the cache line size that we get from the system. | |

| SignalSinkPort< bool > | modelResetPort |

| std::vector< BaseInterrupts * > | interrupts |

| std::vector< ThreadContext * > | threadContexts |

| std::vector< std::unique_ptr< IntSourcePin< BaseCPU > > > | cpuIdlePins |

| trace::InstTracer * | tracer |

| Cycles | previousCycle |

| CPUState | previousState |

| const Cycles | pwrGatingLatency |

| const bool | powerGatingOnIdle |

| EventFunctionWrapper | enterPwrGatingEvent |

| probing::PMUUPtr | ppRetiredInsts |

| Instruction commit probe point. | |

| probing::PMUUPtr | ppRetiredInstsPC |

| probing::PMUUPtr | ppRetiredLoads |

| Retired load instructions. | |

| probing::PMUUPtr | ppRetiredStores |

| Retired store instructions. | |

| probing::PMUUPtr | ppRetiredBranches |

| Retired branches (any type) | |

| probing::PMUUPtr | ppAllCycles |

| CPU cycle counter even if any thread Context is suspended. | |

| probing::PMUUPtr | ppActiveCycles |

| CPU cycle counter, only counts if any thread contexts is active. | |

| ProbePointArg< bool > * | ppSleeping |

| ProbePoint that signals transitions of threadContexts sets. | |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

| Static Protected Attributes inherited from gem5::BaseCPU | |

| static std::unique_ptr< GlobalStats > | globalStats |

| Pointer to the global stat structure. | |

Detailed Description

class gem5::Checker< DynInstPtr >

Templated Checker class.

This Checker class is templated on the DynInstPtr of the instruction type that will be verified. Proper template instantiations of the Checker must be placed at the bottom of checker/cpu.cc.

Member Typedef Documentation

◆ InstListIt

|

private |

Constructor & Destructor Documentation

◆ Checker()

|

inline |

Definition at line 450 of file cpu.hh.

References gem5::CheckerCPU::CheckerCPU(), gem5::MipsISA::p, unverifiedInst, and updateThisCycle.

Referenced by advancePC(), handlePendingInt(), and verify().

Member Function Documentation

◆ advancePC()

| void gem5::Checker< DynInstPtr >::advancePC | ( | const Fault & | fault | ) |

Definition at line 66 of file cpu_impl.hh.

References Checker(), gem5::CheckerCPU::curMacroStaticInst, gem5::CheckerCPU::curStaticInst, DPRINTF, gem5::NoFault, gem5::nullStaticInstPtr, gem5::CheckerCPU::tc, and gem5::CheckerCPU::thread.

Referenced by validateState(), and verify().

◆ copyResult()

| void gem5::Checker< DynInstPtr >::copyResult | ( | const DynInstPtr & | inst, |

| const InstResult & | mismatch_val, | ||

| int | start_idx ) |

Definition at line 570 of file cpu_impl.hh.

References gem5::InstResult::asBlob(), gem5::InstResult::asRegVal(), gem5::RegId::classValue(), gem5::ArmISA::i, gem5::RegId::index(), gem5::InvalidRegClass, gem5::InstResult::isBlob(), gem5::MiscRegClass, and gem5::CheckerCPU::thread.

◆ dumpAndExit()

|

private |

Definition at line 606 of file cpu_impl.hh.

References gem5::cprintf(), and gem5::CheckerCPU::dumpAndExit().

◆ dumpInsts()

|

private |

Definition at line 621 of file cpu_impl.hh.

References gem5::cprintf(), and instList.

◆ handleError()

|

inlineprivate |

Definition at line 471 of file cpu.hh.

References gem5::CheckerCPU::dumpAndExit(), gem5::CheckerCPU::exitOnError, gem5::CheckerCPU::updateOnError, and updateThisCycle.

Referenced by validateInst(), and verify().

◆ handlePendingInt()

| void gem5::Checker< DynInstPtr >::handlePendingInt | ( | ) |

Definition at line 85 of file cpu_impl.hh.

References Checker(), gem5::CheckerCPU::curMacroStaticInst, gem5::CheckerCPU::curStaticInst, gem5::curTick(), DPRINTF, instList, gem5::nullStaticInstPtr, panic, gem5::CheckerCPU::thread, and verify().

◆ switchOut()

|

virtual |

Prepare for another CPU to take over execution.

When this method exits, all internal state should have been flushed. After the method returns, the simulator calls takeOverFrom() on the new CPU with this CPU as its parameter.

Reimplemented from gem5::BaseCPU.

Definition at line 431 of file cpu_impl.hh.

References instList.

◆ takeOverFrom()

|

virtual |

Load the state of a CPU from the previous CPU object, invoked on all new CPUs that are about to be switched in.

A CPU model implementing this method is expected to initialize its state from the old CPU and connect its memory (unless they are already connected) to the memories connected to the old CPU.

- Parameters

-

cpu CPU to initialize read state from.

Reimplemented from gem5::BaseCPU.

Definition at line 437 of file cpu_impl.hh.

◆ validateExecution()

| void gem5::Checker< DynInstPtr >::validateExecution | ( | const DynInstPtr & | inst | ) |

Definition at line 462 of file cpu_impl.hh.

Referenced by verify().

◆ validateInst()

| void gem5::Checker< DynInstPtr >::validateInst | ( | const DynInstPtr & | inst | ) |

Definition at line 441 of file cpu_impl.hh.

References gem5::CheckerCPU::changedPC, gem5::curTick(), handleError(), gem5::CheckerCPU::thread, and warn.

Referenced by verify().

◆ validateState()

| void gem5::Checker< DynInstPtr >::validateState | ( | ) |

Definition at line 544 of file cpu_impl.hh.

References advancePC(), gem5::CheckerCPU::curStaticInst, gem5::curTick(), gem5::NoFault, panic, gem5::CheckerCPU::thread, unverifiedInst, and updateThisCycle.

Referenced by verify().

◆ verify()

| void gem5::Checker< DynInstPtr >::verify | ( | const DynInstPtr & | inst | ) |

Definition at line 119 of file cpu_impl.hh.

References advancePC(), gem5::BaseCPU::baseStats, gem5::CheckerCPU::changedPC, Checker(), gem5::X86ISA::count, gem5::CheckerCPU::curMacroStaticInst, gem5::CheckerCPU::curStaticInst, gem5::curTick(), gem5::Packet::dataStatic(), decoder, DPRINTF, gem5::trace::InstRecord::dump(), gem5::BaseMMU::Execute, gem5::StaticInst::fetchMicroop(), gem5::FullSystem, handleError(), gem5::CheckerCPU::handleError(), gem5::CheckerCPU::icachePort, gem5::Request::INST_FETCH, instList, gem5::StaticInst::isMacroop(), gem5::isRomMicroPC(), gem5::CheckerCPU::mmu, gem5::CheckerCPU::newPCState, gem5::NoFault, gem5::nullStaticInstPtr, gem5::CheckerCPU::numInst, gem5::CheckerCPU::numLoad, panic, gem5::CheckerCPU::pcState(), gem5::MemCmd::ReadReq, gem5::CheckerCPU::requestorId, gem5::CheckerCPU::result, gem5::ArmISA::set, gem5::CheckerCPU::tc, gem5::CheckerCPU::thread, gem5::BaseCPU::tracer, unverifiedInst, gem5::CheckerCPU::unverifiedMemData, gem5::CheckerCPU::unverifiedReq, validateExecution(), validateInst(), validateState(), warn, gem5::CheckerCPU::willChangePC, and gem5::CheckerCPU::youngestSN.

Referenced by handlePendingInt().

Member Data Documentation

◆ instList

|

private |

Definition at line 486 of file cpu.hh.

Referenced by dumpInsts(), handlePendingInt(), switchOut(), and verify().

◆ unverifiedInst

|

private |

Definition at line 484 of file cpu.hh.

Referenced by Checker(), validateState(), and verify().

◆ updateThisCycle

|

private |

Definition at line 482 of file cpu.hh.

Referenced by Checker(), handleError(), and validateState().

The documentation for this class was generated from the following files:

- cpu/checker/cpu.hh

- cpu/checker/cpu_impl.hh

Generated on Sat Oct 18 2025 08:06:50 for gem5 by doxygen 1.14.0