#include <tlb.hh>

Classes | |

| struct | TlbStats |

Public Types | |

| typedef X86TLBParams | Params |

| Public Types inherited from gem5::SimObject | |

| typedef SimObjectParams | Params |

Public Member Functions | |

| TLB (const Params &p) | |

| void | takeOverFrom (BaseTLB *otlb) override |

| Take over from an old tlb context. | |

| TlbEntry * | lookup (Addr va, bool update_lru=true) |

| void | setConfigAddress (uint32_t addr) |

| Addr | concAddrPcid (Addr vpn, uint64_t pcid) |

| Walker * | getWalker () |

| void | flushAll () override |

| Remove all entries from the TLB. | |

| void | flushNonGlobal () |

| void | demapPage (Addr va, uint64_t asn) override |

| void | evictLRU () |

| uint64_t | nextSeq () |

| Fault | translateAtomic (const RequestPtr &req, ThreadContext *tc, BaseMMU::Mode mode) override |

| Fault | translateFunctional (const RequestPtr &req, ThreadContext *tc, BaseMMU::Mode mode) override |

| void | translateTiming (const RequestPtr &req, ThreadContext *tc, BaseMMU::Translation *translation, BaseMMU::Mode mode) override |

| Fault | finalizePhysical (const RequestPtr &req, ThreadContext *tc, BaseMMU::Mode mode) const override |

| Do post-translation physical address finalization. | |

| TlbEntry * | insert (Addr vpn, const TlbEntry &entry, uint64_t pcid) |

| void | serialize (CheckpointOut &cp) const override |

| Serialize an object. | |

| void | unserialize (CheckpointIn &cp) override |

| Unserialize an object. | |

| Port * | getTableWalkerPort () override |

| Get the table walker port. | |

| Public Member Functions inherited from gem5::BaseTLB | |

| void | memInvalidate () |

| Invalidate the contents of memory buffers. | |

| TypeTLB | type () const |

| BaseTLB * | nextLevel () const |

| Public Member Functions inherited from gem5::SimObject | |

| const Params & | params () const |

| SimObject (const Params &p) | |

| virtual | ~SimObject () |

| virtual void | init () |

| init() is called after all C++ SimObjects have been created and all ports are connected. | |

| virtual void | loadState (CheckpointIn &cp) |

| loadState() is called on each SimObject when restoring from a checkpoint. | |

| virtual void | initState () |

| initState() is called on each SimObject when not restoring from a checkpoint. | |

| virtual void | regProbePoints () |

| Register probe points for this object. | |

| virtual void | regProbeListeners () |

| Register probe listeners for this object. | |

| ProbeManager * | getProbeManager () |

| Get the probe manager for this object. | |

| virtual Port & | getPort (const std::string &if_name, PortID idx=InvalidPortID) |

| Get a port with a given name and index. | |

| virtual void | startup () |

| startup() is the final initialization call before simulation. | |

| DrainState | drain () override |

| Provide a default implementation of the drain interface for objects that don't need draining. | |

| virtual void | memWriteback () |

| Write back dirty buffers to memory using functional writes. | |

| Public Member Functions inherited from gem5::EventManager | |

| EventQueue * | eventQueue () const |

| void | schedule (Event &event, Tick when) |

| void | deschedule (Event &event) |

| void | reschedule (Event &event, Tick when, bool always=false) |

| void | schedule (Event *event, Tick when) |

| void | deschedule (Event *event) |

| void | reschedule (Event *event, Tick when, bool always=false) |

| void | wakeupEventQueue (Tick when=(Tick) -1) |

| This function is not needed by the usual gem5 event loop but may be necessary in derived EventQueues which host gem5 on other schedulers. | |

| void | setCurTick (Tick newVal) |

| EventManager (EventManager &em) | |

| Event manger manages events in the event queue. | |

| EventManager (EventManager *em) | |

| EventManager (EventQueue *eq) | |

| Public Member Functions inherited from gem5::Serializable | |

| Serializable () | |

| virtual | ~Serializable () |

| void | serializeSection (CheckpointOut &cp, const char *name) const |

| Serialize an object into a new section. | |

| void | serializeSection (CheckpointOut &cp, const std::string &name) const |

| void | unserializeSection (CheckpointIn &cp, const char *name) |

| Unserialize an a child object. | |

| void | unserializeSection (CheckpointIn &cp, const std::string &name) |

| Public Member Functions inherited from gem5::Drainable | |

| DrainState | drainState () const |

| Return the current drain state of an object. | |

| virtual void | notifyFork () |

| Notify a child process of a fork. | |

| Public Member Functions inherited from gem5::statistics::Group | |

| Group (Group *parent, const char *name=nullptr) | |

| Construct a new statistics group. | |

| virtual | ~Group () |

| virtual void | regStats () |

| Callback to set stat parameters. | |

| virtual void | resetStats () |

| Callback to reset stats. | |

| virtual void | preDumpStats () |

| Callback before stats are dumped. | |

| void | addStat (statistics::Info *info) |

| Register a stat with this group. | |

| const std::map< std::string, Group * > & | getStatGroups () const |

| Get all child groups associated with this object. | |

| const std::vector< Info * > & | getStats () const |

| Get all stats associated with this object. | |

| void | addStatGroup (const char *name, Group *block) |

| Add a stat block as a child of this block. | |

| const Info * | resolveStat (std::string name) const |

| Resolve a stat by its name within this group. | |

| void | mergeStatGroup (Group *block) |

| Merge the contents (stats & children) of a block to this block. | |

| Group ()=delete | |

| Group (const Group &)=delete | |

| Group & | operator= (const Group &)=delete |

| Public Member Functions inherited from gem5::Named | |

| Named (std::string_view name_) | |

| virtual | ~Named ()=default |

| virtual std::string | name () const |

Protected Types | |

| typedef std::list< TlbEntry * > | EntryList |

Protected Member Functions | |

| EntryList::iterator | lookupIt (Addr va, bool update_lru=true) |

| Fault | translateInt (bool read, RequestPtr req, ThreadContext *tc) |

| Fault | translate (const RequestPtr &req, ThreadContext *tc, BaseMMU::Translation *translation, BaseMMU::Mode mode, bool &delayedResponse, bool timing) |

| Protected Member Functions inherited from gem5::BaseTLB | |

| BaseTLB (const BaseTLBParams &p) | |

| Protected Member Functions inherited from gem5::Drainable | |

| Drainable () | |

| virtual | ~Drainable () |

| virtual void | drainResume () |

| Resume execution after a successful drain. | |

| void | signalDrainDone () const |

| Signal that an object is drained. | |

Protected Attributes | |

| uint32_t | configAddress |

| Walker * | walker |

| uint32_t | size |

| std::vector< TlbEntry > | tlb |

| EntryList | freeList |

| TlbEntryTrie | trie |

| uint64_t | lruSeq |

| AddrRange | m5opRange |

| gem5::X86ISA::TLB::TlbStats | stats |

| Protected Attributes inherited from gem5::BaseTLB | |

| TypeTLB | _type |

| BaseTLB * | _nextLevel |

| Protected Attributes inherited from gem5::SimObject | |

| const SimObjectParams & | _params |

| Cached copy of the object parameters. | |

| Protected Attributes inherited from gem5::EventManager | |

| EventQueue * | eventq |

| A pointer to this object's event queue. | |

Friends | |

| class | Walker |

Additional Inherited Members | |

| Static Public Member Functions inherited from gem5::SimObject | |

| static void | serializeAll (const std::string &cpt_dir) |

| Create a checkpoint by serializing all SimObjects in the system. | |

| static SimObject * | find (const char *name) |

| Find the SimObject with the given name and return a pointer to it. | |

| static void | setSimObjectResolver (SimObjectResolver *resolver) |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| static SimObjectResolver * | getSimObjectResolver () |

| There is a single object name resolver, and it is only set when simulation is restoring from checkpoints. | |

| Static Public Member Functions inherited from gem5::Serializable | |

| static const std::string & | currentSection () |

| Gets the fully-qualified name of the active section. | |

| static void | generateCheckpointOut (const std::string &cpt_dir, std::ofstream &outstream) |

| Generate a checkpoint file so that the serialization can be routed to it. | |

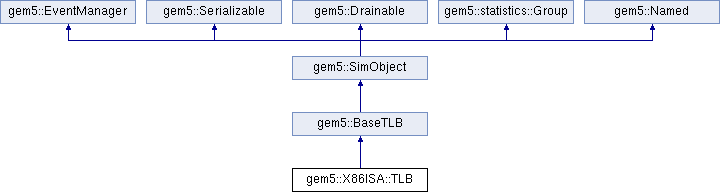

Detailed Description

Member Typedef Documentation

◆ EntryList

|

protected |

◆ Params

| typedef X86TLBParams gem5::X86ISA::TLB::Params |

Constructor & Destructor Documentation

◆ TLB()

| gem5::X86ISA::TLB::TLB | ( | const Params & | p | ) |

Definition at line 65 of file tlb.cc.

References gem5::BaseTLB::BaseTLB(), configAddress, fatal, freeList, lruSeq, m5opRange, gem5::X86ISA::p, size, stats, gem5::X86ISA::system, tlb, walker, and gem5::X86ISA::x.

Referenced by flushAll(), flushNonGlobal(), translate(), and translateInt().

Member Function Documentation

◆ concAddrPcid()

Definition at line 80 of file tlb.hh.

References gem5::X86ISA::pcid.

Referenced by insert(), and translate().

◆ demapPage()

|

overridevirtual |

Implements gem5::BaseTLB.

Definition at line 177 of file tlb.cc.

References freeList, trie, gem5::X86ISA::TlbEntry::trieHandle, and gem5::ArmISA::va.

◆ evictLRU()

| void gem5::X86ISA::TLB::evictLRU | ( | ) |

Definition at line 101 of file tlb.cc.

References evictLRU(), gem5::ArmISA::i, lruSeq, size, and tlb.

Referenced by evictLRU(), and insert().

◆ finalizePhysical()

|

overridevirtual |

Do post-translation physical address finalization.

Some addresses, for example requests going to the APIC, need post-translation updates. Such physical addresses are remapped into a "magic" part of the physical address space by this method.

- Parameters

-

req Request to updated in-place. tc Thread context that created the request. mode Request type (read/write/execute).

- Returns

- A fault on failure, NoFault otherwise.

Implements gem5::BaseTLB.

Definition at line 273 of file tlb.cc.

References gem5::X86ISA::misc_reg::ApicBase, gem5::AddrRange::contains(), gem5::ThreadContext::contextId(), gem5::pseudo_inst::decodeAddrOffset(), gem5::FullSystem, m5opRange, gem5::X86ISA::mode, gem5::NoFault, gem5::X86ISA::PageBytes, gem5::pseudo_inst::pseudoInst(), gem5::BaseMMU::Read, gem5::ThreadContext::readMiscRegNoEffect(), gem5::Packet::setLE(), gem5::AddrRange::start(), gem5::Request::STRICT_ORDER, gem5::Request::UNCACHEABLE, and gem5::X86ISA::x86LocalAPICAddress().

Referenced by translate().

◆ flushAll()

|

overridevirtual |

◆ flushNonGlobal()

| void gem5::X86ISA::TLB::flushNonGlobal | ( | ) |

◆ getTableWalkerPort()

|

overridevirtual |

Get the table walker port.

This is used for migrating port connections during a CPU takeOverFrom() call. For architectures that do not have a table walker, NULL is returned, hence the use of a pointer rather than a reference. For X86 this method will always return a valid port pointer.

- Returns

- A pointer to the walker port

Reimplemented from gem5::BaseTLB.

Definition at line 630 of file tlb.cc.

References walker.

◆ getWalker()

| Walker * gem5::X86ISA::TLB::getWalker | ( | ) |

Definition at line 95 of file tlb.cc.

References getWalker(), and walker.

Referenced by getWalker().

◆ insert()

Definition at line 100 of file tlb.cc.

References concAddrPcid(), evictLRU(), freeList, gem5::FullSystem, gem5::X86ISA::TlbEntry::logBytes, gem5::X86ISA::TlbEntry::lruSeq, gem5::Trie< Addr, TlbEntry >::MaxBits, nextSeq(), gem5::X86ISA::pcid, trie, gem5::X86ISA::TlbEntry::trieHandle, and gem5::X86ISA::TlbEntry::vaddr.

Referenced by translate().

◆ lookup()

Definition at line 136 of file tlb.cc.

References gem5::X86ISA::TlbEntry::lruSeq, nextSeq(), trie, and gem5::ArmISA::va.

Referenced by translate().

◆ lookupIt()

|

protected |

References gem5::ArmISA::va.

◆ nextSeq()

|

inline |

◆ serialize()

|

overridevirtual |

Serialize an object.

Output an object's state into the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::SimObject.

Definition at line 195 of file tlb.cc.

References gem5::csprintf(), gem5::ArmISA::i, serialize(), SERIALIZE_SCALAR, and size.

Referenced by serialize().

◆ setConfigAddress()

| void gem5::X86ISA::TLB::setConfigAddress | ( | uint32_t | addr | ) |

Definition at line 158 of file tlb.cc.

References gem5::X86ISA::addr, and configAddress.

◆ takeOverFrom()

|

inlineoverridevirtual |

Take over from an old tlb context.

Implements gem5::BaseTLB.

Definition at line 74 of file tlb.hh.

References gem5::BaseTLB::BaseTLB().

◆ translate()

|

protected |

Definition at line 322 of file tlb.cc.

References gem5::X86ISA::AddrSizeFlagMask, gem5::X86ISA::AddrSizeFlagShift, gem5::ArmISA::attr, gem5::X86ISA::base, concAddrPcid(), gem5::X86ISA::CPL0FlagBit, gem5::X86ISA::misc_reg::Cr0, gem5::X86ISA::misc_reg::Cr3, gem5::X86ISA::misc_reg::Cr4, gem5::X86ISA::segment_idx::Cs, DPRINTF, gem5::X86ISA::segment_idx::Es, gem5::BaseMMU::Execute, gem5::X86ISA::expandDown, finalizePhysical(), gem5::EmulationPageTable::Entry::flags, gem5::FullSystem, gem5::ThreadContext::getProcessPtr(), gem5::X86ISA::segment_idx::Hs, insert(), gem5::PCStateBase::instAddr(), gem5::X86ISA::limit, gem5::X86ISA::TlbEntry::logBytes, lookup(), gem5::X86ISA::misc_reg::M5Reg, gem5::X86ISA::mask, gem5::X86ISA::mode, gem5::X86ISA::segment_idx::Ms, gem5::NoFault, gem5::X86ISA::offset, gem5::X86ISA::p, gem5::EmulationPageTable::Entry::paddr, gem5::X86ISA::TlbEntry::paddr, gem5::X86ISA::PageShift, gem5::X86ISA::pcid, gem5::ThreadContext::pcState(), gem5::BaseMMU::Read, gem5::Request::READ_MODIFY_WRITE, gem5::ThreadContext::readMiscRegNoEffect(), gem5::EmulationPageTable::ReadOnly, gem5::X86ISA::seg, gem5::X86ISA::misc_reg::segAttr(), gem5::X86ISA::misc_reg::segBase(), gem5::X86ISA::misc_reg::segLimit(), gem5::X86ISA::SegmentFlagMask, gem5::X86ISA::SixtyFourBitMode, stats, gem5::Request::STRICT_ORDER, TLB(), translateInt(), gem5::Request::UNCACHEABLE, gem5::EmulationPageTable::Uncacheable, gem5::X86ISA::TlbEntry::uncacheable, gem5::X86ISA::TlbEntry::user, gem5::MipsISA::vaddr, walker, warn_once, gem5::X86ISA::TlbEntry::writable, and gem5::BaseMMU::Write.

Referenced by translateAtomic(), and translateTiming().

◆ translateAtomic()

|

overridevirtual |

Implements gem5::BaseTLB.

Definition at line 508 of file tlb.cc.

References gem5::X86ISA::mode, gem5::BaseMMU::Read, and translate().

◆ translateFunctional()

|

overridevirtual |

Reimplemented from gem5::BaseTLB.

Definition at line 238 of file tlb.cc.

References gem5::FullSystem, gem5::ThreadContext::getProcessPtr(), gem5::X86ISA::mode, panic_if, gem5::Process::pTable, gem5::EmulationPageTable::translate(), and translateFunctional().

Referenced by translateFunctional().

◆ translateInt()

|

protected |

Definition at line 210 of file tlb.cc.

References gem5::bits(), configAddress, DPRINTF, gem5::X86ISA::IntAddrPrefixCPUID, gem5::X86ISA::IntAddrPrefixIO, gem5::X86ISA::IntAddrPrefixMask, gem5::X86ISA::IntAddrPrefixMSR, gem5::X86ISA::mask, gem5::mbits(), gem5::X86ISA::msrAddrToIndex(), gem5::NoFault, panic, gem5::X86ISA::misc_reg::PciConfigAddress, gem5::X86ISA::PhysAddrPrefixIO, gem5::X86ISA::PhysAddrPrefixPciConfig, gem5::ThreadContext::readMiscRegNoEffect(), gem5::Request::STRICT_ORDER, TLB(), gem5::Request::UNCACHEABLE, and gem5::MipsISA::vaddr.

Referenced by translate().

◆ translateTiming()

|

overridevirtual |

Implements gem5::BaseTLB.

Definition at line 557 of file tlb.cc.

References gem5::BaseMMU::Translation::finish(), gem5::BaseMMU::Translation::markDelayed(), gem5::X86ISA::mode, gem5::BaseMMU::Read, and translate().

◆ unserialize()

|

overridevirtual |

Unserialize an object.

Read an object's state from the current checkpoint section.

- Parameters

-

cp Checkpoint state

Reimplemented from gem5::SimObject.

Definition at line 207 of file tlb.cc.

References gem5::csprintf(), gem5::ArmISA::i, size, unserialize(), and UNSERIALIZE_SCALAR.

Referenced by unserialize().

Friends And Related Symbol Documentation

◆ Walker

|

friend |

Member Data Documentation

◆ configAddress

|

protected |

Definition at line 67 of file tlb.hh.

Referenced by setConfigAddress(), TLB(), and translateInt().

◆ freeList

|

protected |

Definition at line 105 of file tlb.hh.

Referenced by demapPage(), flushAll(), flushNonGlobal(), insert(), and TLB().

◆ lruSeq

|

protected |

Definition at line 108 of file tlb.hh.

Referenced by evictLRU(), nextSeq(), and TLB().

◆ m5opRange

|

protected |

Definition at line 110 of file tlb.hh.

Referenced by finalizePhysical(), and TLB().

◆ size

|

protected |

Definition at line 101 of file tlb.hh.

Referenced by evictLRU(), flushAll(), flushNonGlobal(), serialize(), TLB(), and unserialize().

◆ stats

|

protected |

Referenced by TLB(), and translate().

◆ tlb

|

protected |

Definition at line 103 of file tlb.hh.

Referenced by evictLRU(), flushAll(), flushNonGlobal(), and TLB().

◆ trie

|

protected |

Definition at line 107 of file tlb.hh.

Referenced by demapPage(), flushAll(), flushNonGlobal(), insert(), and lookup().

◆ walker

|

protected |

Definition at line 89 of file tlb.hh.

Referenced by getTableWalkerPort(), getWalker(), TLB(), and translate().

The documentation for this class was generated from the following files:

Generated on Sat Oct 18 2025 08:07:53 for gem5 by doxygen 1.14.0