#include <dyn_inst.hh>

Classes | |

| struct | Arrays |

Public Types | |

| typedef std::list< DynInstPtr >::iterator | ListIt |

Public Member Functions | |

| DynInst (const Arrays &arrays, const StaticInstPtr &staticInst, const StaticInstPtr ¯oop, InstSeqNum seq_num, CPU *cpu) | |

| BaseDynInst constructor given a binary instruction. | |

| DynInst (const Arrays &arrays, const StaticInstPtr &staticInst, const StaticInstPtr ¯oop, const PCStateBase &pc, const PCStateBase &pred_pc, InstSeqNum seq_num, CPU *cpu) | |

| DynInst (const Arrays &arrays, const StaticInstPtr &_staticInst, const StaticInstPtr &_macroop) | |

| BaseDynInst constructor given a static inst pointer. | |

| ~DynInst () | |

| Fault | execute () |

| Executes the instruction. | |

| Fault | initiateAcc () |

| Initiates the access. | |

| Fault | completeAcc (PacketPtr pkt) |

| Completes the access. | |

| BaseCPU * | getCpuPtr () |

| size_t | numSrcs () const |

| size_t | numDests () const |

| const RegId & | flattenedDestIdx (int idx) const |

| void | flattenedDestIdx (int idx, const RegId ®_id) |

| PhysRegIdPtr | renamedDestIdx (int idx) const |

| void | renamedDestIdx (int idx, PhysRegIdPtr phys_reg_id) |

| PhysRegIdPtr | prevDestIdx (int idx) const |

| void | prevDestIdx (int idx, PhysRegIdPtr phys_reg_id) |

| PhysRegIdPtr | renamedSrcIdx (int idx) const |

| void | renamedSrcIdx (int idx, PhysRegIdPtr phys_reg_id) |

| bool | readySrcIdx (int idx) const |

| void | readySrcIdx (int idx, bool ready) |

| void | recordResult (bool f) |

| Records changes to result? | |

| bool | effAddrValid () const |

| Is the effective virtual address valid. | |

| void | effAddrValid (bool b) |

| bool | memOpDone () const |

| Whether or not the memory operation is done. | |

| void | memOpDone (bool f) |

| bool | notAnInst () const |

| void | setNotAnInst () |

| void | demapPage (Addr vaddr, uint64_t asn) override |

| Invalidate a page in the DTLB and ITLB. | |

| Fault | initiateMemRead (Addr addr, unsigned size, Request::Flags flags, const std::vector< bool > &byte_enable) override |

| Fault | initiateMemMgmtCmd (Request::Flags flags) override |

| Initiate a memory management command with no valid address. | |

| Fault | writeMem (uint8_t *data, unsigned size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable) override |

| Fault | initiateMemAMO (Addr addr, unsigned size, Request::Flags flags, AtomicOpFunctorPtr amo_op) override |

| bool | translationStarted () const |

| True if the DTB address translation has started. | |

| void | translationStarted (bool f) |

| bool | translationCompleted () const |

| True if the DTB address translation has completed. | |

| void | translationCompleted (bool f) |

| bool | possibleLoadViolation () const |

| True if this address was found to match a previous load and they issued out of order. | |

| void | possibleLoadViolation (bool f) |

| bool | hitExternalSnoop () const |

| True if the address hit a external snoop while sitting in the LSQ. | |

| void | hitExternalSnoop (bool f) |

| bool | isTranslationDelayed () const |

| Returns true if the DTB address translation is being delayed due to a hw page table walk. | |

| void | renameDestReg (int idx, PhysRegIdPtr renamed_dest, PhysRegIdPtr previous_rename) |

| Renames a destination register to a physical register. | |

| void | renameSrcReg (int idx, PhysRegIdPtr renamed_src) |

| Renames a source logical register to the physical register which has/will produce that logical register's result. | |

| void | dump () |

| Dumps out contents of this BaseDynInst. | |

| void | dump (std::string &outstring) |

| Dumps out contents of this BaseDynInst into given string. | |

| int | cpuId () const |

| Read this CPU's ID. | |

| uint32_t | socketId () const |

| Read this CPU's Socket ID. | |

| RequestorID | requestorId () const |

| Read this CPU's data requestor ID. | |

| ContextID | contextId () const |

| Read this context's system-wide ID. | |

| Fault | getFault () const |

| Returns the fault type. | |

| Fault & | getFault () |

| TODO: This I added for the LSQRequest side to be able to modify the fault. | |

| bool | doneTargCalc () |

| Checks whether or not this instruction has had its branch target calculated yet. | |

| void | setPredTarg (const PCStateBase &pred_pc) |

| Set the predicted target of this current instruction. | |

| const PCStateBase & | readPredTarg () |

| bool | readPredTaken () |

| Returns whether the instruction was predicted taken or not. | |

| void | setPredTaken (bool predicted_taken) |

| bool | mispredicted () |

| Returns whether the instruction mispredicted. | |

| bool | isNop () const |

| bool | isMemRef () const |

| bool | isLoad () const |

| bool | isStore () const |

| bool | isAtomic () const |

| bool | isStoreConditional () const |

| bool | isInstPrefetch () const |

| bool | isDataPrefetch () const |

| bool | isInteger () const |

| bool | isFloating () const |

| bool | isVector () const |

| bool | isControl () const |

| bool | isCall () const |

| bool | isReturn () const |

| bool | isDirectCtrl () const |

| bool | isIndirectCtrl () const |

| bool | isCondCtrl () const |

| bool | isUncondCtrl () const |

| bool | isSerializing () const |

| bool | isSerializeBefore () const |

| bool | isSerializeAfter () const |

| bool | isSquashAfter () const |

| bool | isFullMemBarrier () const |

| bool | isReadBarrier () const |

| bool | isWriteBarrier () const |

| bool | isNonSpeculative () const |

| bool | isQuiesce () const |

| bool | isUnverifiable () const |

| bool | isSyscall () const |

| bool | isMacroop () const |

| bool | isMicroop () const |

| bool | isDelayedCommit () const |

| bool | isLastMicroop () const |

| bool | isFirstMicroop () const |

| bool | isHtmStart () const |

| bool | isHtmStop () const |

| bool | isHtmCancel () const |

| bool | isHtmCmd () const |

| uint64_t | getHtmTransactionUid () const override |

| uint64_t | newHtmTransactionUid () const override |

| bool | inHtmTransactionalState () const override |

| uint64_t | getHtmTransactionalDepth () const override |

| void | setHtmTransactionalState (uint64_t htm_uid, uint64_t htm_depth) |

| void | clearHtmTransactionalState () |

| void | setSerializeBefore () |

| Temporarily sets this instruction as a serialize before instruction. | |

| void | clearSerializeBefore () |

| Clears the serializeBefore part of this instruction. | |

| bool | isTempSerializeBefore () |

| Checks if this serializeBefore is only temporarily set. | |

| void | setSerializeAfter () |

| Temporarily sets this instruction as a serialize after instruction. | |

| void | clearSerializeAfter () |

| Clears the serializeAfter part of this instruction. | |

| bool | isTempSerializeAfter () |

| Checks if this serializeAfter is only temporarily set. | |

| void | setSerializeHandled () |

| Sets the serialization part of this instruction as handled. | |

| bool | isSerializeHandled () |

| Checks if the serialization part of this instruction has been handled. | |

| OpClass | opClass () const |

| Returns the opclass of this instruction. | |

| std::unique_ptr< PCStateBase > | branchTarget () const |

| Returns the branch target address. | |

| size_t | numSrcRegs () const |

| Returns the number of source registers. | |

| size_t | numDestRegs () const |

| Returns the number of destination registers. | |

| size_t | numDestRegs (RegClassType type) const |

| const RegId & | destRegIdx (int i) const |

| Returns the logical register index of the i'th destination register. | |

| const RegId & | srcRegIdx (int i) const |

| Returns the logical register index of the i'th source register. | |

| uint8_t | resultSize () |

| Return the size of the instResult queue. | |

| InstResult | popResult (InstResult dflt=InstResult()) |

| Pops a result off the instResult queue. | |

| void | markSrcRegReady () |

| Records that one of the source registers is ready. | |

| void | markSrcRegReady (RegIndex src_idx) |

| Marks a specific register as ready. | |

| void | setCompleted () |

| Sets this instruction as completed. | |

| bool | isCompleted () const |

| Returns whether or not this instruction is completed. | |

| void | setResultReady () |

| Marks the result as ready. | |

| bool | isResultReady () const |

| Returns whether or not the result is ready. | |

| void | setCanIssue () |

| Sets this instruction as ready to issue. | |

| bool | readyToIssue () const |

| Returns whether or not this instruction is ready to issue. | |

| void | clearCanIssue () |

| Clears this instruction being able to issue. | |

| void | setIssued () |

| Sets this instruction as issued from the IQ. | |

| bool | isIssued () const |

| Returns whether or not this instruction has issued. | |

| void | clearIssued () |

| Clears this instruction as being issued. | |

| void | setExecuted () |

| Sets this instruction as executed. | |

| bool | isExecuted () const |

| Returns whether or not this instruction has executed. | |

| void | setCanCommit () |

| Sets this instruction as ready to commit. | |

| void | clearCanCommit () |

| Clears this instruction as being ready to commit. | |

| bool | readyToCommit () const |

| Returns whether or not this instruction is ready to commit. | |

| void | setAtCommit () |

| bool | isAtCommit () |

| void | setCommitted () |

| Sets this instruction as committed. | |

| bool | isCommitted () const |

| Returns whether or not this instruction is committed. | |

| void | setSquashed () |

| Sets this instruction as squashed. | |

| bool | isSquashed () const |

| Returns whether or not this instruction is squashed. | |

| void | setInIQ () |

| Sets this instruction as a entry the IQ. | |

| void | clearInIQ () |

| Sets this instruction as a entry the IQ. | |

| bool | isInIQ () const |

| Returns whether or not this instruction has issued. | |

| void | setSquashedInIQ () |

| Sets this instruction as squashed in the IQ. | |

| bool | isSquashedInIQ () const |

| Returns whether or not this instruction is squashed in the IQ. | |

| void | setInLSQ () |

| Sets this instruction as a entry the LSQ. | |

| void | removeInLSQ () |

| Sets this instruction as a entry the LSQ. | |

| bool | isInLSQ () const |

| Returns whether or not this instruction is in the LSQ. | |

| void | setSquashedInLSQ () |

| Sets this instruction as squashed in the LSQ. | |

| bool | isSquashedInLSQ () const |

| Returns whether or not this instruction is squashed in the LSQ. | |

| void | setInROB () |

| Sets this instruction as a entry the ROB. | |

| void | clearInROB () |

| Sets this instruction as a entry the ROB. | |

| bool | isInROB () const |

| Returns whether or not this instruction is in the ROB. | |

| void | setSquashedInROB () |

| Sets this instruction as squashed in the ROB. | |

| bool | isSquashedInROB () const |

| Returns whether or not this instruction is squashed in the ROB. | |

| void | setNoCapableFU () |

| Mark this instruction as having attempted to execute but CPU did not have a capable functional unit. | |

| bool | noCapableFU () const |

| Returns whether or not this instruction attempted to execute and found not capable FU. | |

| bool | isPinnedRegsRenamed () const |

| Returns whether pinned registers are renamed. | |

| void | setPinnedRegsRenamed () |

| Sets the destination registers as renamed. | |

| bool | isPinnedRegsWritten () const |

| Returns whether destination registers are written. | |

| void | setPinnedRegsWritten () |

| Sets destination registers as written. | |

| bool | isPinnedRegsSquashDone () const |

| Return whether dest registers' pinning status updated after squash. | |

| void | setPinnedRegsSquashDone () |

| Sets dest registers' status updated after squash. | |

| const PCStateBase & | pcState () const override |

| Read the PC state of this instruction. | |

| void | pcState (const PCStateBase &val) override |

| Set the PC state of this instruction. | |

| bool | readPredicate () const override |

| void | setPredicate (bool val) override |

| bool | readMemAccPredicate () const override |

| void | setMemAccPredicate (bool val) override |

| void | setTid (ThreadID tid) |

| Sets the thread id. | |

| void | setThreadState (ThreadState *state) |

| Sets the pointer to the thread state. | |

| gem5::ThreadContext * | tcBase () const override |

| Returns the thread context. | |

| bool | strictlyOrdered () const |

| Is this instruction's memory access strictly ordered? | |

| void | strictlyOrdered (bool so) |

| bool | hasRequest () const |

| Has this instruction generated a memory request. | |

| void | setRequest () |

| Assert this instruction has generated a memory request. | |

| ListIt & | getInstListIt () |

| Returns iterator to this instruction in the list of all insts. | |

| void | setInstListIt (ListIt _instListIt) |

| Sets iterator for this instruction in the list of all insts. | |

| unsigned int | readStCondFailures () const override |

| Returns the number of consecutive store conditional failures. | |

| void | setStCondFailures (unsigned int sc_failures) override |

| Sets the number of consecutive store conditional failures. | |

| void | armMonitor (Addr address) override |

| bool | mwait (PacketPtr pkt) override |

| void | mwaitAtomic (gem5::ThreadContext *tc) override |

| AddressMonitor * | getAddrMonitor () override |

| RegVal | readMiscReg (int misc_reg) override |

| Reads a misc. | |

| void | setMiscReg (int misc_reg, RegVal val) override |

| Sets a misc. | |

| RegVal | readMiscRegOperand (const StaticInst *si, int idx) override |

| Reads a misc. | |

| void | setMiscRegOperand (const StaticInst *si, int idx, RegVal val) override |

| Sets a misc. | |

| void | updateMiscRegs () |

| Called at the commit stage to update the misc. | |

| void | forwardOldRegs () |

| void | trap (const Fault &fault) |

| Traps to handle specified fault. | |

| RegVal | getRegOperand (const StaticInst *si, int idx) override |

| void | getRegOperand (const StaticInst *si, int idx, void *val) override |

| void * | getWritableRegOperand (const StaticInst *si, int idx) override |

| void | setRegOperand (const StaticInst *si, int idx, RegVal val) override |

| void | setRegOperand (const StaticInst *si, int idx, const void *val) override |

| template<typename T> | |

| void | setResult (const RegClass ®_class, T &&t) |

| Pushes a result onto the instResult queue. | |

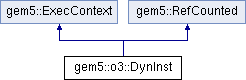

| Public Member Functions inherited from gem5::ExecContext | |

| virtual Fault | readMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Perform an atomic memory read operation. | |

| virtual Fault | initiateMemRead (Addr addr, unsigned int size, Request::Flags flags, const std::vector< bool > &byte_enable) |

| Initiate a timing memory read operation. | |

| virtual Fault | writeMem (uint8_t *data, unsigned int size, Addr addr, Request::Flags flags, uint64_t *res, const std::vector< bool > &byte_enable)=0 |

| For atomic-mode contexts, perform an atomic memory write operation. | |

| virtual Fault | amoMem (Addr addr, uint8_t *data, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For atomic-mode contexts, perform an atomic AMO (a.k.a., Atomic Read-Modify-Write Memory Operation) | |

| virtual Fault | initiateMemAMO (Addr addr, unsigned int size, Request::Flags flags, AtomicOpFunctorPtr amo_op) |

| For timing-mode contexts, initiate an atomic AMO (atomic read-modify-write memory operation) | |

| Public Member Functions inherited from gem5::RefCounted | |

| RefCounted () | |

| We initialize the reference count to zero and the first object to take ownership of it must increment it to one. | |

| virtual | ~RefCounted () |

| We make the destructor virtual because we're likely to have virtual functions on reference counted objects. | |

| void | incref () const |

| Increment the reference count. | |

| void | decref () const |

| Decrement the reference count and destroy the object if all references are gone. | |

Static Public Member Functions | |

| static void * | operator new (size_t count, Arrays &arrays) |

| static void | operator delete (void *ptr) |

Public Attributes | |

| InstSeqNum | seqNum = 0 |

| The sequence number of the instruction. | |

| const StaticInstPtr | staticInst |

| The StaticInst used by this BaseDynInst. | |

| CPU * | cpu = nullptr |

| Pointer to the Impl's CPU object. | |

| ThreadState * | thread = nullptr |

| Pointer to the thread state. | |

| Fault | fault = NoFault |

| The kind of fault this instruction has generated. | |

| trace::InstRecord * | traceData = nullptr |

| InstRecord that tracks this instructions. | |

| ThreadID | threadNumber = 0 |

| The thread this instruction is from. | |

| ListIt | instListIt |

| Iterator pointing to this BaseDynInst in the list of all insts. | |

| std::unique_ptr< PCStateBase > | predPC |

| Predicted PC state after this instruction. | |

| const StaticInstPtr | macroop |

| The Macroop if one exists. | |

| uint8_t | readyRegs = 0 |

| How many source registers are ready. | |

| Addr | effAddr = 0 |

| The effective virtual address (lds & stores only). | |

| Addr | physEffAddr = 0 |

| The effective physical address. | |

| unsigned | memReqFlags = 0 |

| The memory request flags (from translation). | |

| unsigned | effSize |

| The size of the request. | |

| uint8_t * | memData = nullptr |

| Pointer to the data for the memory access. | |

| ssize_t | lqIdx = -1 |

| Load queue index. | |

| LSQUnit::LQIterator | lqIt |

| ssize_t | sqIdx = -1 |

| Store queue index. | |

| LSQUnit::SQIterator | sqIt |

| LSQ::LSQRequest * | savedRequest |

| Saved memory request (needed when the DTB address translation is delayed due to a hw page table walk). | |

| RequestPtr | reqToVerify |

| Tick | firstIssue = -1 |

| Tick | lastWakeDependents = -1 |

Protected Types | |

| enum | Status { IqEntry , RobEntry , LsqEntry , Completed , ResultReady , CanIssue , Issued , Executed , CanCommit , AtCommit , Committed , Squashed , SquashedInIQ , SquashedInLSQ , SquashedInROB , PinnedRegsRenamed , PinnedRegsWritten , PinnedRegsSquashDone , RecoverInst , BlockingInst , ThreadsyncWait , SerializeBefore , SerializeAfter , SerializeHandled , NumStatus } |

| enum | Flags { NotAnInst , TranslationStarted , TranslationCompleted , PossibleLoadViolation , HitExternalSnoop , EffAddrValid , RecordResult , Predicate , MemAccPredicate , PredTaken , IsStrictlyOrdered , ReqMade , MemOpDone , HtmFromTransaction , NoCapableFU , MaxFlags } |

Protected Attributes | |

| std::queue< InstResult > | instResult |

| The result of the instruction; assumes an instruction can have many destination registers. | |

| std::unique_ptr< PCStateBase > | pc |

| PC state for this instruction. | |

| std::vector< RegVal > | _destMiscRegVal |

| Values to be written to the destination misc. | |

| std::vector< short > | _destMiscRegIdx |

| Indexes of the destination misc. | |

| size_t | _numSrcs |

| size_t | _numDests |

| RegId * | _flatDestIdx |

| PhysRegIdPtr * | _destIdx |

| PhysRegIdPtr * | _prevDestIdx |

| PhysRegIdPtr * | _srcIdx |

| uint8_t * | _readySrcIdx |

Private Member Functions | |

| DynInst (const StaticInstPtr &staticInst, const StaticInstPtr ¯oop, InstSeqNum seq_num, CPU *cpu) | |

Private Attributes | |

| std::bitset< MaxFlags > | instFlags |

| std::bitset< NumStatus > | status |

| The status of this BaseDynInst. | |

| uint64_t | htmUid = -1 |

| uint64_t | htmDepth = 0 |

Detailed Description

Definition at line 75 of file dyn_inst.hh.

Member Typedef Documentation

◆ ListIt

| typedef std::list<DynInstPtr>::iterator gem5::o3::DynInst::ListIt |

Definition at line 83 of file dyn_inst.hh.

Member Enumeration Documentation

◆ Flags

|

protected |

Definition at line 174 of file dyn_inst.hh.

◆ Status

|

protected |

| Enumerator | |

|---|---|

| IqEntry | |

| RobEntry | Instruction is in the IQ. |

| LsqEntry | Instruction is in the ROB. |

| Completed | Instruction is in the LSQ. |

| ResultReady | Instruction has completed. |

| CanIssue | Instruction has its result. |

| Issued | Instruction can issue and execute. |

| Executed | Instruction has issued. |

| CanCommit | Instruction has executed. |

| AtCommit | Instruction can commit. |

| Committed | Instruction has reached commit. |

| Squashed | Instruction has committed. |

| SquashedInIQ | Instruction is squashed. |

| SquashedInLSQ | Instruction is squashed in the IQ. |

| SquashedInROB | Instruction is squashed in the LSQ. |

| PinnedRegsRenamed | Instruction is squashed in the ROB. |

| PinnedRegsWritten | Pinned registers are renamed. |

| PinnedRegsSquashDone | Pinned registers are written back. |

| RecoverInst | Regs pinning status updated after squash. |

| BlockingInst | Is a recover instruction. |

| ThreadsyncWait | Is a blocking instruction. |

| SerializeBefore | Is a thread synchronization instruction. |

| SerializeAfter | Needs to serialize on instructions ahead of it. |

| SerializeHandled | Needs to serialize instructions behind it. |

| NumStatus | Serialization has been handled. |

Definition at line 144 of file dyn_inst.hh.

Constructor & Destructor Documentation

◆ DynInst() [1/4]

|

private |

References cpu, macroop, and staticInst.

Referenced by DynInst(), DynInst(), DynInst(), and ~DynInst().

◆ DynInst() [2/4]

| gem5::o3::DynInst::DynInst | ( | const Arrays & | arrays, |

| const StaticInstPtr & | staticInst, | ||

| const StaticInstPtr & | macroop, | ||

| InstSeqNum | seq_num, | ||

| CPU * | cpu ) |

BaseDynInst constructor given a binary instruction.

Definition at line 56 of file dyn_inst.cc.

References _destIdx, _flatDestIdx, _numDests, _numSrcs, _prevDestIdx, _readySrcIdx, _srcIdx, cpu, DPRINTF, DynInst(), instFlags, macroop, MemAccPredicate, numDests(), numSrcs(), Predicate, prevDestIdx(), readySrcIdx(), RecordResult, seqNum, staticInst, and status.

◆ DynInst() [3/4]

| gem5::o3::DynInst::DynInst | ( | const Arrays & | arrays, |

| const StaticInstPtr & | staticInst, | ||

| const StaticInstPtr & | macroop, | ||

| const PCStateBase & | pc, | ||

| const PCStateBase & | pred_pc, | ||

| InstSeqNum | seq_num, | ||

| CPU * | cpu ) |

Definition at line 95 of file dyn_inst.cc.

References DynInst(), pc, predPC, and gem5::ArmISA::set.

◆ DynInst() [4/4]

| gem5::o3::DynInst::DynInst | ( | const Arrays & | arrays, |

| const StaticInstPtr & | _staticInst, | ||

| const StaticInstPtr & | _macroop ) |

BaseDynInst constructor given a static inst pointer.

Definition at line 104 of file dyn_inst.cc.

References DynInst().

◆ ~DynInst()

| gem5::o3::DynInst::~DynInst | ( | ) |

Definition at line 199 of file dyn_inst.cc.

References _destIdx, _flatDestIdx, _numDests, _numSrcs, _prevDestIdx, _readySrcIdx, _srcIdx, cpu, DPRINTF, DPRINTFR, DynInst(), fault, gem5::ArmISA::i, memData, gem5::NoFault, pcState(), seqNum, staticInst, traceData, and gem5::X86ISA::val.

Member Function Documentation

◆ armMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 972 of file dyn_inst.hh.

References cpu, and threadNumber.

◆ branchTarget()

|

inline |

Returns the branch target address.

Definition at line 674 of file dyn_inst.hh.

References pc, and staticInst.

◆ clearCanCommit()

|

inline |

Clears this instruction as being ready to commit.

Definition at line 772 of file dyn_inst.hh.

◆ clearCanIssue()

|

inline |

Clears this instruction being able to issue.

Definition at line 751 of file dyn_inst.hh.

◆ clearHtmTransactionalState()

|

inline |

Definition at line 628 of file dyn_inst.hh.

References DPRINTF, getHtmTransactionUid(), htmDepth, HtmFromTransaction, htmUid, inHtmTransactionalState(), and instFlags.

◆ clearInIQ()

|

inline |

Sets this instruction as a entry the IQ.

Definition at line 799 of file dyn_inst.hh.

◆ clearInROB()

|

inline |

Sets this instruction as a entry the ROB.

Definition at line 835 of file dyn_inst.hh.

◆ clearIssued()

|

inline |

Clears this instruction as being issued.

Definition at line 760 of file dyn_inst.hh.

◆ clearSerializeAfter()

|

inline |

Clears the serializeAfter part of this instruction.

Definition at line 654 of file dyn_inst.hh.

References SerializeAfter, and status.

◆ clearSerializeBefore()

|

inline |

Clears the serializeBefore part of this instruction.

Definition at line 645 of file dyn_inst.hh.

References SerializeBefore, and status.

◆ completeAcc()

Completes the access.

Only valid for memory operations.

Definition at line 382 of file dyn_inst.cc.

References cpu, fault, isStoreConditional(), gem5::Packet::req, reqToVerify, staticInst, thread, and traceData.

◆ contextId()

|

inline |

◆ cpuId()

|

inline |

◆ demapPage()

|

inlineoverridevirtual |

Invalidate a page in the DTLB and ITLB.

Implements gem5::ExecContext.

Definition at line 394 of file dyn_inst.hh.

References cpu, and gem5::MipsISA::vaddr.

◆ destRegIdx()

|

inline |

Returns the logical register index of the i'th destination register.

Definition at line 692 of file dyn_inst.hh.

References gem5::ArmISA::i, and staticInst.

◆ doneTargCalc()

|

inline |

Checks whether or not this instruction has had its branch target calculated yet.

For now it is not utilized and is hacked to be always false.

- Todo

- : Actually use this instruction.

Definition at line 513 of file dyn_inst.hh.

◆ dump() [1/2]

| void gem5::o3::DynInst::dump | ( | ) |

Dumps out contents of this BaseDynInst.

Definition at line 287 of file dyn_inst.cc.

References gem5::cprintf(), pc, staticInst, and threadNumber.

◆ dump() [2/2]

| void gem5::o3::DynInst::dump | ( | std::string & | outstring | ) |

Dumps out contents of this BaseDynInst into given string.

Definition at line 295 of file dyn_inst.cc.

References pc, gem5::ArmISA::s, staticInst, and threadNumber.

◆ effAddrValid() [1/2]

|

inline |

Is the effective virtual address valid.

Definition at line 376 of file dyn_inst.hh.

References EffAddrValid, and instFlags.

◆ effAddrValid() [2/2]

|

inline |

Definition at line 377 of file dyn_inst.hh.

References gem5::ArmISA::b, EffAddrValid, and instFlags.

◆ execute()

| Fault gem5::o3::DynInst::execute | ( | ) |

Executes the instruction.

Definition at line 348 of file dyn_inst.cc.

References fault, staticInst, thread, and traceData.

◆ flattenedDestIdx() [1/2]

|

inline |

Definition at line 248 of file dyn_inst.hh.

References _flatDestIdx.

◆ flattenedDestIdx() [2/2]

|

inline |

Definition at line 256 of file dyn_inst.hh.

References _flatDestIdx.

◆ forwardOldRegs()

|

inline |

Definition at line 1087 of file dyn_inst.hh.

References cpu, gem5::RegId::isRenameable(), numDestRegs(), prevDestIdx(), gem5::RegClass::regBytes(), gem5::RegId::regClass(), setRegOperand(), staticInst, threadNumber, and gem5::X86ISA::val.

◆ getAddrMonitor()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 987 of file dyn_inst.hh.

References cpu, and threadNumber.

◆ getCpuPtr()

|

inline |

Definition at line 132 of file dyn_inst.hh.

References cpu.

◆ getFault() [1/2]

|

inline |

TODO: This I added for the LSQRequest side to be able to modify the fault.

There should be a better mechanism in place.

Definition at line 506 of file dyn_inst.hh.

References fault.

◆ getFault() [2/2]

|

inline |

◆ getHtmTransactionalDepth()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 611 of file dyn_inst.hh.

References htmDepth, and inHtmTransactionalState().

◆ getHtmTransactionUid()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 591 of file dyn_inst.hh.

References HtmFromTransaction, htmUid, and instFlags.

Referenced by clearHtmTransactionalState().

◆ getInstListIt()

|

inline |

Returns iterator to this instruction in the list of all insts.

Definition at line 949 of file dyn_inst.hh.

References instListIt.

◆ getRegOperand() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1127 of file dyn_inst.hh.

References cpu, gem5::InvalidRegClass, gem5::X86ISA::reg, renamedSrcIdx(), gem5::ArmISA::si, and threadNumber.

◆ getRegOperand() [2/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1136 of file dyn_inst.hh.

References cpu, gem5::InvalidRegClass, gem5::X86ISA::reg, renamedSrcIdx(), gem5::ArmISA::si, threadNumber, and gem5::X86ISA::val.

◆ getWritableRegOperand()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1145 of file dyn_inst.hh.

References cpu, renamedDestIdx(), gem5::ArmISA::si, and threadNumber.

◆ hasRequest()

|

inline |

Has this instruction generated a memory request.

Definition at line 944 of file dyn_inst.hh.

◆ hitExternalSnoop() [1/2]

|

inline |

True if the address hit a external snoop while sitting in the LSQ.

If this is true and a older instruction sees it, this instruction must reexecute

Definition at line 443 of file dyn_inst.hh.

References HitExternalSnoop, and instFlags.

◆ hitExternalSnoop() [2/2]

|

inline |

Definition at line 444 of file dyn_inst.hh.

References gem5::ArmISA::f, HitExternalSnoop, and instFlags.

◆ inHtmTransactionalState()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 605 of file dyn_inst.hh.

References HtmFromTransaction, and instFlags.

Referenced by clearHtmTransactionalState(), and getHtmTransactionalDepth().

◆ initiateAcc()

| Fault gem5::o3::DynInst::initiateAcc | ( | ) |

Initiates the access.

Only valid for memory operations.

Definition at line 365 of file dyn_inst.cc.

References fault, staticInst, thread, and traceData.

◆ initiateMemAMO()

|

override |

Definition at line 444 of file dyn_inst.cc.

References gem5::X86ISA::addr, and cpu.

◆ initiateMemMgmtCmd()

|

overridevirtual |

Initiate a memory management command with no valid address.

Currently, these instructions need to bypass squashing in the O3 model Examples include HTM commands and TLBI commands. e.g. tell Ruby we're starting/stopping a HTM transaction, or tell Ruby to issue a TLBI operation

Implements gem5::ExecContext.

Definition at line 422 of file dyn_inst.cc.

References cpu.

◆ initiateMemRead()

|

override |

Definition at line 411 of file dyn_inst.cc.

References gem5::X86ISA::addr, and cpu.

◆ isAtCommit()

|

inline |

Definition at line 779 of file dyn_inst.hh.

◆ isAtomic()

|

inline |

Definition at line 545 of file dyn_inst.hh.

References staticInst.

◆ isCall()

|

inline |

Definition at line 554 of file dyn_inst.hh.

References staticInst.

◆ isCommitted()

|

inline |

Returns whether or not this instruction is committed.

Definition at line 785 of file dyn_inst.hh.

◆ isCompleted()

|

inline |

Returns whether or not this instruction is completed.

Definition at line 736 of file dyn_inst.hh.

◆ isCondCtrl()

|

inline |

Definition at line 558 of file dyn_inst.hh.

References staticInst.

◆ isControl()

|

inline |

Definition at line 553 of file dyn_inst.hh.

References staticInst.

◆ isDataPrefetch()

|

inline |

Definition at line 549 of file dyn_inst.hh.

References staticInst.

◆ isDelayedCommit()

|

inline |

Definition at line 581 of file dyn_inst.hh.

References staticInst.

◆ isDirectCtrl()

|

inline |

Definition at line 556 of file dyn_inst.hh.

References staticInst.

◆ isExecuted()

|

inline |

Returns whether or not this instruction has executed.

Definition at line 766 of file dyn_inst.hh.

◆ isFirstMicroop()

|

inline |

Definition at line 583 of file dyn_inst.hh.

References staticInst.

◆ isFloating()

|

inline |

Definition at line 551 of file dyn_inst.hh.

References staticInst.

◆ isFullMemBarrier()

|

inline |

Definition at line 572 of file dyn_inst.hh.

References staticInst.

◆ isHtmCancel()

|

inline |

Definition at line 587 of file dyn_inst.hh.

References staticInst.

◆ isHtmCmd()

|

inline |

Definition at line 588 of file dyn_inst.hh.

References staticInst.

◆ isHtmStart()

|

inline |

Definition at line 585 of file dyn_inst.hh.

References staticInst.

◆ isHtmStop()

|

inline |

Definition at line 586 of file dyn_inst.hh.

References staticInst.

◆ isIndirectCtrl()

|

inline |

Definition at line 557 of file dyn_inst.hh.

References staticInst.

◆ isInIQ()

|

inline |

Returns whether or not this instruction has issued.

Definition at line 802 of file dyn_inst.hh.

◆ isInLSQ()

|

inline |

Returns whether or not this instruction is in the LSQ.

Definition at line 820 of file dyn_inst.hh.

◆ isInROB()

|

inline |

Returns whether or not this instruction is in the ROB.

Definition at line 838 of file dyn_inst.hh.

◆ isInstPrefetch()

|

inline |

Definition at line 548 of file dyn_inst.hh.

References staticInst.

◆ isInteger()

|

inline |

Definition at line 550 of file dyn_inst.hh.

References staticInst.

◆ isIssued()

|

inline |

Returns whether or not this instruction has issued.

Definition at line 757 of file dyn_inst.hh.

◆ isLastMicroop()

|

inline |

Definition at line 582 of file dyn_inst.hh.

References staticInst.

◆ isLoad()

|

inline |

Definition at line 543 of file dyn_inst.hh.

References staticInst.

◆ isMacroop()

|

inline |

Definition at line 579 of file dyn_inst.hh.

References staticInst.

◆ isMemRef()

|

inline |

Definition at line 542 of file dyn_inst.hh.

References staticInst.

◆ isMicroop()

|

inline |

Definition at line 580 of file dyn_inst.hh.

References staticInst.

◆ isNonSpeculative()

|

inline |

Definition at line 575 of file dyn_inst.hh.

References staticInst.

◆ isNop()

|

inline |

Definition at line 541 of file dyn_inst.hh.

References staticInst.

◆ isPinnedRegsRenamed()

|

inline |

Returns whether pinned registers are renamed.

Definition at line 857 of file dyn_inst.hh.

References PinnedRegsRenamed, and status.

Referenced by setSquashed().

◆ isPinnedRegsSquashDone()

|

inline |

Return whether dest registers' pinning status updated after squash.

Definition at line 882 of file dyn_inst.hh.

References PinnedRegsSquashDone, and status.

Referenced by setSquashed().

◆ isPinnedRegsWritten()

|

inline |

Returns whether destination registers are written.

Definition at line 869 of file dyn_inst.hh.

References PinnedRegsWritten, and status.

Referenced by setSquashed().

◆ isQuiesce()

|

inline |

Definition at line 576 of file dyn_inst.hh.

References staticInst.

◆ isReadBarrier()

|

inline |

Definition at line 573 of file dyn_inst.hh.

References staticInst.

◆ isResultReady()

|

inline |

Returns whether or not the result is ready.

Definition at line 742 of file dyn_inst.hh.

References ResultReady, and status.

◆ isReturn()

|

inline |

Definition at line 555 of file dyn_inst.hh.

References staticInst.

◆ isSerializeAfter()

|

inline |

Definition at line 567 of file dyn_inst.hh.

References SerializeAfter, staticInst, and status.

◆ isSerializeBefore()

|

inline |

Definition at line 562 of file dyn_inst.hh.

References SerializeBefore, staticInst, and status.

◆ isSerializeHandled()

|

inline |

Checks if the serialization part of this instruction has been handled.

This does not apply to the temporary serializing state; it only applies to this instruction's own permanent serializing state.

Definition at line 667 of file dyn_inst.hh.

References SerializeHandled, and status.

◆ isSerializing()

|

inline |

Definition at line 560 of file dyn_inst.hh.

References staticInst.

◆ isSquashAfter()

|

inline |

Definition at line 571 of file dyn_inst.hh.

References staticInst.

◆ isSquashed()

|

inline |

Returns whether or not this instruction is squashed.

Definition at line 791 of file dyn_inst.hh.

◆ isSquashedInIQ()

|

inline |

Returns whether or not this instruction is squashed in the IQ.

Definition at line 808 of file dyn_inst.hh.

References SquashedInIQ, and status.

◆ isSquashedInLSQ()

|

inline |

Returns whether or not this instruction is squashed in the LSQ.

Definition at line 826 of file dyn_inst.hh.

References SquashedInLSQ, and status.

◆ isSquashedInROB()

|

inline |

Returns whether or not this instruction is squashed in the ROB.

Definition at line 844 of file dyn_inst.hh.

References SquashedInROB, and status.

◆ isStore()

|

inline |

Definition at line 544 of file dyn_inst.hh.

References staticInst.

◆ isStoreConditional()

|

inline |

◆ isSyscall()

|

inline |

Definition at line 578 of file dyn_inst.hh.

References staticInst.

◆ isTempSerializeAfter()

|

inline |

Checks if this serializeAfter is only temporarily set.

Definition at line 657 of file dyn_inst.hh.

References SerializeAfter, and status.

◆ isTempSerializeBefore()

|

inline |

Checks if this serializeBefore is only temporarily set.

Definition at line 648 of file dyn_inst.hh.

References SerializeBefore, and status.

◆ isTranslationDelayed()

|

inline |

Returns true if the DTB address translation is being delayed due to a hw page table walk.

Definition at line 451 of file dyn_inst.hh.

References translationCompleted(), and translationStarted().

◆ isUncondCtrl()

|

inline |

Definition at line 559 of file dyn_inst.hh.

References staticInst.

◆ isUnverifiable()

|

inline |

Definition at line 577 of file dyn_inst.hh.

References staticInst.

◆ isVector()

|

inline |

Definition at line 552 of file dyn_inst.hh.

References staticInst.

◆ isWriteBarrier()

|

inline |

Definition at line 574 of file dyn_inst.hh.

References staticInst.

◆ markSrcRegReady() [1/2]

| void gem5::o3::DynInst::markSrcRegReady | ( | ) |

Records that one of the source registers is ready.

Definition at line 305 of file dyn_inst.cc.

References DPRINTF, numSrcRegs(), readyRegs, readyToIssue(), seqNum, and setCanIssue().

Referenced by markSrcRegReady().

◆ markSrcRegReady() [2/2]

| void gem5::o3::DynInst::markSrcRegReady | ( | RegIndex | src_idx | ) |

Marks a specific register as ready.

Definition at line 315 of file dyn_inst.cc.

References markSrcRegReady(), and readySrcIdx().

◆ memOpDone() [1/2]

|

inline |

Whether or not the memory operation is done.

Definition at line 380 of file dyn_inst.hh.

◆ memOpDone() [2/2]

|

inline |

Definition at line 381 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and MemOpDone.

◆ mispredicted()

|

inline |

Returns whether the instruction mispredicted.

Definition at line 531 of file dyn_inst.hh.

References pc, predPC, and staticInst.

◆ mwait()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 977 of file dyn_inst.hh.

References cpu, and threadNumber.

◆ mwaitAtomic()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 982 of file dyn_inst.hh.

References cpu, and threadNumber.

◆ newHtmTransactionUid()

|

inlineoverridevirtual |

◆ noCapableFU()

|

inline |

Returns whether or not this instruction attempted to execute and found not capable FU.

Definition at line 854 of file dyn_inst.hh.

References instFlags, and NoCapableFU.

◆ notAnInst()

|

inline |

Definition at line 383 of file dyn_inst.hh.

◆ numDestRegs() [1/2]

|

inline |

Returns the number of destination registers.

Definition at line 683 of file dyn_inst.hh.

References numDests().

Referenced by forwardOldRegs(), and setSquashed().

◆ numDestRegs() [2/2]

|

inline |

Definition at line 686 of file dyn_inst.hh.

References staticInst.

◆ numDests()

|

inline |

Definition at line 243 of file dyn_inst.hh.

References _numDests.

Referenced by DynInst(), and numDestRegs().

◆ numSrcRegs()

|

inline |

Returns the number of source registers.

Definition at line 680 of file dyn_inst.hh.

References numSrcs().

Referenced by markSrcRegReady().

◆ numSrcs()

|

inline |

Definition at line 242 of file dyn_inst.hh.

References _numSrcs.

Referenced by DynInst(), and numSrcRegs().

◆ opClass()

|

inline |

Returns the opclass of this instruction.

Definition at line 670 of file dyn_inst.hh.

References staticInst.

◆ operator delete()

|

static |

Definition at line 194 of file dyn_inst.cc.

◆ operator new()

|

static |

Definition at line 137 of file dyn_inst.cc.

References gem5::RefCounted::count, and gem5::roundUp().

◆ pcState() [1/2]

|

inlineoverridevirtual |

Read the PC state of this instruction.

Implements gem5::ExecContext.

Definition at line 897 of file dyn_inst.hh.

References pc.

Referenced by gem5::o3::DependencyGraph< DynInstPtr >::dump(), and ~DynInst().

◆ pcState() [2/2]

|

inlineoverridevirtual |

Set the PC state of this instruction.

Implements gem5::ExecContext.

Definition at line 903 of file dyn_inst.hh.

References pc, gem5::ArmISA::set, and gem5::X86ISA::val.

◆ popResult()

|

inline |

Pops a result off the instResult queue.

If the result stack is empty, return the default value.

Definition at line 704 of file dyn_inst.hh.

References instResult, and gem5::ArmISA::t.

◆ possibleLoadViolation() [1/2]

|

inline |

True if this address was found to match a previous load and they issued out of order.

If that happend, then it's only a problem if an incoming snoop invalidate modifies the line, in which case we need to squash. If nothing modified the line the order doesn't matter.

Definition at line 429 of file dyn_inst.hh.

References instFlags, and PossibleLoadViolation.

◆ possibleLoadViolation() [2/2]

|

inline |

Definition at line 434 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and PossibleLoadViolation.

◆ prevDestIdx() [1/2]

|

inline |

Definition at line 279 of file dyn_inst.hh.

References _prevDestIdx.

Referenced by DynInst(), forwardOldRegs(), and renameDestReg().

◆ prevDestIdx() [2/2]

|

inline |

Definition at line 286 of file dyn_inst.hh.

References _prevDestIdx.

◆ readMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 918 of file dyn_inst.hh.

References instFlags, and MemAccPredicate.

◆ readMiscReg()

|

inlineoverridevirtual |

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements gem5::ExecContext.

Definition at line 1020 of file dyn_inst.hh.

References cpu, and threadNumber.

◆ readMiscRegOperand()

|

inlineoverridevirtual |

Reads a misc.

register, including any side-effects the read might have as defined by the architecture.

Implements gem5::ExecContext.

Definition at line 1050 of file dyn_inst.hh.

References cpu, gem5::MiscRegClass, gem5::X86ISA::reg, gem5::ArmISA::si, and threadNumber.

◆ readPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 905 of file dyn_inst.hh.

◆ readPredTaken()

|

inline |

Returns whether the instruction was predicted taken or not.

Definition at line 521 of file dyn_inst.hh.

◆ readPredTarg()

|

inline |

Definition at line 518 of file dyn_inst.hh.

References predPC.

◆ readStCondFailures()

|

inlineoverridevirtual |

Returns the number of consecutive store conditional failures.

Implements gem5::ExecContext.

Definition at line 957 of file dyn_inst.hh.

References thread.

◆ readySrcIdx() [1/2]

|

inline |

Definition at line 305 of file dyn_inst.hh.

References _readySrcIdx, and gem5::bits().

Referenced by DynInst(), and markSrcRegReady().

◆ readySrcIdx() [2/2]

|

inline |

Definition at line 312 of file dyn_inst.hh.

References _readySrcIdx, and gem5::replaceBits().

◆ readyToCommit()

|

inline |

Returns whether or not this instruction is ready to commit.

Definition at line 775 of file dyn_inst.hh.

◆ readyToIssue()

|

inline |

Returns whether or not this instruction is ready to issue.

Definition at line 748 of file dyn_inst.hh.

References CanIssue, and status.

Referenced by markSrcRegReady().

◆ recordResult()

|

inline |

Records changes to result?

Definition at line 373 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and RecordResult.

◆ removeInLSQ()

|

inline |

Sets this instruction as a entry the LSQ.

Definition at line 817 of file dyn_inst.hh.

◆ renamedDestIdx() [1/2]

|

inline |

Definition at line 264 of file dyn_inst.hh.

References _destIdx.

Referenced by getWritableRegOperand(), renameDestReg(), setRegOperand(), setRegOperand(), and setSquashed().

◆ renamedDestIdx() [2/2]

|

inline |

Definition at line 271 of file dyn_inst.hh.

References _destIdx.

◆ renameDestReg()

|

inline |

Renames a destination register to a physical register.

Also records the previous physical register that the logical register mapped to.

Definition at line 465 of file dyn_inst.hh.

References gem5::PhysRegId::isPinned(), prevDestIdx(), renamedDestIdx(), and setPinnedRegsRenamed().

◆ renamedSrcIdx() [1/2]

|

inline |

Definition at line 293 of file dyn_inst.hh.

References _srcIdx.

Referenced by getRegOperand(), getRegOperand(), and renameSrcReg().

◆ renamedSrcIdx() [2/2]

|

inline |

Definition at line 299 of file dyn_inst.hh.

References _srcIdx.

◆ renameSrcReg()

|

inline |

Renames a source logical register to the physical register which has/will produce that logical register's result.

- Todo

- : add in whether or not the source register is ready.

Definition at line 479 of file dyn_inst.hh.

References renamedSrcIdx().

◆ requestorId()

|

inline |

◆ resultSize()

|

inline |

Return the size of the instResult queue.

Definition at line 698 of file dyn_inst.hh.

References instResult.

◆ setAtCommit()

|

inline |

Definition at line 777 of file dyn_inst.hh.

◆ setCanCommit()

|

inline |

Sets this instruction as ready to commit.

Definition at line 769 of file dyn_inst.hh.

◆ setCanIssue()

|

inline |

Sets this instruction as ready to issue.

Definition at line 745 of file dyn_inst.hh.

References CanIssue, and status.

Referenced by markSrcRegReady().

◆ setCommitted()

|

inline |

Sets this instruction as committed.

Definition at line 782 of file dyn_inst.hh.

◆ setCompleted()

|

inline |

Sets this instruction as completed.

Definition at line 733 of file dyn_inst.hh.

◆ setExecuted()

|

inline |

Sets this instruction as executed.

Definition at line 763 of file dyn_inst.hh.

◆ setHtmTransactionalState()

|

inline |

Definition at line 620 of file dyn_inst.hh.

References htmDepth, HtmFromTransaction, htmUid, and instFlags.

◆ setInIQ()

|

inline |

Sets this instruction as a entry the IQ.

Definition at line 796 of file dyn_inst.hh.

◆ setInLSQ()

|

inline |

Sets this instruction as a entry the LSQ.

Definition at line 814 of file dyn_inst.hh.

◆ setInROB()

|

inline |

Sets this instruction as a entry the ROB.

Definition at line 832 of file dyn_inst.hh.

◆ setInstListIt()

|

inline |

Sets iterator for this instruction in the list of all insts.

Definition at line 952 of file dyn_inst.hh.

References instListIt.

◆ setIssued()

|

inline |

Sets this instruction as issued from the IQ.

Definition at line 754 of file dyn_inst.hh.

◆ setMemAccPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 924 of file dyn_inst.hh.

References instFlags, MemAccPredicate, and gem5::X86ISA::val.

◆ setMiscReg()

|

inlineoverridevirtual |

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Writes to misc. registers are recorded and deferred until the commit stage, when updateMiscRegs() is called. First, check if the misc reg has been written before and update its value to be committed instead of making a new entry. If not, make a new entry and record the write.

Implements gem5::ExecContext.

Definition at line 1029 of file dyn_inst.hh.

References _destMiscRegIdx, _destMiscRegVal, and gem5::X86ISA::val.

Referenced by setMiscRegOperand().

◆ setMiscRegOperand()

|

inlineoverridevirtual |

Sets a misc.

register, including any side-effects the write might have as defined by the architecture.

Implements gem5::ExecContext.

Definition at line 1061 of file dyn_inst.hh.

References gem5::MiscRegClass, gem5::X86ISA::reg, setMiscReg(), gem5::ArmISA::si, and gem5::X86ISA::val.

◆ setNoCapableFU()

|

inline |

Mark this instruction as having attempted to execute but CPU did not have a capable functional unit.

Definition at line 849 of file dyn_inst.hh.

References instFlags, and NoCapableFU.

◆ setNotAnInst()

|

inline |

Definition at line 384 of file dyn_inst.hh.

◆ setPinnedRegsRenamed()

|

inline |

Sets the destination registers as renamed.

Definition at line 861 of file dyn_inst.hh.

References PinnedRegsRenamed, PinnedRegsSquashDone, PinnedRegsWritten, and status.

Referenced by renameDestReg().

◆ setPinnedRegsSquashDone()

|

inline |

Sets dest registers' status updated after squash.

Definition at line 889 of file dyn_inst.hh.

References PinnedRegsSquashDone, and status.

Referenced by setSquashed().

◆ setPinnedRegsWritten()

|

inline |

Sets destination registers as written.

Definition at line 873 of file dyn_inst.hh.

References PinnedRegsRenamed, PinnedRegsSquashDone, PinnedRegsWritten, and status.

◆ setPredicate()

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 908 of file dyn_inst.hh.

References instFlags, Predicate, traceData, and gem5::X86ISA::val.

◆ setPredTaken()

|

inline |

Definition at line 524 of file dyn_inst.hh.

◆ setPredTarg()

|

inline |

Set the predicted target of this current instruction.

Definition at line 516 of file dyn_inst.hh.

References predPC, and gem5::ArmISA::set.

◆ setRegOperand() [1/2]

|

inlineoverridevirtual |

Implements gem5::ExecContext.

Definition at line 1164 of file dyn_inst.hh.

References cpu, gem5::InvalidRegClass, gem5::X86ISA::reg, renamedDestIdx(), setResult(), gem5::ArmISA::si, threadNumber, and gem5::X86ISA::val.

◆ setRegOperand() [2/2]

|

inlineoverridevirtual |

- Todo

- : Make results into arrays so they can handle multiple dest registers.

Implements gem5::ExecContext.

Definition at line 1154 of file dyn_inst.hh.

References cpu, gem5::InvalidRegClass, gem5::X86ISA::reg, renamedDestIdx(), setResult(), gem5::ArmISA::si, threadNumber, and gem5::X86ISA::val.

Referenced by forwardOldRegs().

◆ setRequest()

|

inline |

Assert this instruction has generated a memory request.

Definition at line 946 of file dyn_inst.hh.

◆ setResult()

|

inline |

Pushes a result onto the instResult queue.

Definition at line 718 of file dyn_inst.hh.

References instFlags, instResult, RecordResult, and gem5::ArmISA::t.

Referenced by setRegOperand(), and setRegOperand().

◆ setResultReady()

|

inline |

Marks the result as ready.

Definition at line 739 of file dyn_inst.hh.

References ResultReady, and status.

◆ setSerializeAfter()

|

inline |

Temporarily sets this instruction as a serialize after instruction.

Definition at line 651 of file dyn_inst.hh.

References SerializeAfter, and status.

◆ setSerializeBefore()

|

inline |

Temporarily sets this instruction as a serialize before instruction.

Definition at line 642 of file dyn_inst.hh.

References SerializeBefore, and status.

◆ setSerializeHandled()

|

inline |

Sets the serialization part of this instruction as handled.

Definition at line 660 of file dyn_inst.hh.

References SerializeHandled, and status.

◆ setSquashed()

| void gem5::o3::DynInst::setSquashed | ( | ) |

Sets this instruction as squashed.

Definition at line 323 of file dyn_inst.cc.

References gem5::PhysRegId::incrNumPinnedWrites(), gem5::PhysRegId::incrNumPinnedWritesToComplete(), gem5::PhysRegId::isPinned(), isPinnedRegsRenamed(), isPinnedRegsSquashDone(), isPinnedRegsWritten(), numDestRegs(), renamedDestIdx(), setPinnedRegsSquashDone(), Squashed, and status.

◆ setSquashedInIQ()

|

inline |

Sets this instruction as squashed in the IQ.

Definition at line 805 of file dyn_inst.hh.

References Squashed, SquashedInIQ, and status.

◆ setSquashedInLSQ()

|

inline |

Sets this instruction as squashed in the LSQ.

Definition at line 823 of file dyn_inst.hh.

References Squashed, SquashedInLSQ, and status.

◆ setSquashedInROB()

|

inline |

Sets this instruction as squashed in the ROB.

Definition at line 841 of file dyn_inst.hh.

References SquashedInROB, and status.

◆ setStCondFailures()

|

inlineoverridevirtual |

Sets the number of consecutive store conditional failures.

Implements gem5::ExecContext.

Definition at line 964 of file dyn_inst.hh.

References thread.

◆ setThreadState()

|

inline |

Sets the pointer to the thread state.

Definition at line 933 of file dyn_inst.hh.

References thread.

◆ setTid()

|

inline |

◆ socketId()

|

inline |

◆ srcRegIdx()

|

inline |

Returns the logical register index of the i'th source register.

Definition at line 695 of file dyn_inst.hh.

References gem5::ArmISA::i, and staticInst.

◆ strictlyOrdered() [1/2]

|

inline |

Is this instruction's memory access strictly ordered?

Definition at line 940 of file dyn_inst.hh.

References instFlags, and IsStrictlyOrdered.

◆ strictlyOrdered() [2/2]

|

inline |

Definition at line 941 of file dyn_inst.hh.

References instFlags, IsStrictlyOrdered, and gem5::PowerISA::so.

◆ tcBase()

|

inlineoverridevirtual |

Returns the thread context.

Implements gem5::ExecContext.

Definition at line 936 of file dyn_inst.hh.

References thread.

◆ translationCompleted() [1/2]

|

inline |

True if the DTB address translation has completed.

Definition at line 417 of file dyn_inst.hh.

References instFlags, and TranslationCompleted.

Referenced by isTranslationDelayed().

◆ translationCompleted() [2/2]

|

inline |

Definition at line 421 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and TranslationCompleted.

◆ translationStarted() [1/2]

|

inline |

True if the DTB address translation has started.

Definition at line 412 of file dyn_inst.hh.

References instFlags, and TranslationStarted.

Referenced by isTranslationDelayed().

◆ translationStarted() [2/2]

|

inline |

Definition at line 413 of file dyn_inst.hh.

References gem5::ArmISA::f, instFlags, and TranslationStarted.

◆ trap()

| void gem5::o3::DynInst::trap | ( | const Fault & | fault | ) |

Traps to handle specified fault.

Definition at line 405 of file dyn_inst.cc.

References cpu, fault, staticInst, and threadNumber.

◆ updateMiscRegs()

|

inline |

Called at the commit stage to update the misc.

registers.

Definition at line 1070 of file dyn_inst.hh.

References _destMiscRegIdx, _destMiscRegVal, cpu, gem5::ArmISA::i, thread, and threadNumber.

◆ writeMem()

|

override |

Definition at line 432 of file dyn_inst.cc.

References gem5::X86ISA::addr, cpu, and data.

Member Data Documentation

◆ _destIdx

|

protected |

Definition at line 229 of file dyn_inst.hh.

Referenced by DynInst(), renamedDestIdx(), renamedDestIdx(), and ~DynInst().

◆ _destMiscRegIdx

|

protected |

Indexes of the destination misc.

registers. They are needed to defer the write accesses to the misc. registers until the commit stage, when the instruction is out of its speculative state.

Definition at line 218 of file dyn_inst.hh.

Referenced by setMiscReg(), and updateMiscRegs().

◆ _destMiscRegVal

|

protected |

Values to be written to the destination misc.

registers.

Definition at line 212 of file dyn_inst.hh.

Referenced by setMiscReg(), and updateMiscRegs().

◆ _flatDestIdx

|

protected |

Definition at line 225 of file dyn_inst.hh.

Referenced by DynInst(), flattenedDestIdx(), flattenedDestIdx(), and ~DynInst().

◆ _numDests

|

protected |

Definition at line 221 of file dyn_inst.hh.

Referenced by DynInst(), numDests(), and ~DynInst().

◆ _numSrcs

|

protected |

Definition at line 220 of file dyn_inst.hh.

Referenced by DynInst(), numSrcs(), and ~DynInst().

◆ _prevDestIdx

|

protected |

Definition at line 233 of file dyn_inst.hh.

Referenced by DynInst(), prevDestIdx(), prevDestIdx(), and ~DynInst().

◆ _readySrcIdx

|

protected |

Definition at line 239 of file dyn_inst.hh.

Referenced by DynInst(), readySrcIdx(), readySrcIdx(), and ~DynInst().

◆ _srcIdx

|

protected |

Definition at line 236 of file dyn_inst.hh.

Referenced by DynInst(), renamedSrcIdx(), renamedSrcIdx(), and ~DynInst().

◆ cpu

| CPU* gem5::o3::DynInst::cpu = nullptr |

Pointer to the Impl's CPU object.

Definition at line 130 of file dyn_inst.hh.

Referenced by armMonitor(), completeAcc(), cpuId(), demapPage(), DynInst(), DynInst(), forwardOldRegs(), getAddrMonitor(), getCpuPtr(), getRegOperand(), getRegOperand(), getWritableRegOperand(), initiateMemAMO(), initiateMemMgmtCmd(), initiateMemRead(), mwait(), mwaitAtomic(), readMiscReg(), readMiscRegOperand(), requestorId(), setRegOperand(), setRegOperand(), socketId(), trap(), updateMiscRegs(), writeMem(), and ~DynInst().

◆ effAddr

| Addr gem5::o3::DynInst::effAddr = 0 |

The effective virtual address (lds & stores only).

Definition at line 337 of file dyn_inst.hh.

◆ effSize

| unsigned gem5::o3::DynInst::effSize |

The size of the request.

Definition at line 346 of file dyn_inst.hh.

◆ fault

The kind of fault this instruction has generated.

Definition at line 138 of file dyn_inst.hh.

Referenced by completeAcc(), execute(), getFault(), getFault(), initiateAcc(), trap(), and ~DynInst().

◆ firstIssue

| Tick gem5::o3::DynInst::firstIssue = -1 |

Definition at line 1013 of file dyn_inst.hh.

◆ htmDepth

|

private |

Definition at line 995 of file dyn_inst.hh.

Referenced by clearHtmTransactionalState(), getHtmTransactionalDepth(), and setHtmTransactionalState().

◆ htmUid

|

private |

Definition at line 994 of file dyn_inst.hh.

Referenced by clearHtmTransactionalState(), getHtmTransactionUid(), and setHtmTransactionalState().

◆ instFlags

|

private |

Definition at line 197 of file dyn_inst.hh.

Referenced by clearHtmTransactionalState(), DynInst(), effAddrValid(), effAddrValid(), getHtmTransactionUid(), hasRequest(), hitExternalSnoop(), hitExternalSnoop(), inHtmTransactionalState(), memOpDone(), memOpDone(), noCapableFU(), notAnInst(), possibleLoadViolation(), possibleLoadViolation(), readMemAccPredicate(), readPredicate(), readPredTaken(), recordResult(), setHtmTransactionalState(), setMemAccPredicate(), setNoCapableFU(), setNotAnInst(), setPredicate(), setPredTaken(), setRequest(), setResult(), strictlyOrdered(), strictlyOrdered(), translationCompleted(), translationCompleted(), translationStarted(), and translationStarted().

◆ instListIt

| ListIt gem5::o3::DynInst::instListIt |

Iterator pointing to this BaseDynInst in the list of all insts.

Definition at line 322 of file dyn_inst.hh.

Referenced by getInstListIt(), and setInstListIt().

◆ instResult

|

protected |

The result of the instruction; assumes an instruction can have many destination registers.

Definition at line 206 of file dyn_inst.hh.

Referenced by popResult(), resultSize(), and setResult().

◆ lastWakeDependents

| Tick gem5::o3::DynInst::lastWakeDependents = -1 |

Definition at line 1014 of file dyn_inst.hh.

◆ lqIdx

| ssize_t gem5::o3::DynInst::lqIdx = -1 |

Load queue index.

Definition at line 352 of file dyn_inst.hh.

◆ lqIt

| LSQUnit::LQIterator gem5::o3::DynInst::lqIt |

Definition at line 353 of file dyn_inst.hh.

◆ macroop

| const StaticInstPtr gem5::o3::DynInst::macroop |

The Macroop if one exists.

Definition at line 329 of file dyn_inst.hh.

◆ memData

| uint8_t* gem5::o3::DynInst::memData = nullptr |

Pointer to the data for the memory access.

Definition at line 349 of file dyn_inst.hh.

Referenced by ~DynInst().

◆ memReqFlags

| unsigned gem5::o3::DynInst::memReqFlags = 0 |

The memory request flags (from translation).

Definition at line 343 of file dyn_inst.hh.

◆ pc

|

protected |

PC state for this instruction.

Definition at line 209 of file dyn_inst.hh.

Referenced by branchTarget(), dump(), dump(), DynInst(), mispredicted(), pcState(), and pcState().

◆ physEffAddr

| Addr gem5::o3::DynInst::physEffAddr = 0 |

The effective physical address.

Definition at line 340 of file dyn_inst.hh.

◆ predPC

| std::unique_ptr<PCStateBase> gem5::o3::DynInst::predPC |

Predicted PC state after this instruction.

Definition at line 326 of file dyn_inst.hh.

Referenced by DynInst(), mispredicted(), readPredTarg(), and setPredTarg().

◆ readyRegs

| uint8_t gem5::o3::DynInst::readyRegs = 0 |

How many source registers are ready.

Definition at line 332 of file dyn_inst.hh.

Referenced by markSrcRegReady().

◆ reqToVerify

| RequestPtr gem5::o3::DynInst::reqToVerify |

Definition at line 369 of file dyn_inst.hh.

Referenced by completeAcc().

◆ savedRequest

| LSQ::LSQRequest* gem5::o3::DynInst::savedRequest |

Saved memory request (needed when the DTB address translation is delayed due to a hw page table walk).

Definition at line 365 of file dyn_inst.hh.

◆ seqNum

| InstSeqNum gem5::o3::DynInst::seqNum = 0 |

The sequence number of the instruction.

Definition at line 124 of file dyn_inst.hh.

Referenced by gem5::o3::DependencyGraph< DynInstPtr >::dump(), DynInst(), markSrcRegReady(), and ~DynInst().

◆ sqIdx

| ssize_t gem5::o3::DynInst::sqIdx = -1 |

Store queue index.

Definition at line 356 of file dyn_inst.hh.

◆ sqIt

| LSQUnit::SQIterator gem5::o3::DynInst::sqIt |

Definition at line 357 of file dyn_inst.hh.

◆ staticInst

| const StaticInstPtr gem5::o3::DynInst::staticInst |

The StaticInst used by this BaseDynInst.

Definition at line 127 of file dyn_inst.hh.

Referenced by branchTarget(), completeAcc(), destRegIdx(), dump(), dump(), DynInst(), DynInst(), execute(), forwardOldRegs(), initiateAcc(), isAtomic(), isCall(), isCondCtrl(), isControl(), isDataPrefetch(), isDelayedCommit(), isDirectCtrl(), isFirstMicroop(), isFloating(), isFullMemBarrier(), isHtmCancel(), isHtmCmd(), isHtmStart(), isHtmStop(), isIndirectCtrl(), isInstPrefetch(), isInteger(), isLastMicroop(), isLoad(), isMacroop(), isMemRef(), isMicroop(), isNonSpeculative(), isNop(), isQuiesce(), isReadBarrier(), isReturn(), isSerializeAfter(), isSerializeBefore(), isSerializing(), isSquashAfter(), isStore(), isStoreConditional(), isSyscall(), isUncondCtrl(), isUnverifiable(), isVector(), isWriteBarrier(), mispredicted(), numDestRegs(), opClass(), srcRegIdx(), trap(), and ~DynInst().

◆ status

|

private |

The status of this BaseDynInst.

Several bits can be set.

Definition at line 200 of file dyn_inst.hh.

Referenced by clearCanCommit(), clearCanIssue(), clearInIQ(), clearInROB(), clearIssued(), clearSerializeAfter(), clearSerializeBefore(), DynInst(), isAtCommit(), isCommitted(), isCompleted(), isExecuted(), isInIQ(), isInLSQ(), isInROB(), isIssued(), isPinnedRegsRenamed(), isPinnedRegsSquashDone(), isPinnedRegsWritten(), isResultReady(), isSerializeAfter(), isSerializeBefore(), isSerializeHandled(), isSquashed(), isSquashedInIQ(), isSquashedInLSQ(), isSquashedInROB(), isTempSerializeAfter(), isTempSerializeBefore(), readyToCommit(), readyToIssue(), removeInLSQ(), setAtCommit(), setCanCommit(), setCanIssue(), setCommitted(), setCompleted(), setExecuted(), setInIQ(), setInLSQ(), setInROB(), setIssued(), setPinnedRegsRenamed(), setPinnedRegsSquashDone(), setPinnedRegsWritten(), setResultReady(), setSerializeAfter(), setSerializeBefore(), setSerializeHandled(), setSquashed(), setSquashedInIQ(), setSquashedInLSQ(), and setSquashedInROB().

◆ thread

| ThreadState* gem5::o3::DynInst::thread = nullptr |

Pointer to the thread state.

Definition at line 135 of file dyn_inst.hh.

Referenced by completeAcc(), contextId(), execute(), initiateAcc(), readStCondFailures(), setStCondFailures(), setThreadState(), tcBase(), and updateMiscRegs().

◆ threadNumber

| ThreadID gem5::o3::DynInst::threadNumber = 0 |

The thread this instruction is from.

Definition at line 319 of file dyn_inst.hh.

Referenced by armMonitor(), dump(), dump(), forwardOldRegs(), getAddrMonitor(), getRegOperand(), getRegOperand(), getWritableRegOperand(), mwait(), mwaitAtomic(), readMiscReg(), readMiscRegOperand(), setRegOperand(), setRegOperand(), setTid(), trap(), and updateMiscRegs().

◆ traceData

| trace::InstRecord* gem5::o3::DynInst::traceData = nullptr |

InstRecord that tracks this instructions.

Definition at line 141 of file dyn_inst.hh.

Referenced by completeAcc(), execute(), initiateAcc(), setPredicate(), and ~DynInst().

The documentation for this class was generated from the following files:

- cpu/o3/dyn_inst.hh

- cpu/o3/dyn_inst.cc

Generated on Sat Oct 18 2025 08:07:00 for gem5 by doxygen 1.14.0